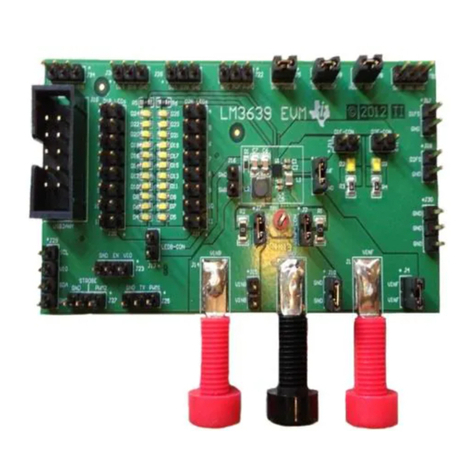

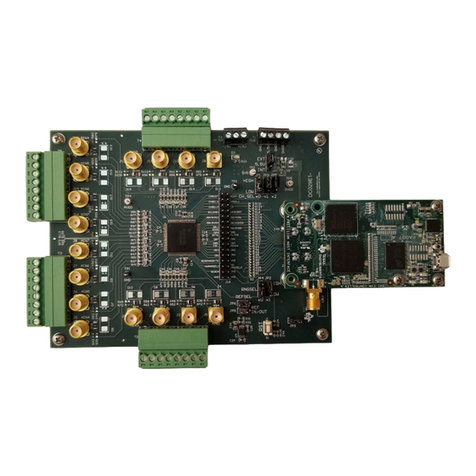

2.3 Header Information

As outlined in Table 2-1, header J1 provides connections to the low-voltage side of the SENSE capacitors

(corresponding to the SENSE pins of the IC), the low-voltage side of the inject capacitor, the IC bias power

supply (VDD and GND pins), which is set between 8 V and 16 V, and a remote enable (EN) signal.

Table 2-1. J1 Header Connections

POSITION(1) LABEL DESCRIPTION

1 EN Enable input – leave open or tie high to enable the IC; tie to GND to disable

2 VDD Supply voltage connection – connect to a 12-V bias power supply referenced to GND(2)

3 INJ Inject output – connect to a Y-rated inject capacitor, CINJ

4 GND Ground – connect to the chassis ground of the system with a direct, low-inductance connection

5 S1 Sense 1 input – connect to a Y-rated sense capacitor, CSEN1

6 S2 Sense 2 input – connect to a Y-rated sense capacitor, CSEN2

(1) Pin positions of header J1 are designated right to left when viewed from the top side of the EVM.

(2) Working at an ESD-protected workstation, verify that any wrist straps, bootstraps or mats are connected and referencing the user to

Earth ground before power is applied to the EVM.

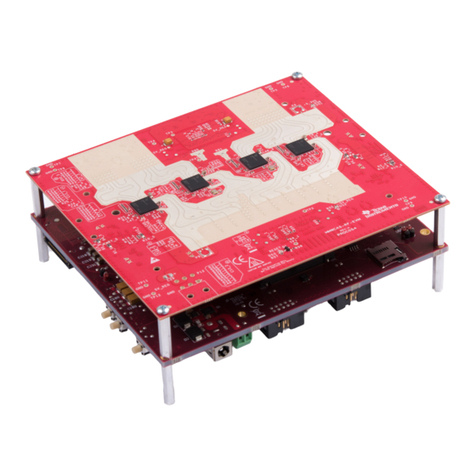

A 6-pin right-angle header, part number TSW-106-08-G-S-RA, connects the EVM to a corresponding female

receptacle, part number SSW-106-01-G-S, which mounts on the EMI filter board that carries the passive filter

components – the CM chokes, X-capacitors and Y-capacitors – as well as the sense and inject capacitors. The

EVM includes both the header and the receptacle, manufactured by Samtec. See Section 4.2.

2.4 EVM Performance Validation

1. Connect the EVM to the filter board (see receptacle J2 in Figure 2-3).

2. Apply a VDD bias supply voltage of 8 V to 16 V (nominal 12 V, with ripple voltage less than 20 mV

peak-to-peak) between the VDD and GND terminals of J1.

3. Measure the voltage at the INJ pin of the TPSF12C1 (pin 13) with respect to GND; a DC voltage of VVDD/2

and have no AC perturbations that indicate instability. The VDD current consumption must be approximately

12 mA. If the INJ pin voltage is oscillating, modify the damping network components on the EVM to achieve

stability.

4. The user must perform low-voltage testing prior to connecting the high-voltage power stage. To provide a

CM stimulus, connect a 5-V peak-to-peak square-wave source from a function generator as shown in Figure

2-4. Set the signal frequency to the switching freqeuncy of the power stage and choose a duty cycle that

creates all the spectral harmonics (aside: 50% duty cycle eliminates the even harmonics, 33.3% removes

the triple-n harmonics, and so forth). A 1-nF capacitor in series with the signal source emulates a practical

CM noise source impedance.

• Using this CM excitation source, verify the dynamic voltage range of the TPSF12C1 INJ pin. Ensure that

the INJ pin voltage relative to GND operates in a window between 2.5 V and VVDD – 2 V.

5. Connect a LISN on each input power line and measure the EMI with AEF disabled (EN tied to GND) to

benchmark the existing passive filter. Short the low-voltage (bottom) terminal of the inject capacitor to GND

when AEF is disabled by tying the INJ terminal on J1 to GND. This emulates the Y-capacitor connection in

an equivalent passive filter design.

6. Remove the pulldown short on the inject capacitor and enable the AEF circuit by allowing EN to float high.

Repeat the EMI measurement, thus quantifying the EMI reduction with AEF.

7. In a similar fashion, perform a comparison of filter insertion loss or attenuation performance using a network

analyzer. For a true insertion loss measurement with 50-Ω source and load impedances, replace the LISN by

a 50-Ω load tied from L or N to GND.

8. Using high-voltage safety precautions, connect the switching power stage as shown in Figure 2-2. Turn the

regulator ON and, similar to step 4, verify that the IC's INJ pin voltage is not getting clipped. To improve the

dynamic range of the INJ voltage, increase one or more of the following:

• Regulator-side Y-capacitance, CY3 and CY4

• Inject capacitance, CINJ

• VDD supply voltage, VVDD

9. Measure the EMI with AEF enabled and disabled, similar to the procedure outlined in steps 5 and 6.

10. Turn the regulator OFF. Wait for all high-voltage capacitors to fully discharge.

www.ti.com Hardware

SLVUCK7A – NOVEMBER 2022 – REVISED JULY 2023

Submit Document Feedback

Active EMI Filter Evaluation Module for Single-Phase AC Power Systems 7

Copyright © 2023 Texas Instruments Incorporated