Table of Contents

1 High-Density EVM Description.............................................................................................................................................. 4

1.1 Typical Applications............................................................................................................................................................4

2 Test Setup and Procedure......................................................................................................................................................5

2.1 EVM Connections.............................................................................................................................................................. 5

2.2 EVM Setup......................................................................................................................................................................... 6

2.3 Test Equipment.................................................................................................................................................................. 7

2.4 Recommended Test Setup.................................................................................................................................................7

2.5 Test Procedure................................................................................................................................................................... 7

3 Test Data and Performance Curves...................................................................................................................................... 8

3.1 Efficiency and Load Regulation Performance.................................................................................................................... 8

3.2 Waveforms....................................................................................................................................................................... 10

3.3 Bode Plot..........................................................................................................................................................................11

3.4 EMI Performance............................................................................................................................................................. 13

4 EVM Documentation.............................................................................................................................................................14

4.1 Schematic........................................................................................................................................................................ 14

4.2 Bill of Materials.................................................................................................................................................................15

4.3 PCB Layout...................................................................................................................................................................... 17

4.4 Multi-Layer Stackup......................................................................................................................................................... 19

5 Device and Documentation Support...................................................................................................................................20

5.1 Device Support.................................................................................................................................................................20

5.2 Documentation Support................................................................................................................................................... 20

6 Revision History................................................................................................................................................................... 21

List of Figures

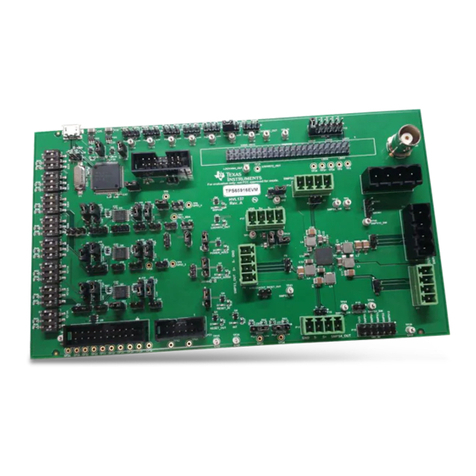

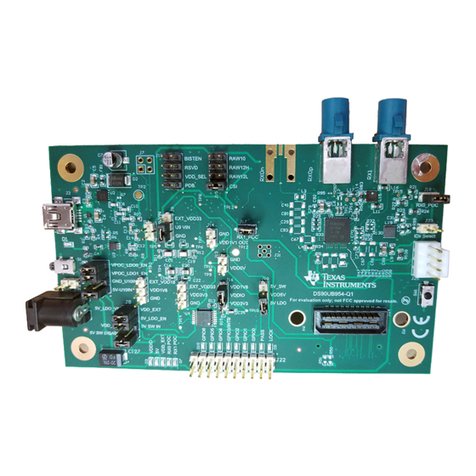

Figure 2-1. EVM Test Setup.........................................................................................................................................................5

Figure 3-1. Efficiency, VOUT = 5 V, FSW = 1 MHz, FPWM Mode.................................................................................................. 8

Figure 3-2. Efficiency, VOUT = 5 V, FSW = 1 MHz, AUTO Mode................................................................................................... 8

Figure 3-3. Load Regulation, VOUT = 5 V, FSW = 1 MHz, FPWM Mode.......................................................................................8

Figure 3-4. Load Regulation, VOUT = 5 V, FSW = 1 MHz, AUTO Mode........................................................................................ 8

Figure 3-5. Efficiency, VOUT = 3.3 V, FSW = 1 MHz, FPWM Mode............................................................................................... 8

Figure 3-6. Efficiency, VOUT = 3.3 V, FSW = 1 MHz, AUTO Mode................................................................................................ 8

Figure 3-7. Load Regulation, VOUT = 3.3 V, FSW = 1 MHz, FPWM Mode....................................................................................9

Figure 3-8. Load Regulation, VOUT = 3.3 V, FSW = 1 MHz, AUTO Mode.....................................................................................9

Figure 3-9. Start-Up to VIN = 24 V............................................................................................................................................. 10

Figure 3-10. Shutdown ............................................................................................................................................................. 10

Figure 3-11. Enable ON and OFF .............................................................................................................................................10

Figure 3-12. Load Transient, 4 A to 8 A at 1 A/µs......................................................................................................................10

Figure 3-13. Infrared Thermal Image VIN = 12 V, VOUT = 5 V....................................................................................................10

Figure 3-14. Infrared Thermal Image VIN = 24 V, VOUT = 5 V....................................................................................................10

Figure 3-15. Infrared Thermal Image VIN = 12 V, VOUT = 3.3 V................................................................................................. 11

Figure 3-16. Infrared Thermal Image VIN = 24 V, VOUT = 3.3 V................................................................................................. 11

Figure 3-17. Bode Plot With Four 47-µF, 16-V Output Capacitors (110 µF Effective at 5 VDC, 25°C)...................................... 11

Figure 3-18. Output Capacitor Voltage Derating Curve............................................................................................................. 12

Figure 3-19. CISPR 11/32 Class B Conducted Emissions: VIN = 24 V, SPSP ON.................................................................... 13

Figure 3-20. CISPR 11 Class B Radiated Emissions: VIN = 24 V, SPSP ON............................................................................ 13

Figure 4-1. EVM Schematic.......................................................................................................................................................14

Figure 4-2. 3D Top View............................................................................................................................................................ 17

Figure 4-3. 3D Bottom View.......................................................................................................................................................17

Figure 4-4. Top Layer Copper....................................................................................................................................................18

Figure 4-5. Layer 2 Copper........................................................................................................................................................18

Figure 4-6. Layer 3 Copper........................................................................................................................................................19

Figure 4-7. Bottom Layer Copper (Viewed From Top)...............................................................................................................19

Figure 4-8. Layer Stackup......................................................................................................................................................... 19

List of Tables

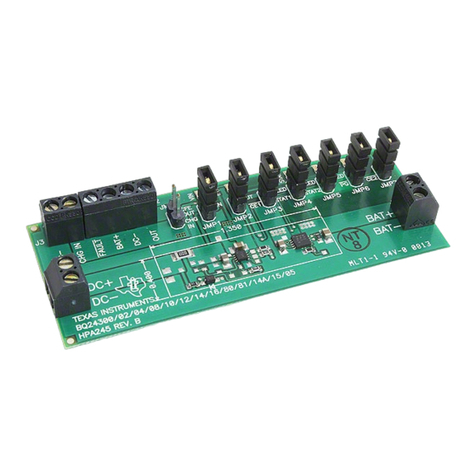

Table 1-1. TPSM63608 and TPSM63610 Synchronous Buck DC/DC Power Module Family..................................................... 1

Table 2-1. EVM Power Connections............................................................................................................................................ 5

Table 2-2. EVM Signal Connections............................................................................................................................................ 5

Table 4-1. Component BOM...................................................................................................................................................... 15

Table of Contents www.ti.com

2TPSM63610 36-V, 8-A Buck Regulator Evaluation Module User's Guide SLVUCF1A – SEPTEMBER 2022 – REVISED OCTOBER 2022

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated