www.ti.com

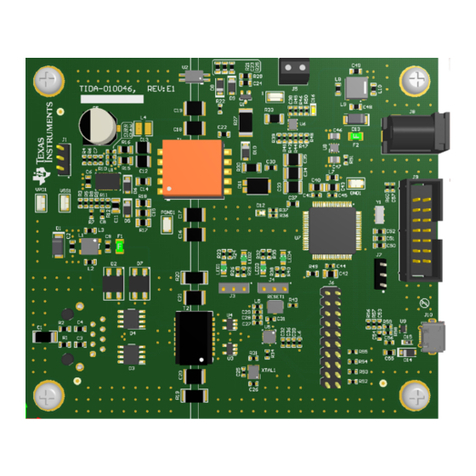

Hardware Configuration

5

SLAU580B–June 2014–Revised September 2016

Submit Documentation Feedback Copyright © 2014–2016, Texas Instruments Incorporated

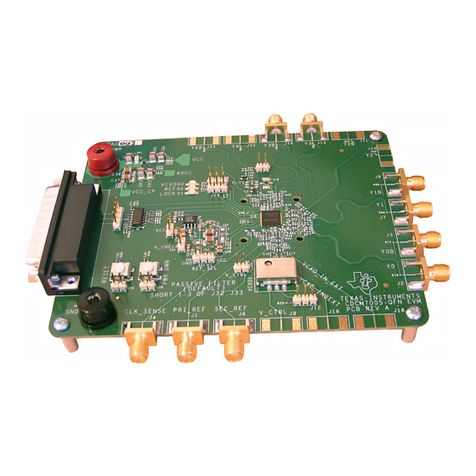

TSW14J10 FMC-USB Interposer Card

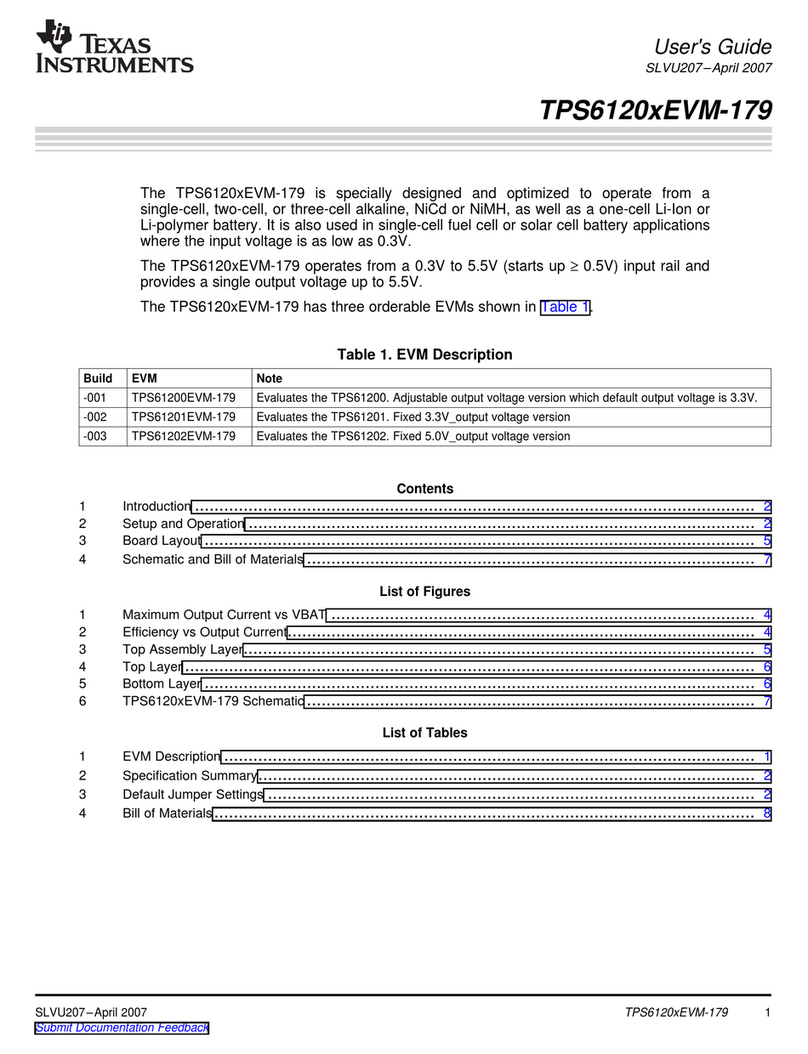

Table 1. TSW14J10 Jumper Descriptions

Component Description Default

JP1 USB power select. Default is power from the USB interface. 2-3

JP2–JP5 FTDI connected to JTAG connector or FMC. Default is JTAG connector. 1-2

JP6 Translator voltage level select (1.8 V or 3.3 V). Default is 3.3 V. 2-3

SJP1 Direction control for buffer U9. Default is A to B. 1-2

SJP2 Direction control for buffer U10. Default is B to A. 2-3

SJP3 Direction control for buffer U11. Default is B to A. 2-3

3.3 Connectors

3.3.1 FPGA Development Platform FMC Connector

The TSW14J10 EVM has one FPGA Mezzanine Card Connector (FMC) to allow for direct plug in of a TI

JESD204B serial interface ADC or DAC EVM and another to plug into an FPGA development board. The

specifications for this connector were mostly derived from the ANSI/VITA 57.1 FPGA Mezzanine Card

Standard. This standard describes the compliance requirements for a low overhead protocol bridge

between a carrier card’s IO and an FPGA processing device on a carrier card. This specification is being

used by FPGA vendors on their development platforms.

FMC connector J5 provides the interface between the TSW14J10EVM and a FPGA development platform.

This 400-pin Samtec high-speed, high- density connector, part number SEAF-40-05.0-S-10-2-A-K, is

suitable for high-speed differential pairs up to 21 Gbps. In addition to the JESD204B standard signals, 13

CMOS single-ended signals are sourced from the USB interface to the FMC connector. These signals are

used by the HSDC Pro GUI to program internal registers and read and write data to the FPGA. The

connector pinout description is shown in Table 2.

Table 2. FPGA FMC Connector (J5) Description of the TSW14J10

FMC Signal Name FMC Pin Standard JESD204

Application Mapping Description

DP0_M2C_P/N C6/C7 Lane 0+/- (M->C) JESD Serial data transmitted from Mezzanine and received by Carrier

DP1_M2C_P/N A2/A3 Lane 1+/- (M->C) JESD Serial data transmitted from Mezzanine and received by Carrier

DP2_M2C_P/N A6/A7 Lane 2+/- (M->C) JESD Serial data transmitted from Mezzanine and received by Carrier

DP3_M2C_P/N A10/A11 Lane 3+/- (M->C) JESD Serial data transmitted from Mezzanine and received by Carrier

DP4_M2C_P/N A14/A15 Lane 4+/- (M->C) JESD Serial data transmitted from Mezzanine and received by Carrier

DP5_M2C_P/N A18/A19 Lane 5+/- (M->C) JESD Serial data transmitted from Mezzanine and received by Carrier

DP6_M2C_P/N B16/B17 Lane 6+/- (M->C) JESD Serial data transmitted from Mezzanine and received by Carrier

DP7_M2C_P/N B12/B13 Lane 7+/- (M->C) JESD Serial data transmitted from Mezzanine and received by Carrier

DP8_M2C_P/N B8/B9 Lane 8+/- (M->C) JESD Serial data transmitted from Mezzanine and received by Carrier

DP9_M2C_P/N B4/B5 Lane 9+/- (M->C) JESD Serial data transmitted from Mezzanine and received by Carrier

DP0_C2M_P/N C2/C3 Lane 0+/- (C->M) JESD Serial data transmitted from Carrier and received by Mezzanine

DP1_C2M_P/N A22/A23 Lane 1+/- (C->M) JESD Serial data transmitted from Carrier and received by Mezzanine

DP2_C2M_P/N A26/A27 Lane 2+/- (C->M) JESD Serial data transmitted from Carrier and received by Mezzanine

DP3_C2M_P/N A30/A31 Lane 3+/- (C->M) JESD Serial data transmitted from Carrier and received by Mezzanine

DP4_C2M_P/N A34/A35 Lane 4+/- (C->M) JESD Serial data transmitted from Carrier and received by Mezzanine

DP5_C2M_P/N A38/A39 Lane 5+/- (C->M) JESD Serial data transmitted from Carrier and received by Mezzanine

DP6_C2M_P/N B36/B37 Lane 6+/- (C->M) JESD Serial data transmitted from Carrier and received by Mezzanine

DP7_C2M_P/N B32/B33 Lane 7+/- (C->M) JESD Serial data transmitted from Carrier and received by Mezzanine

DP8_C2M_P/N B28/B29 Lane 8+/- (C->M) JESD Serial data transmitted from Carrier and received by Mezzanine

DP9_C2M_P/N B24/B25 Lane 9+/- (C->M) JESD Serial data transmitted from Carrier and received by Mezzanine

GTX_CLKP/M D4/D5 DEVCLKA+/- (M->C) Primary carrier-bound reference clock required for FPGA gigabit transceivers.

Equivalent to device clock.

Device Clock, SYSREF, and SYNC

FMC Signal Name FMC Pin Standard JESD204

Application Mapping Description