Table of Contents

iv

RAM Configuration.............................................................................................22

Compatible RAM Devices...................................................................................22

CMOS RAM Configuration ................................................................................23

Memory Mapping................................................................................................24

I/O Configuration .............................................................................................................25

Using 8-Bit I/O Cards..........................................................................................25

Using 10-Bit I/O Cards........................................................................................25

Using 16-Bit I/O Cards........................................................................................26

COM2 Configuration........................................................................................................ 27

RS-232 Operation................................................................................................27

RS-422 Operation................................................................................................27

RS-485 Operation................................................................................................27

Opto 22 Rack Configuration.............................................................................................29

Rack Power Control.............................................................................................29

Multiprocessor Configuration ..........................................................................................30

Multiprocessor Jumper Configuration.................................................................30

Resistor Pack Configuration................................................................................31

Multiprocessor CPU Reset ..................................................................................31

Interrupt Configuration..................................................................................................... 32

Interrupt Configuration Jumpers .........................................................................33

STD Bus Interrupt Signals...................................................................................34

CPU Interrupt Request Inputs..............................................................................35

Interprocessor Communications Interrupt Configuration ...................................37

Non-maskable Interrupt Configuration ...............................................................37

DMA Configuration..........................................................................................................38

DMA Channel Allocation................................................................................................. 39

Board Initialization...........................................................................................................40

82C836 Initialization...........................................................................................41

82C721 Initialization...........................................................................................42

486SXLC Initialization........................................................................................42

RAM Refresh Initialization.................................................................................43

4. Installation.............................................................................................................................. 45

Introduction ......................................................................................................................45

Activating the Battery.......................................................................................................45

Card Insertion and Extraction........................................................................................... 45

Card Installation ..................................................................................................46

Card Placement....................................................................................................46

STD 32 Bus Installation Guidelines....................................................................46

External Connections........................................................................................................47

Connector Functions............................................................................................47

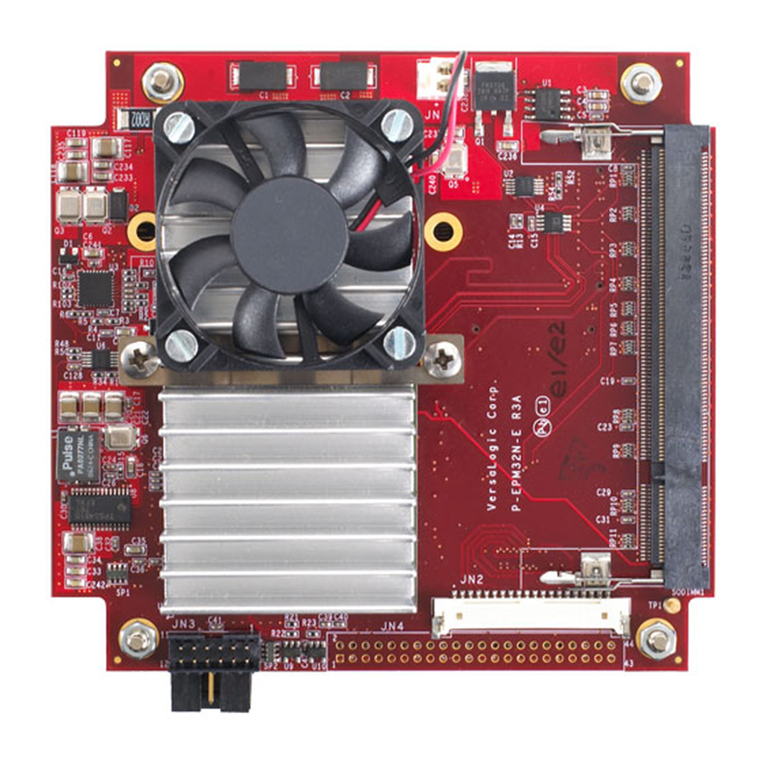

Connector Locations............................................................................................47

Mating Connectors and Cable Assemblies..........................................................48

Cable Assembly Diagrams ..................................................................................49

J1, J4 – Serial Port Connectors............................................................................50

J2 – Digital I/O Connector...................................................................................51

J3 – LPT1 Parallel Port Connector......................................................................52

J5 – Counter/Timer - Digital I/O - Interrupt Connector...................................... 53