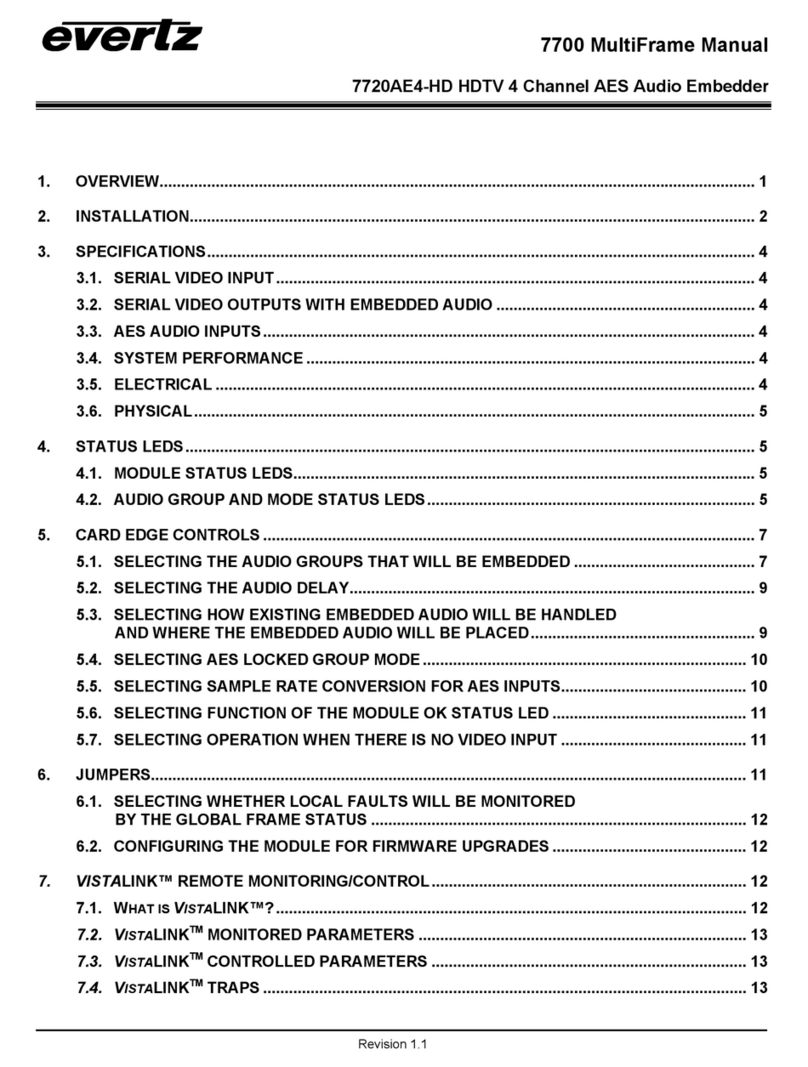

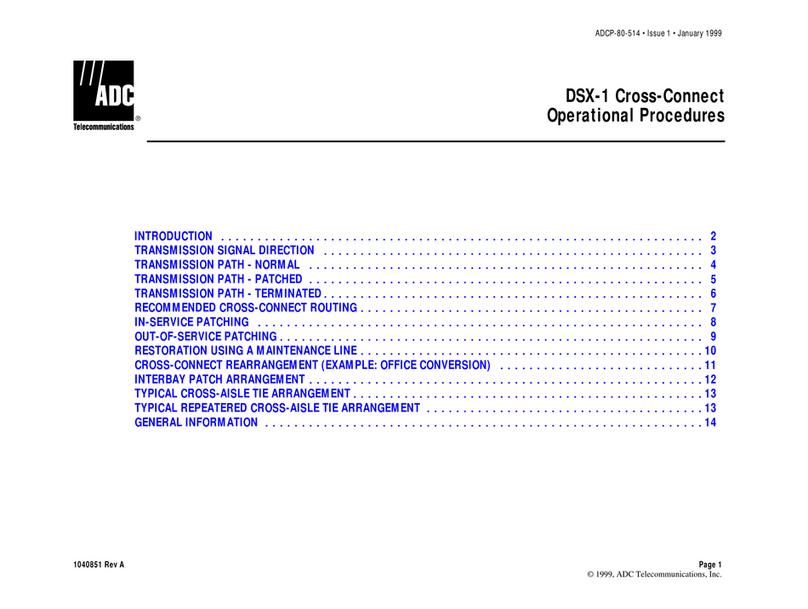

Table of Contents

Revision History...............................................................................................................2

Chapter 1: Overview......................................................................................................5

Features........................................................................................................................................5

Description................................................................................................................................... 5

Chapter 2: Connectors................................................................................................. 8

Host Side.......................................................................................................................................8

Target Side................................................................................................................................... 9

Front View.................................................................................................................................. 10

Chapter 3: Installing the SmartLynq+ Module.............................................11

Chapter 4: USB 3.0 Host Connection.................................................................. 12

Minimum Host System Requirements....................................................................................12

Default USB 3.0 IP Setting........................................................................................................ 12

Windows USB 3.0 Driver Setup................................................................................................13

Linux USB 3.0 Setup.................................................................................................................. 16

Changing the USB 3.0 IP Setting............................................................................................. 18

Chapter 5: Ethernet Connection...........................................................................19

Changing the Ethernet IP Settings..........................................................................................19

Chapter 6: SmartLynq+ Module Display.......................................................... 20

Chapter 7: JTAG Target Interface......................................................................... 21

Chapter 8: GPIO Target Interface........................................................................ 25

Chapter 9: HSDP Target Interface....................................................................... 28

Chapter 10: Parallel Debug Interface................................................................35

Appendix A: Regulatory and Compliance Information........................... 38

UG1514 (v1.0) March 8, 2021 www.xilinx.com

SmartLynq Module+ 3