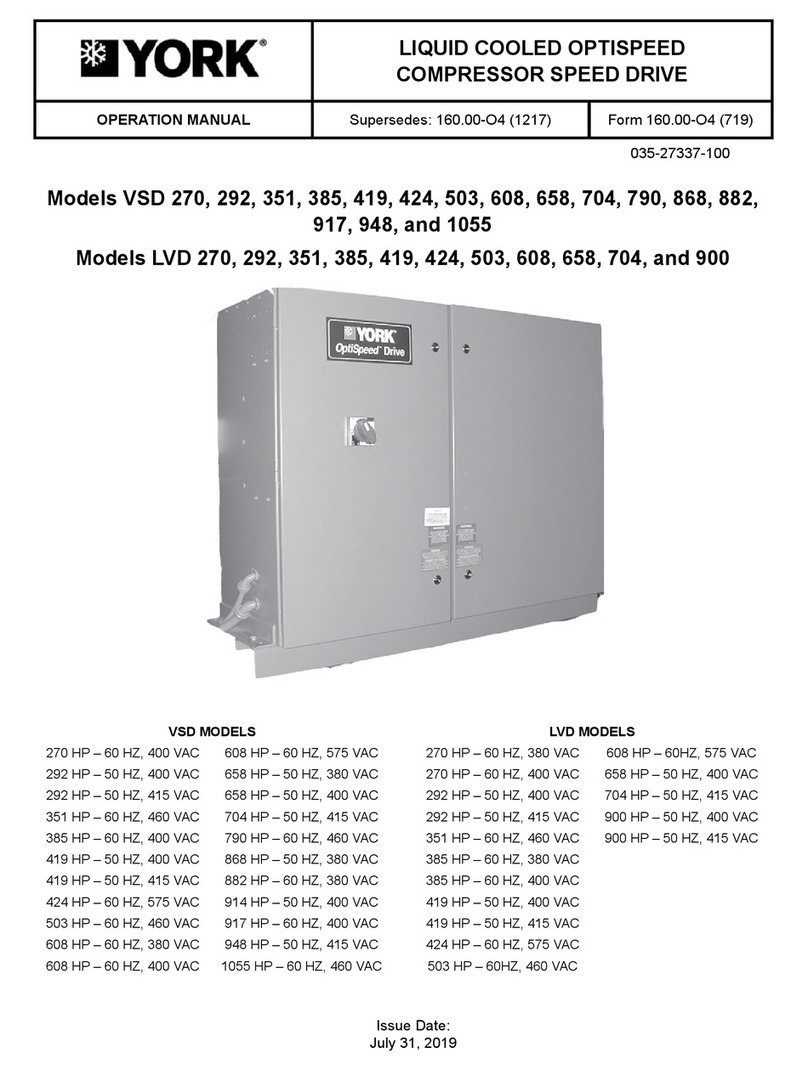

JOHNSON CONTROLS

8

FORM 160.00-O1 (1020)

to form a capacitor “bank”. In order to assure an equal sharing

of the voltage between the series connected capacitors and

to provide a discharge means for the capacitor bank when the

VSD is powered o, “bleeder” resistors (3RES and 4RES) are

connected across the capacitor banks.

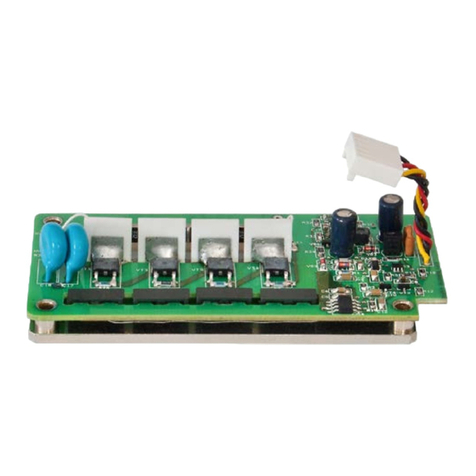

The DC to AC inverter section of the VSD (See Fig. 2), serves

to convert the rectied and ltered DC back to AC at the mag-

nitude and frequency commanded by the VSD Logic board.

The inverter section is actually composed of three identical

inverter output phase assemblies. These assemblies are in

turn composed of a series of Insulated Gate Bipolar Transistor

(IGBT) modules (Q1-Q4) mounted to a liquid cooled heatsink, a

lter capacitor “bank” (C13-C20) and a VSD Gate Driver board

(031-01476) which provides the On and O gating pulses to

the IGBT’s as determined by the VSD Logic board. In order

to minimize the parasitic inductance between the IGBT’s and

the capacitor banks, copper plates which electrically connect

the capacitors to one another and to the IGBT’s are connected

together using a “laminated bus” structure. This “laminated

bus” structure is a actually composed of a pair of copper bus

plates with a thin sheet of insulating material acting as the

separator/insulator. The “laminated bus” structure forms a

parasitic capacitor which acts as a small valued capacitor,

eectively canceling the parasitic inductance of the busbars

themselves. To further cancel the parasitic inductances, a se-

ries of small lm capacitors (C43-C51) are connected between

the positive and negative plates of the DC link. To provide

electrical shielding for the VSD Gate Driver board, an IGBT

driver “shield board” (031-01627) is mounted just beneath the

VSD Gate Driver board.

The VSD output suppression network is composed of a

series of capacitors (C61-C66) and resistors (5RES-10RES)

connected in a three phase delta conguration. The param-

eters of the suppression network components are chosen

to work in unison with the parasitic inductance of the DC to

AC inverter sections in order to simultaneously limit both the

rate of change of voltage and the peak voltage applied to

the motor windings. By limiting the peak voltage to the motor

windings, as well as the rate-of-change of motor voltage, we

can avoid problems commonly associated with PWM motor

drives, such as stator-winding end-turn failures and electrical

uting of motor bearings.

Various ancillary sensors and boards are used to convey

information back to the VSD Logic board. Each liquid cooled

heatsink within the DC to AC inverter section contains a

thermistor heatsink temperature sensor (RT1 - RT3) to provide

temperature information to the VSD logic board. The AC to

DC semi-converter heatsink temperature is also monitored

using thermistor temperature sensor RT4. The Bus Isolator

board (031-01624) utilizes three resistors on the board to

provide a “safe” impedance between the DC link lter capac-

itors located on the output phase bank assemblies and the

VSD logic board. It provides the means to sense the positive,

midpoint and negative connection points of the VSD’s DC link.

A Current Transformer (3T - 5T) is included on each output

phase assembly to provide motor current information to the

VSD logic board.

Harmonic Filter Option

The VSD system may also include an optional harmonic lter

designed to meet the IEEE Std 519 -1992, “IEEE Recom-

mended Practices and Requirements for Harmonic Control

in Electrical Power Systems”. The lter is oered as a means

to “clean up” the input current waveform drawn by the VSD

from the power mains, thus reducing the possibility of causing

electrical interference with other sensitive electronic equipment

connected to the same power source.

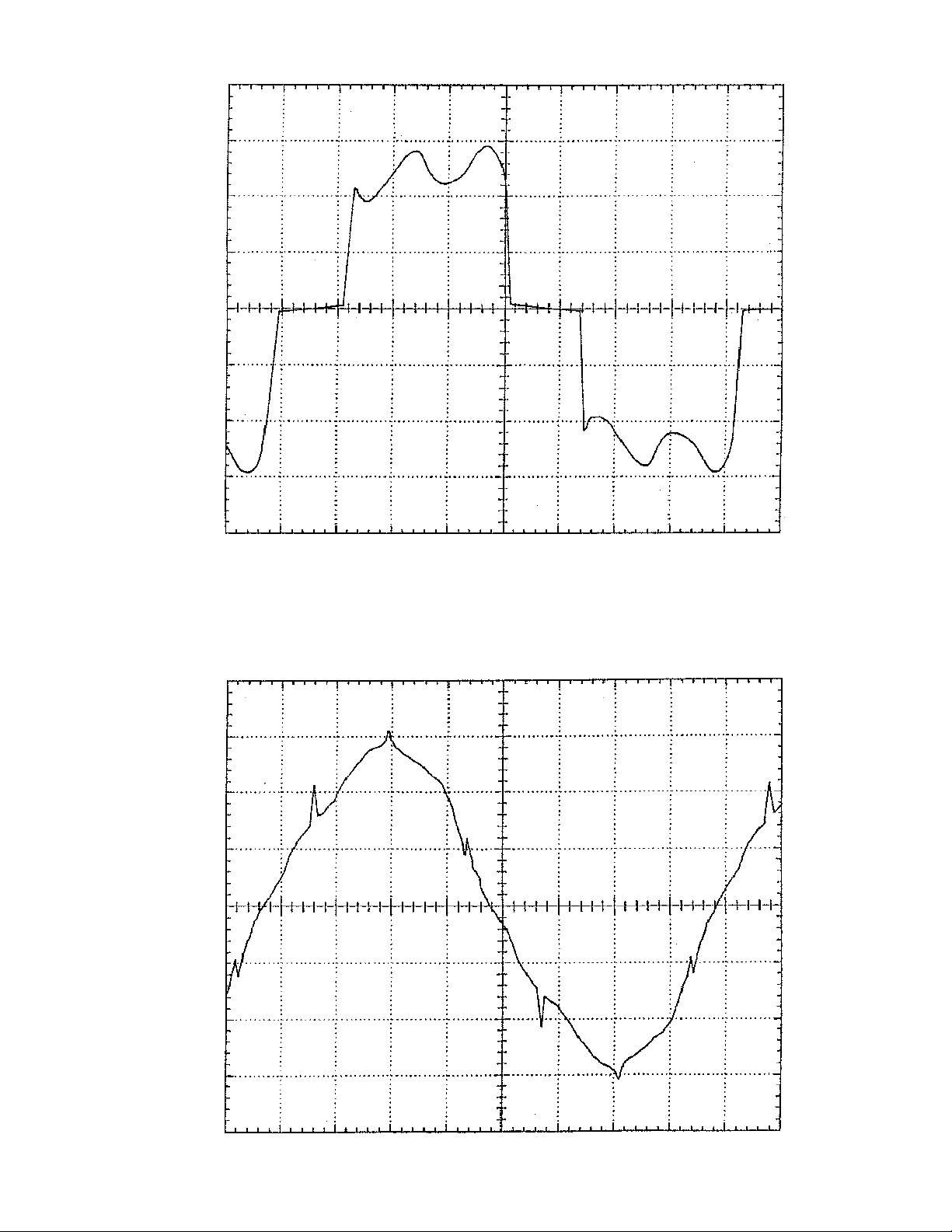

Figure 3A is a plot of the typical input current waveform for

the VSD system without the optional lter when the system

is operating at 50% load. Figure 3B is a plot of the typical

input current waveform for the VSD system with the optional

harmonic lter installed when operating at the same load

conditions. The plots show that the input current waveform

is converted from a square wave to a fairly clean sinusoidal

waveform when the lter is installed. In addition, the power

factor of the system with the optional lter installed corrects

the system power factor to nearly unity.

The power section of the Harmonic Filter is composed of four

major blocks: a pre-charge section, a “trap” lter network,

a three phase inductor and an IGBT Phase Bank Assembly

(See Fig. 4).

The pre-charge section is formed by three resistors (11RES

- 13RES) and two contactors, pre-charge contactor 2M, and

supply contactor 3M. The pre-charge network serves two pur-

poses, to slowly charge the DC link lter capacitors associated

with the lter Phase Bank Assembly (via the diodes within the

IGBT modules Q13-Q18) and to provide a means of discon-

necting the lter power components from the power mains.

When the drive is turned o, both contactors are dropped out

and the lter phase bank assembly is disconnected from the

mains. When the drive is commanded to run, the pre-charge

resistors are switched into the circuit via contactor 2M for a

xed time period of 5 seconds. This permits the lter capac-

itors in the phase bank assembly to slowly charge. After the

5 second time period, the supply contactor is pulled in and

the pre-charge contactor is dropped out, permitting the lter

Phase Bank Assembly to completely charge to the peak of the

input power mains. Three power fuses (11FU -13FU) connect

the lter power components to the power mains. Very fast

semiconductor power fuses are utilized to ensure that the

IGBT modules do not rupture if a catastrophic failure were to