RFSoC Data Converter Evaluation Tool User Guide 5

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

Chapter 1

Introduction

Overview

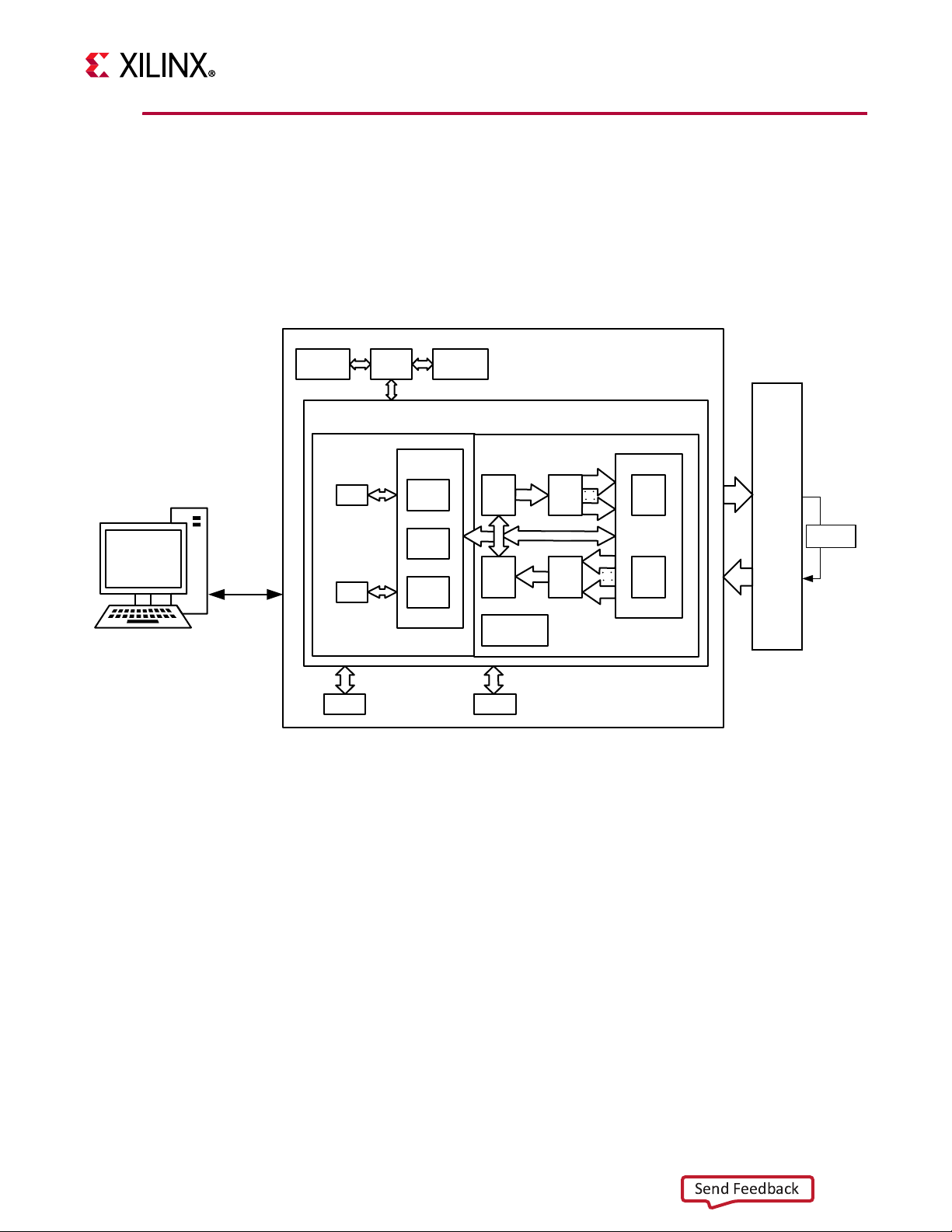

The objective of this reference design is to help you quickly and easily evaluate the new RF

Data Converter (DC) Evaluation Tool functionality in the Zynq® UltraScale+™ family of

RFSoCs. The RFSoC design demonstrates the capabilities and performance of the RF data

converter (RFDC—RF-ADC and RF-DAC) available in the RFSoC devices. The evaluation tool

serves as a platform for you to evaluate the Zynq UltraScale+ RFSoC features and helps

accelerate the product design cycle.

The evaluation tool consists of a ZCU111 evaluation board and a custom-developed

graphical user interface (GUI) installed on a Windows host machine. The evaluation tool

allows you to configure the operation of the RF-ADCs and RF-DACs and perform some basic

tests e.g., FFT analysis of the ADC output for various input test signals. The key

differentiator of Zynq UltraScale+ RFSoC devices when compared to many other discrete

solutions is that the device contains both RF-ADCs and RF-DACs. However, one significant

benefit is the DACs can be used to provide test signals for the ADC (i.e., loopback) which

facilitates a very compact and easy to use solution for early demonstration or evaluation.

All communications to the host PC (GUI) use the processing system (PS) Ethernet interface.

This is necessary to facilitate the transfer of a large amount of test data as efficiently as

possible. The ZCU111 evaluation board supports an external DDR4 memory interface on the

programmable logic (PL) in addition to the PS DDR4 memory. Waveforms with a limited

number of samples can leverage on-chip memory, but application testing and prototyping

require the use of much larger external memories.

The Xilinx® Vivado® IP integrator flow is used to create the hardware design, which is

partitioned between the PS, RFDC, and PL. The reference design uses the IP integrator core

for the RF Data Converter subsystem. The implementation supports all data rates on PL to

the Data Converter interface, all converter sample rates and digital up conversion

(DUC)/digital down conversion (DDC) configurations with a single design. The Xilinx

PetaLinux flow is used to create and integrate the software components, including the Linux

kernel and drivers.