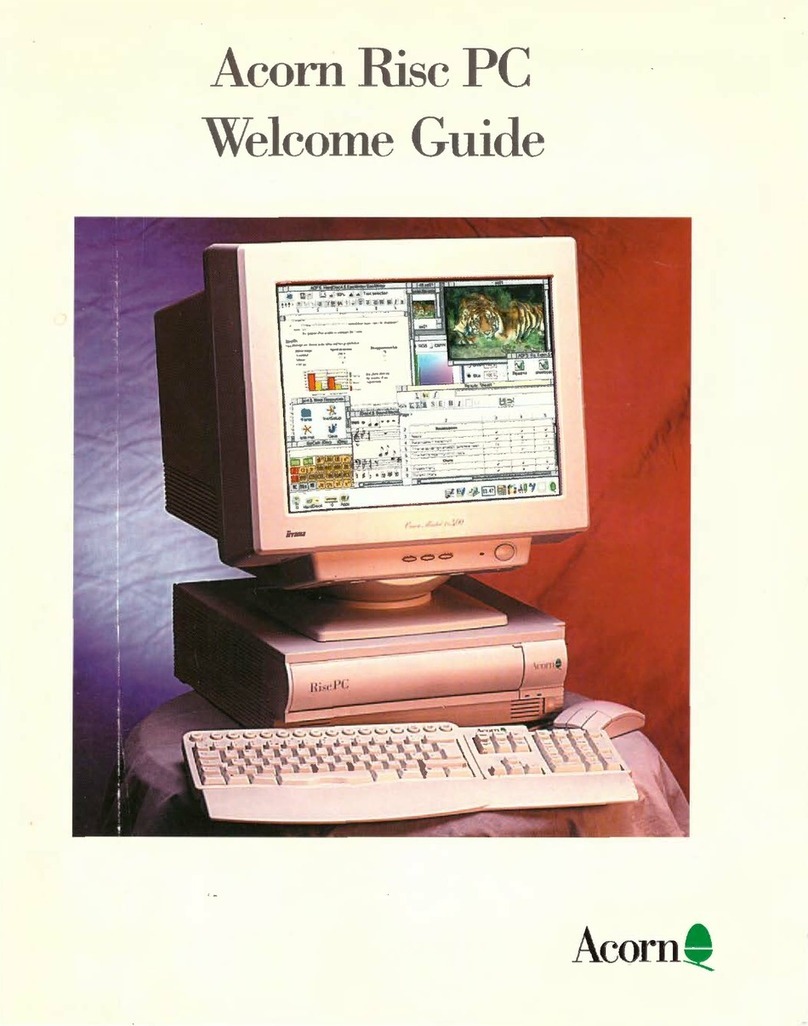

Acorn

Risc

PC Technical Reference Manual

Part 1 - System description

Introduction

The Acorn Risc PC family is built around the Advanced

Risc Machines (ARM) chipset, comprising the ARM

processor, the I/O and Memorycontroller (IOMD) and the

Video Controller (VIDC). All products feature 10MD and

VI

DC 20 and offer the following features:

DMA Enhanced Bus Interface (DEBI) -where

capabilities include 32-bit data transfer and the

support

of

up to two general purpose DMA channels

for transfer between I/O and memory

PC-AT compatible keyboard interface

Support for Video RAM (VRAM)

1-, 2-, 4-, 8-, 16- &32-bit pixel depths

Pixel rates in excess of 110 MHz

Support for up to 256

MB

of DRAM via two DRAM

SIMM sockets

Interchangeable ARM CPU card

OPEN Bus connector for second bus master

or

additional CPU.

Ablock diagram

of

the main system components

is

shown in Figure

1.1

overleaf.

General

Initially, model variants feature either

an

ARM 610

or

ARM700 processor with the option for aFloating Point

Accelerator

({PA)

to plug

in

alongside the ARM700.

the

processor is resident on a small plug

in

card which fits

in

to

one of the two 'OPEN Bus' slots on the main PCB.

Variants are also likely to appear which feature

an

Intel-

based processor resident

in

the second OPEN Bus slot.

The

number

of expansion bus slots available is either

none, 2

or

4(with architectural support for

up

to

8). The

backplane PCBs are easily interchangeable

as

they plug

into the 132-way edge connector

on

the main PCB. A

network slot is provided so that adding networkcapability

does not detract from the numberof free expansion card

slots available. This new Acorn propriety interface is,

therefore, incompatible with the existing

A30xO

and

A4000 network expansion cards.

Memory upgrading is provided for by the use of DRAM

Single In-line Memory Modules (SIMMs). Two sockets

are provided for this purpose and the machine uses

industry-standard modules chosen to meet the system

specifications. VRAM is provided on a plug-in daughter

card; this is an Acorn proprietary upgrade module and

plugs into the Dual In-line Memory Module (DIMM)

connector on the motherboard.

The Parallel, Serial, floppy disc and Integrated Drive

Electronics (IDE) hard disc sub-systems are handled by

an industry-standard PC clone Universal Peripheral

Controller device (Le. 'combo' IC). This provides PC-

standard control signals and allows each of these

interfaces to

be

(broadly) compatible with the

PC

world.

Anew version of RISC OS 3is provided with these

machines

in

two 1MB ROMS on the main PCB. This

version, 3.50, provides all the necessary software and

user interfaces

to

make use of the hardware: for instance

anew screen mode selector to cater for the increased

number of screen modes available with VIDC 20. Some

other functional improvements over version 3.11 have

also been included. The reader is referred to the

RISC as 3UserGuide for the Rise PC and RISC as3

Programmer's Reference Manual,

Vol.

5(version 3.5

supplement) for further details.

System chipset: ARM, IOMD,

vIDe

and

peripheral

controller

ARM

From the ARM 600 onwards, all ARM processors provide

afull 32-bit address bus and a32-bit program counter.

The

ARM

6xO

and

7xO

also have the ability to

be

configured in a26-bit address space mode for either

instruction fetches ordataoperations. RISC OS 3version

3.5 operates

in

26-bit address space for instruction

fetches

and

32-bit address space for data access. The

ARM610 (and 700) also feature 4KB and 8KB caches

respectively and both use write-back buffers to improve

on chip memory performance. Both devices also feature

an on-board memory management unit (MMU) with a

4KB page size.

IOMD

From

the

ARM600 onwards, the Memory Management

Unit is integrated within the ARM CPU. This has allowed

memory control and refresh (previously provided by

MEMC),

10

control (previously provided by 10C) and PC

specific I/O signals to drive the

PC

Combo device

(previously provided by lOEB) together with some new

functionality to

be

implemented in one device: the I/O

Memory Device, or 10MD. Essentially, 10MD provides

the following:

•direct interface to ARM61 0

or

ARM700

•

DRAM

control for2SIMMs providing 4banks of DRAM

•VRAM control and interface

to

VIDC20, including

generation of transfer cycles

•DMA Interface to CD-quality digital sound chip

•Video and sound DMA channels similar to that

provided by MEMC

•four general purpose 1/0 DMA channels

•..

16-bit byte-steered bus, for on-board peripherals such

as

the

network and IDE interfaces

two general purpose counter /timers and system

interrupt control registers

•interrupt line allocation similar to previous machines

•

PC

keyboard interface

•Quadrature mouse interface.

System

description

Issue 1, September 1994

1-1