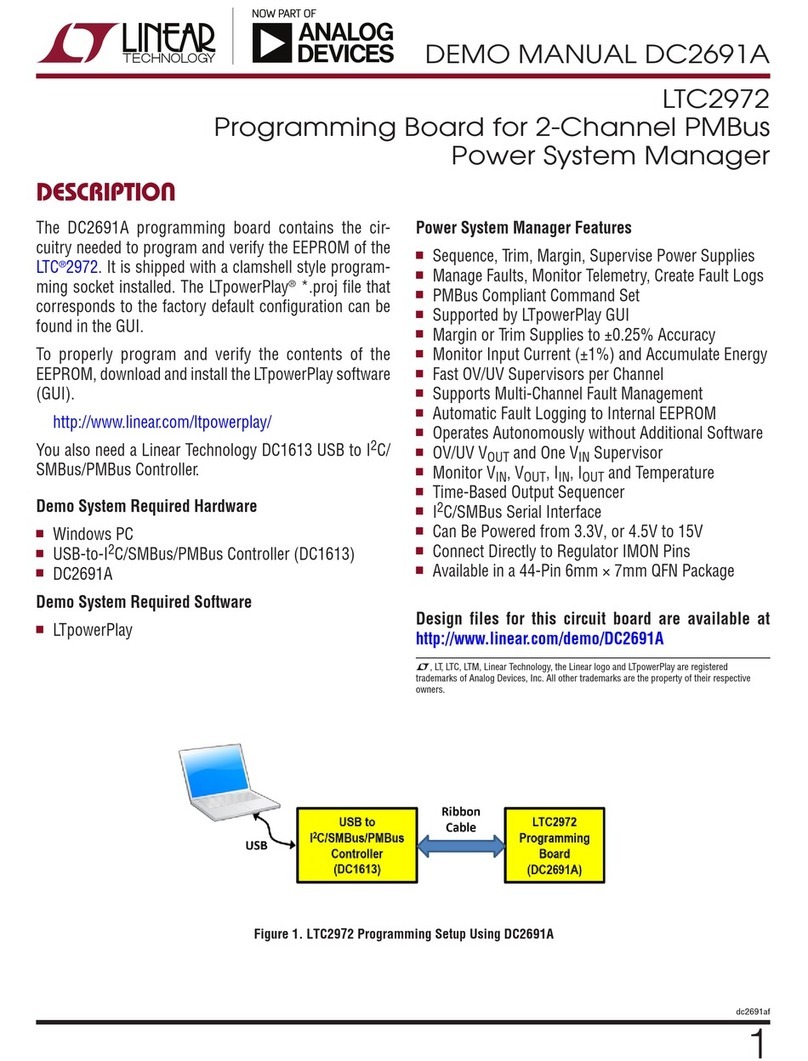

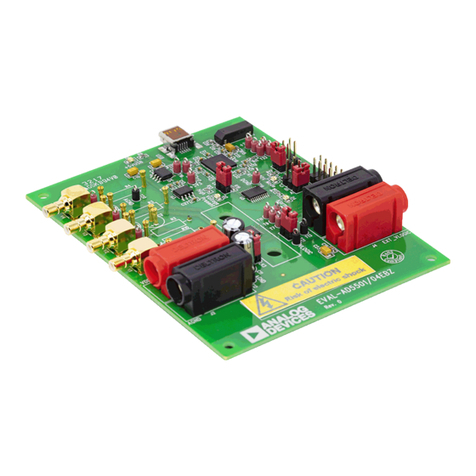

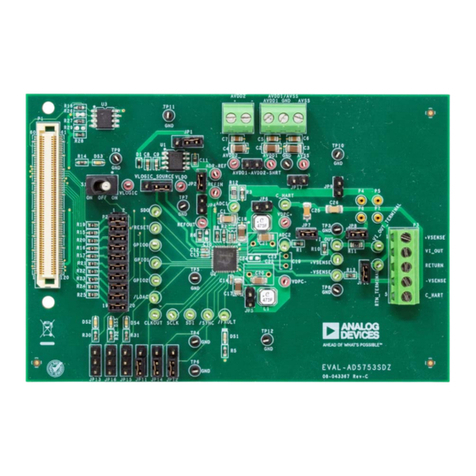

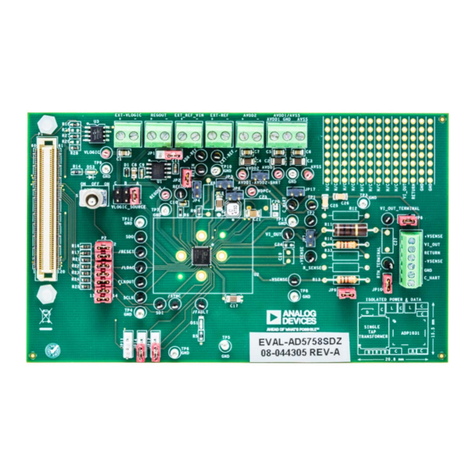

EVAL-AD5423SDZ Evaluation Board User Guide UG-1554

Rev. 0 | Page 3 of 19

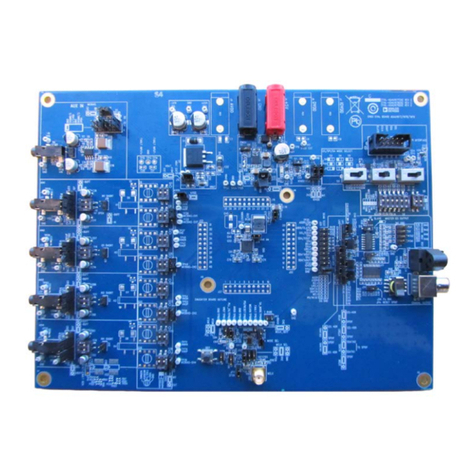

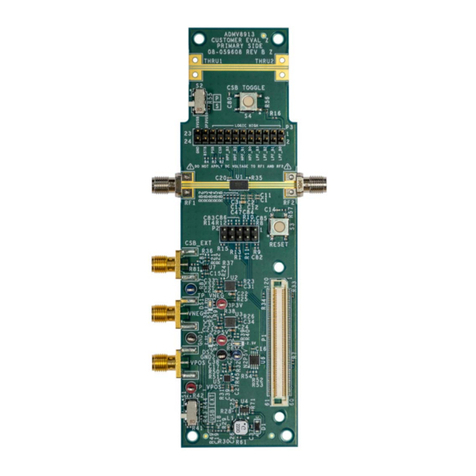

EVALUATION BOARD HARDWARE

POWER SUPPLIES

The EVAL-AD5423SDZ requires a number of power supply

inputs for the AVDD1, AVDD2, AVSS, and VLOGIC pins on the AD5423.

If there is only one positive rail available, connect the AVDD2 pin

to the AVDD1 pin via the AVDD1-AVDD2-SHRT link on the EVAL-

AD5423SDZ. The VLOGIC supply can be selected from 3.3V_SDP

on the SDP-S board or VLDO, through the JP1 and JP3 jumpers.

See Table 1 for more link options and the default link positions.

EVAL-AD5423SDZ operates with a power supply range from

−33 V on AVSS to +33 V on AVDD1 with a maximum voltage of

50 V between the two rails. AVDD2 requires a voltage between

5 V and 33 V. In a typical operating condition, AVDD2 = 5 V,

AVDD1 = +24 V, and AVSS = −24 V.

SERIAL COMMUNICATION

The SDP-S board handles the communication to the EVAL-

AD5423SDZ via the PC. By default, the SDP-S board handles

the serial port interface (SPI) communication, controls the

RESET pin and the LDAC pin, and monitors the FAULT pin of

the AD5423.

The EVAL-AD5423SDZ can disconnect from the SDP-S board

and drive the digital signals from an external source by

removing the appropriate links on P2 (see Table 2). An option

to tie the RESET pin and the LDAC pin to high or low levels is

available through the S1 switch and the JP11 link.

AD5423 DEVICE ADDRESS PINS

The device address pins (AD0 and AD1) are used in conjunction

with the device address bits within the SPI frame to determine

which AD5423 device is being addressed by the system controller.

The AD0 pin and the AD1 pin can be configured through the

JP12 and JP14 links (see Table 1).

Table 1. EVAL-AD5423SDZ Link Option Functions

Link Default Position Function

AVDD1-AVDD2-SHRT Not inserted Connects the AVDD2 pin to the AVDD1 pin.

JP1 Not inserted Selects 3.3 V from the SDP-S as the source for the VLOGIC pin.

JP2 Inserted Selects the external reference ADR-REF as the input to REFIN.

JP3 Inserted Selects 3.3 V from the VLDO pin of the AD5423 as the source for the VLOGIC pin.

JP4 Not inserted Selects the REFOUT pin as the input to the REFIN pin.

JP5 Inserted Powers external reference ADR-REF from the AVDD2 pin (the maximum supply for the ADR4525 is 15 V).

JP8 Inserted Connects the VIOUT pin to the + VSENSE pin.

JP10 Inserted Connects the –VSENSE pin to the RETURN signal on the EVAL-AD5423SDZ.

JP11 A

Position A connects the LDAC pin to the ground position. Position B connects LDAC to the VLOGIC pin.

JP12 A

Position A connects the AD0 pin to the ground position. Position B connects the AD0 pin to the

VLOGIC pin.

JP14 A

Position A connects the AD1 pin to the ground position. Position B connects the AD1 pin to the

VLOGIC pin.

JP17 Not inserted Connects the AVSS pin to the ground position pin for the unipolar supply option (current output only).

P2 Inserted

Provides options to disconnect from the SDP-S board and to drive digital signals from an

external source.

S1 Up

In the up position, this link connects the RESET pin to the VLOGIC pin.

Middle (default)

In the middle position (default), this link controls the RESET pin via the SDP-S board.

Down

In the right position, this link connects the RESET pin to the ground position pin.