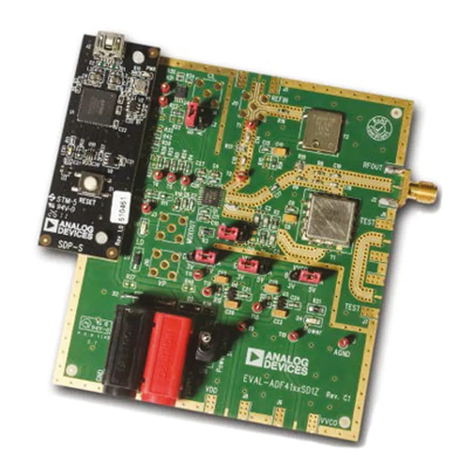

User Guide EVAL-ADAQ23876/EVAL-ADAQ23878

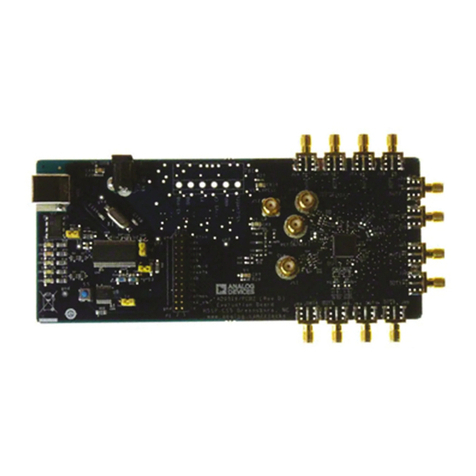

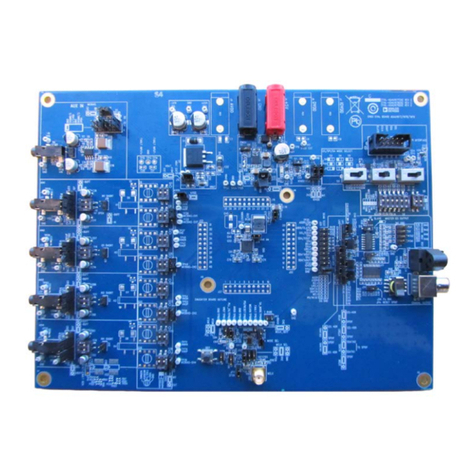

EVALUATION BOARD HARDWARE

analog.com Rev. A | 4 of 29

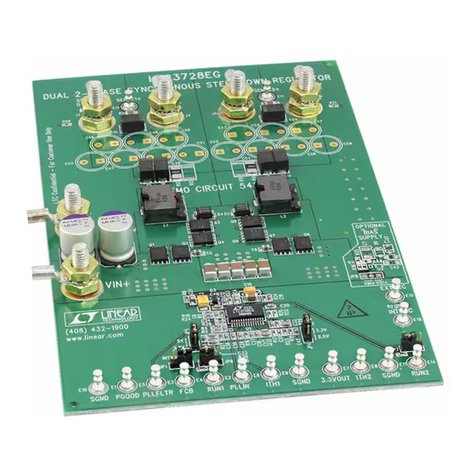

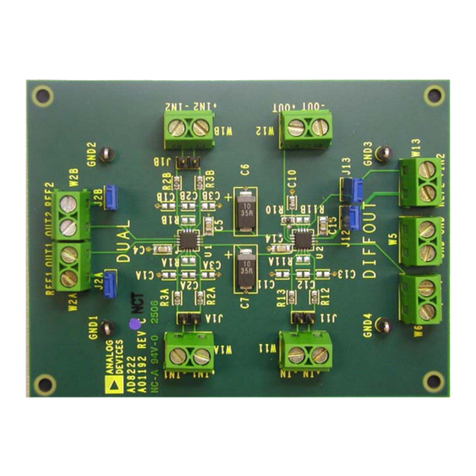

25. The optional amplifiers, ADA4899-1 (A2, A3), can be set up in a

unity-gain configuration driving the ADAQ23876 or ADAQ23878.

In a default configuration of the EVAL-ADAQ23876FMCZ and

EVAL-ADAQ23878FMCZ, an input signal via VIN+ and VIN can

be fed directly to the ADAQ23876 or ADAQ23878, respectively, by

bypassing A2 and A3.

The EVAL-ADAQ23876FMCZ and EVAL-ADAQ23878FMCZ are

factory configured to provide the appropriate input signal type, sin-

gle-ended or fully differential, and different gain/attenuation or input

range scaling. Table 2 lists the necessary jumper positions and link

options for different configurations. The default board configuration

presents a 4.096 V on the REFBUF pin and a buffered 2.048

V (midscale) of the fully differential ADC driver amplifier (FDA)'s

VCMO pin of the ADAQ23876 and ADAQ23878.

To evaluate dynamic performance, a fast Fourier transform (FFT),

integral nonlinearity (INL), differential nonlinearity (DNL), or time

domain (waveform or histogram) test can be performed by applying

a very low distortion ac source. For low input frequency testing

below 100 kHz, it is recommended to use a low noise, audio

precision signal source (such as the SYS-2700 series) with the

outputs set to balanced floating. A different precision signal source

can be used alternatively with additional band-pass filtering. The

filter bandwidth depends on input bandwidth of interest.

LINK CONFIGURATION OPTIONS

Multiple link options must be set correctly for the appropriate

operating setup before applying the power and signal to the EVAL-

ADAQ23876FMCZ or EVAL-ADAQ23878FMCZ. Table 2 shows the

default positions of the links for the EVAL-ADAQ23876FMCZ and

EVAL-ADAQ23878FMCZ.

Table 2. Link Options for the EVAL-ADAQ23876FMCZ and EVAL-ADAQ23878FMCZ

Link Default Function Comment

JP3 Center to B FPGA CNV+ Change center to A when using ADC_PLL_CNV+.

JP4 Center to B FPGA CNV- Change center to A when using ADC_PLL_CNV−.

JP5 Center to A AMP+ Change center to B when using an external supply.

JP6 Center to A AMP− Change center to B when an using external supply. If configured to the single-

supply VS− to GND, remove both jumpers (JP6) and install R49 (0 Ω).

JP9 Center to A 3.3 V Change center to B when using an external 3.3 V supply.

P1 Tie Pin 2 and Pin 3

(connected to GND)

Two-lane digital output modes Digital input that enables two-lane output mode. Use this jumper to select either

single lane or two-lane data output mode. The default setting is Pin 2 and Pin 3.

The Pin 2 and Pin 3 setting clocks out all data on the DA± pin. The Pin 1 and Pin 2

setting clocks out data alternately on the DA± and DB± pins.

P2 No connect ADCIN− Negative input of an internal ADC. Extra capacitance can be added on this pin to

reduce the RC filter bandwidth. Optional for the ADAQ23876 and ADAQ23878.

P3 No connect ADCIN+ Positive input of an internal ADC. Additional capacitance can be added on this pin

to reduce the RC filter bandwidth. Optional for the ADAQ23876 and ADAQ23878.

P4 Tie Pin 1 and Pin 2 PDB_AMP Active low. Connect this pin to GND to power down the fully differential ADC driver.

Otherwise, connect it to VS+.

P5 Not applicable SDP-H1 FMC connector The EVAL-ADAQ23876FMCZ and EVAL-ADAQ23878FMCZ interface to the SDP-

H1 via a 160-pin connector.

P6 Tie Pin 1 and Pin 2 PDB_ADC Digital input that enables the power-down mode. When PDB_ADC is low, an

internal ADC core enters power-down mode, and all circuitry (including the LVDS

interface) shuts down. When PDB_ADC is high, the device operates normally.

Logic levels are determined by VIO.

P7 0 Ω installed −VS for the ADA4899-1 (A2, A3) Remove 0 Ω to use the external supply for the ADA4899-1 (A2, A3).

P8 0 Ω installed +VS for the ADA4899-1 (A2, A3) Remove 0 Ω to use the external supply for the ADA4899-1 (A2, A3).

P9 Tie Pin 1 and Pin 2, tie

Pin 5 and Pin 6

INx− Gain pin select. Refer to Table 3 for the different gain configurations.

P10 Tie Pin 1 and Pin 2, tie

Pin 5 and Pin 6

INx+ Gain pin select. Refer to Table 3 for the different gain configurations.