REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

AD6122

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

CDMA 3 V Transmitter IF Subsystem

with Integrated Voltage Regulator

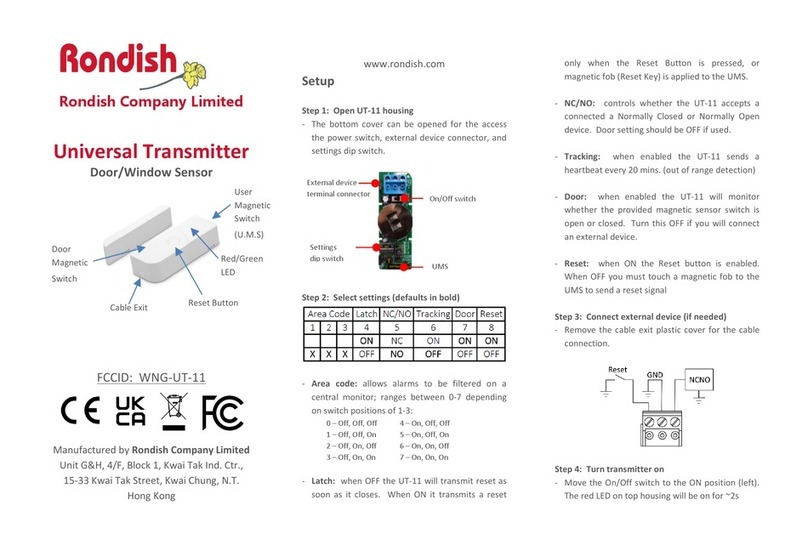

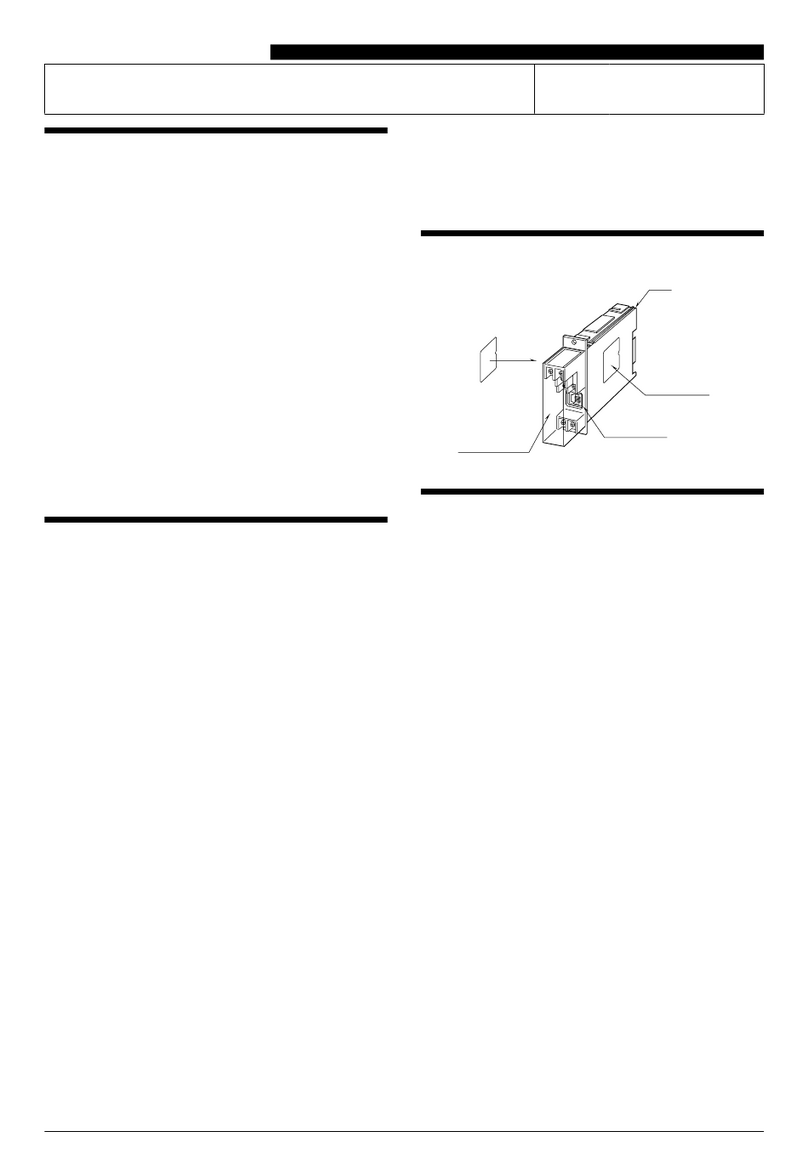

FUNCTIONAL BLOCK DIAGRAM

I INPUT

Q INPUT

LOCAL

OSCILLATOR

INPUT

ATTENUATOR

LOW

DROPOUT

REGULATOR

COMMON-MODE

REFERENCE

OUTPUT

VREG

POWER-

DOWN 1 1.23 V

REFERENCE

OUTPUT

VPOS TEMPERATURE

COMPENSATION

GAIN

CONTROL

SCALE

FACTOR

GAIN CONTROL

VOLTAGE

INPUT

GAIN CONTROL

REFERENCE

VOLTAGE

INPUT

TRANSMIT

OUTPUT

IF AMPLIFIERS

QUADRATURE MODULATOR

POWER-

DOWN 2

IF AMPLIFIER

INPUT

QUADRATURE

MODULATOR

OUTPUT

ⴜ2

AD6122

VCC

FEATURES

Fully Compliant with IS98A and PCS Specifications

Linear IF Amplifier

–63 dB to +34 dB

Linear-in-dB Gain Control

Temperature-Compensated Gain Control

Quadrature Modulator

Modulates IFs from 50 MHz to 350 MHz

Integral Low Dropout Regulator

Accepts 2.9 V to 4.2 V Input from Battery

Low Power

10.4 mA at Midgain

<10 A Sleep Mode Operation

Companion Receiver IF Chip Available (AD6121)

APPLICATIONS

CDMA, W-CDMA, AMPS and TACS Operation

QPSK Transmitters

GENERAL DESCRIPTION

The AD6122 is a low power IF transmitter subsystem, specifi-

cally designed for CDMA applications. It consists of an I and Q

modulator, a divide-by-two quadrature generator, high dynamic

range IF amplifiers with voltage-controlled gain and a power-

down control input. An integral low dropout regulator allows

operation from battery voltages from 2.9 V to 4.2 V.

The gain control input accepts an external gain control voltage

input from a DAC. It provides 97 dB of gain control with a

nominal 75 dB/V scale factor. Either an internal or an external

reference may be used to set the gain-control scale factor.

The I and Q modulator accepts differential quadrature base-

band inputs from a CDMA baseband converter. The local oscil-

lator is injected at twice the IF frequency. A divide-by-two

quadrature generator followed by dual polyphase filters ensures

±1°quadrature accuracy.

The modulator provides a common-mode reference output to

bias the transmit DACs in the baseband converter to the same

common-mode voltage as the modulator inputs, allowing dc

coupling between the two ICs and thus eliminating the need to

charge and discharge coupling capacitors. This allows the fastest

power-up and power-down times for the AD6122 and CDMA

baseband ICs.

The AD6122 is fabricated using a 25 GHz f

t

silicon BiCMOS

process and is packaged in a 28-lead SSOP and a 32-leadless

LPCC chip scale package (5 mm ×5 mm).