Evaluation Kit AT697F V3.0 [APPLICATION NOTE]

Table of Contents

1. Overview............................................................................................4

1.1 Scope4

1.2 Deliverables ......................................................................................................4

1.3 Features............................................................................................................5

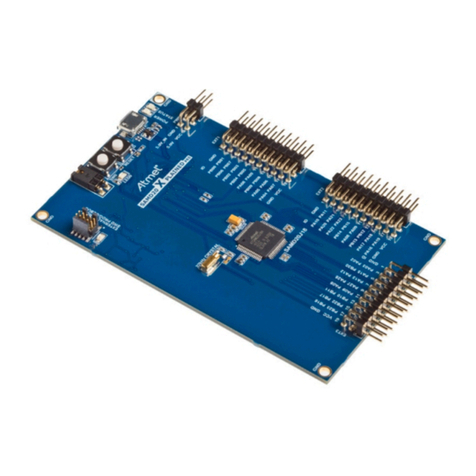

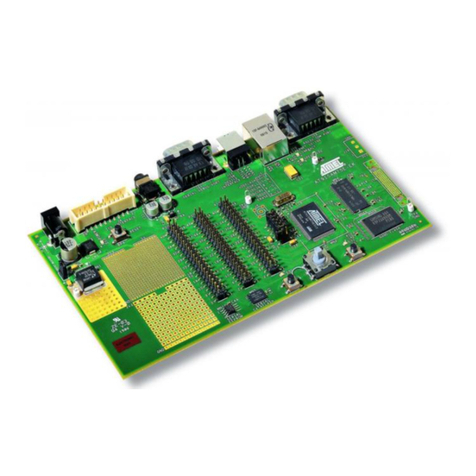

2. Hardware description.........................................................................6

2.1 Block diagram ...................................................................................................6

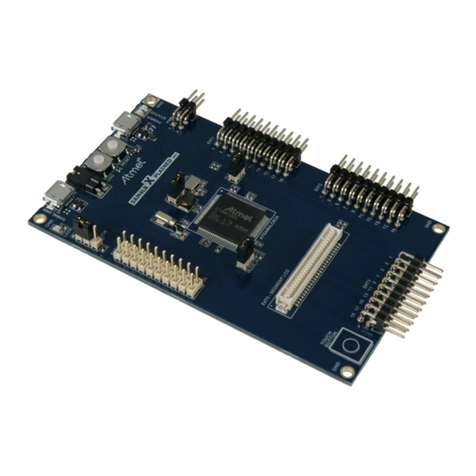

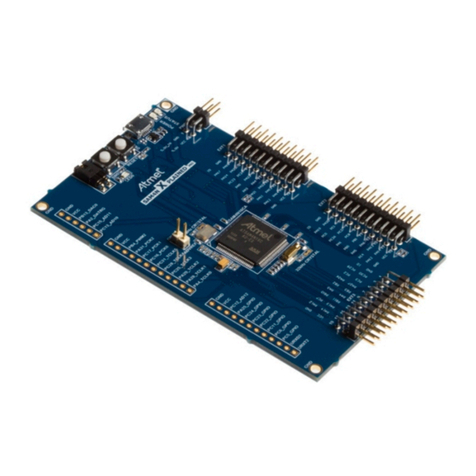

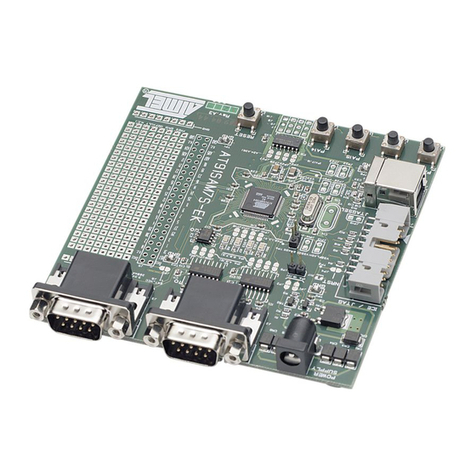

2.2 Evaluation board...............................................................................................7

2.3 Manufacturing configuration..............................................................................8

2.4 Board power supply ..........................................................................................9

2.5 Processor........................................................................................................10

2.5.1 Processor Package...........................................................................10

2.5.2 Processor Pin-out.............................................................................10

2.6 Memories ........................................................................................................13

2.6.1 Memory organization overview .........................................................13

2.6.2 PROM (or Flash)...............................................................................13

2.6.2.1 PROM Overview .............................................................13

2.6.2.2 PROM40 Configuration (SW37.7 is OFF).......................14

2.6.2.3 PROM8 Configuration (SW37.7 is ON)...........................14

2.6.2.4 PROM Expansion ...........................................................15

2.6.3 RAM Overview..................................................................................15

2.6.3.1 SRAM Configuration.......................................................15

2.6.3.2 SDRAM Configuration.....................................................16

2.7 Board HMI.......................................................................................................17

2.7.1 Board press buttons..........................................................................17

2.7.2 Board LEDs ......................................................................................17

2.7.3 Board display....................................................................................18

2.8 UART interface................................................................................................18

2.8.1 Serial link 1.......................................................................................18

2.8.2 Serial link 2.......................................................................................19

2.9 PCI interface ...................................................................................................19

2.10 Clock management.........................................................................................20

2.10.1 Clock overview..................................................................................20

2.10.2 Internal clocks...................................................................................21

2.10.3 External clocks..................................................................................21

2.10.4 Processor clock configuration...........................................................21

2.11 Evaluation Kit Reset........................................................................................22

2.11.1 Hardware reset .................................................................................22

2.11.2 Alternate reset ..................................................................................22

2.11.3 Supply voltage supervisor.................................................................22

2.11.4 Space Programmer (SPP) reset.......................................................23

2.11.5 Watchdog reset.................................................................................23

2.12 Debug Support Unit.........................................................................................23

2.13 JTAG connector..............................................................................................24

2.14 Test Points......................................................................................................24

2.14.1 Current measurement test points......................................................24

2.14.2 Clocks test points..............................................................................25

2.14.3 System and CPCI test points............................................................26

2.15 Expansion connector.......................................................................................27

2.16 Mechanical drawing ........................................................................................29

2.17 Board History ..................................................................................................30

3. Appendix A –Getting Started...........................................................31

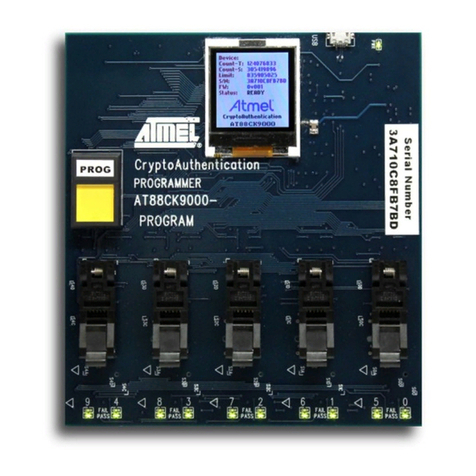

3.1 AT697 Development Kit Content.....................................................................31

3.2 Handling..........................................................................................................32

3.3 System requirements......................................................................................32