Averlogic AL462B-EVB-A0 User manual

AL462B-EVB-A0-User Manual

©2018 Copyright by AverLogic Technologies, Corp. Version 1.0

AL462B-EVB-A0

Evaluation Board with HSMC Interface

User Manual

Version 1.0

INFORMATION FURNISHED BY AVERLOGIC IS BELIEVED TO BE ACCURATE AND RELIABLE. HOWEVER,

NO RESPONSIBILITY IS ASSUMED BY AVERLOGIC FOR ITS USE, OR FOR ANY INFRINGEMENTS OF

PATENTS, OR OTHER RIGHTS OF THIRD PARTIES THAT MAY RESULT FROM ITS USE. NO LICENSE IS

GRANTED BY IMPLICATION OR OTHERWISE UNDER ANY PATENT OR PATENT RIGHTS OF AVERLOGIC.

©2018 by AverLogic Technologies, Corp.

AL462B-EVB-A0-User Manual

©2018 Copyright by AverLogic Technologies, Corp. Version 1.0 2

Amendments

Revise Date

Contents

Author

2018.12.28

Formal Release Version 1.0

Ken Liu

Disclaimer

THE CONTENTS OF THIS DOCUMENT ARE SUBJECT TO CHANGE WITHOUT

NOTICE. AVERLOGIC TECHNOLOGIES RESERVES THE RIGHT TO MAKE CHANGES

WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE

RELIABILITY, FUNCTION OR DESIGN. AVERLOGIC DOES NOT ASSUME ANY

LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR

CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER

ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. CUSTOMERS ARE ADVISED

TO CONSULT WITH AVERLOGIC OR ITS COMMERCIAL DISTRIBUTORS BEFORE

ORDERING.

AL462B-EVB-A0-User Manual

©2018 Copyright by AverLogic Technologies, Corp. Version 1.0 3

Table of Contents

1 INTRODUCTION..........................................................................................4

1.1 KIT CONTENT.................................................................................................................4

2 EVB CONTROL INTERFACE......................................................................5

2.1 BOARD VIEW..................................................................................................................5

2.2 USER CONTROL INTERFACE ............................................................................................6

3 ADAPTOR INTERFACE..............................................................................7

3.1 ALTERA HSMC CONNECTOR...........................................................................................7

3.2 J1/J3 DEBUG PORT –40-PIN HEADERS...........................................................................9

4 MECHANICAL SPECIFICATION...............................................................10

AL462B-EVB-A0-User Manual

©2018 Copyright by AverLogic Technologies, Corp. Version 1.0 4

1 Introduction

The AL462 HSMC EVB is designed for connecting the AL462 chip to an ALTERA FPGA

board. This configuration facilitates design verification/validation when developing or testing

with the AL462 chip.

The HSMC connector is a modified version of a standard high-speed Samtec connector,

which is pin-to-pin compatible with the Cyclone V FPGA host board’s HSMC connector.

We also provide an FPGA sample code for Cyclone V GX Kit. Please contact your

AverLogic representative for more information.

1.1 EVB Content

Evaluation Board

5V Power Adapter

AL462B-EVB-A0-User Manual

©2018 Copyright by AverLogic Technologies, Corp. Version 1.0 5

2 EVB Control Interface

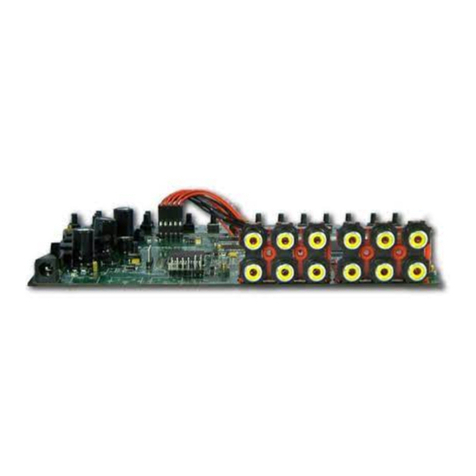

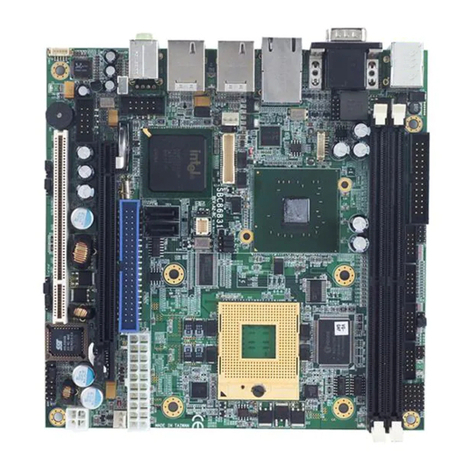

2.1 Board View

Top Side

Bottom Side

HSMC Connector

1

Short Open

AL462

J3 J1

J4

J5

J6

S2

S1

JP1

JP2

ST1 ST2 ST3 ST4 ST5 ST6

S3

J2

SW1

J7 (Bottom)

On Off

AL462B-EVB-A0-User Manual

©2018 Copyright by AverLogic Technologies, Corp. Version 1.0 6

2.2 User Control Interface

Name

Function

Default

SW1

Reset

/

J1

Data Pins for debugging

/

J2

5V DC Power

/

J3

Data Pins for debugging

/

J4

Pin1:RCKO_0; Pin 2:RCKO_1; Pin 3:RENO_0; Pin 4:RENO_1

/

J5

Pin1:WFSEL_0; Pin 2:WFSEL_1; Pin 3:RFSEL_0; Pin 4:RFSEL_1

/

J6

Pin1:WE_IE_SEL; Pin 2:PLRTY; Pin 3:TFEN; Pin 4:16EN

/

J7

HSMC Connector

/

S1

IE0 & IE1 enable pins

Short/On

S2

OE0 and OE1 enable pins

Short/On

S3

Power Switch

/

JP1

Reserved for I/O Power

/

JP2

Reserved for I/O Power

/

ST1

1-8 DL_CFG_0

2-7 DL_CFG_1

3-6 DL_CFG_1

4-5 TMOD_2

Open/Off

Open/Off

Open/Off

Open/Off

ST2

1-8 D_CFG_4

2-7 D_CFG_5

3-6 RCKOINV_0

4-5 RCKOINV_1

Open/Off

Open/Off

Open/Off

Open/Off

ST3

1-8 D_CFG_4

2-7 D_CFG_5

3-6 RCKOINV_0

4-5 RCKOINV_1

Open/Off

Open/Off

Open/Off

Open/Off

ST4

1-8 RCKO_0

2-7 RCKO_1

3-6 RENO_0

4-5 RENO_1

Short/On

Short/On

Short/On

Short/On

ST5

1-8 WFSEL_0

2-7 WFSEL_1

3-6 RFSEL_0

4-5 RFSEL_1

Open/Off

Open/Off

Open/Off

Open/Off

ST6

1-8 WE_IE_SEL

2-7 PLRTY

3-6 TFEN

4-5 16EN

Short/On

Open/Off

Open/Off

Open/Off

S1

AL462B-EVB-A0-User Manual

©2018 Copyright by AverLogic Technologies, Corp. Version 1.0 7

3 Adaptor Interface

3.1 Altera HSMC connector

The HSMC connector reference part numbers are listed in the table directly below. The

HSMC reference label on the adaptor board is J7.

Altera-Specific Samtec Part Number

ASP-122952-01

Table: HSMC Part Numbers

The user interface between the evaluation board and the HSMC connector is shown in the

Pin Description table below.

AL462

J1/J3 Debug Port

HSMC

AL462 I/O

Signal Name

Pin Number

Signal Name

Pin Number

DI_31

HSMC_DI_31

J1/1

HSMC_DI_Ch2_15

41

DI_15

HSMC_DI_15

J1/2

HSMC_DI_Ch1_15

42

DI_30

HSMC_DI_30

J1/3

HSMC_DI_Ch2_14

43

DI_14

HSMC_DI_14

J1/4

HSMC_DI_Ch1_14

44

DI_29

HSMC_DI_29

J1/5

HSMC_DI_Ch2_13

47

DI_13

HSMC_DI_13

J1/6

HSMC_DI_Ch1_13

48

DI_28

HSMC_DI_28

J1/7

HSMC_DI_Ch2_12

49

DI_12

HSMC_DI_12

J1/8

HSMC_DI_Ch1_12

50

DI_27

HSMC_DI_27

J1/9

HSMC_DI_Ch2_11

53

DI_11

HSMC_DI_11

J1/10

HSMC_DI_Ch1_11

54

DI_26

HSMC_DI_26

J1/11

HSMC_DI_Ch2_10

55

DI_10

HSMC_DI_10

J1/12

HSMC_DI_Ch1_10

56

DI_25

HSMC_DI_25

J1/13

HSMC_DI_Ch2_09

59

DI_09

HSMC_DI_09

J1/14

HSMC_DI_Ch1_09

60

DI_24

HSMC_DI_24

J1/15

HSMC_DI_Ch2_08

61

DI_08

HSMC_DI_08

J1/16

HSMC_DI_Ch1_08

62

DI_23

HSMC_DI_23

J1/17

HSMC_DI_Ch2_07

65

DI_07

HSMC_DI_07

J1/18

HSMC_DI_Ch1_07

66

DI_22

HSMC_DI_22

J1/19

HSMC_DI_Ch2_06

67

DI_06

HSMC_DI_06

J1/20

HSMC_DI_Ch1_06

68

DI_21

HSMC_DI_21

J1/21

HSMC_DI_Ch2_05

71

DI_05

HSMC_DI_05

J1/22

HSMC_DI_Ch1_05

72

DI_20

HSMC_DI_20

J1/23

HSMC_DI_Ch2_04

73

DI_04

HSMC_DI_04

J1/24

HSMC_DI_Ch1_04

74

DI_19

HSMC_DI_19

J1/25

HSMC_DI_Ch2_03

77

DI_03

HSMC_DI_03

J1/26

HSMC_DI_Ch1_03

78

DI_18

HSMC_DI_18

J1/27

HSMC_DI_Ch2_02

79

DI_02

HSMC_DI_02

J1/28

HSMC_DI_Ch1_02

80

DI_17

HSMC_DI_17

J1/29

HSMC_DI_Ch2_01

83

DI_01

HSMC_DI_01

J1/30

HSMC_DI_Ch1_01

84

DI_16

HSMC_DI_16

J1/31

HSMC_DI_Ch2_00

85

DI_00

HSMC_DI_00

J1/32

HSMC_DI_Ch1_00

86

AL462B-EVB-A0-User Manual

©2018 Copyright by AverLogic Technologies, Corp. Version 1.0 8

WEN_1

HSMC_DI_DE2

J1/35

HSMC_DI_Ch2_WEN

89

WEN_0

HSMC_D1_DE1

J1/36

HSMC_DI_Ch1_WEN

90

WRST_1

HSMC_DI_VS2

J1/37

HSMC_DI_Ch2_RST

91

WRST_0

HSMC_DI_VS1

J1/38

HSMC_DI_Ch1_RST

92

IE_1

HSMC_DI_CH2_IE

J1/33

HSMC_DI_Ch2_IE

95

IE_0

HSMC_DI_CH1_IE

J1/34

HSMC_DI_Ch1_IE

96

WCLK_1

HSMC_DI_CKL2

J1/39

HSMC_DI_Ch2_CLK

97

WCLK_0

HSMC_D1_CKL1

J1/40

HSMC_DI_Ch1_CLK

98

DO_31

HSMC_DO_31

J3/1

HSMC_DO_CH2_15

101

DO_15

HSMC_DO_15

J3/2

HSMC_DO_CH1_15

102

DO_30

HSMC_DO_30

J3/3

HSMC_DO_CH2_14

103

DO_14

HSMC_DO_14

J3/4

HSMC_DO_CH1_14

104

DO_29

HSMC_DO_29

J3/5

HSMC_DO_CH2_13

107

DO_13

HSMC_DO_13

J3/6

HSMC_DO_CH1_13

108

DO_28

HSMC_DO_28

J3/7

HSMC_DO_CH2_12

109

DO_12

HSMC_DO_12

J3/8

HSMC_DO_CH1_12

110

DO_27

HSMC_DO_27

J3/9

HSMC_DO_CH2_11

113

DO_11

HSMC_DO_11

J3/10

HSMC_DO_CH1_11

114

DO_26

HSMC_DO_26

J3/11

HSMC_DO_CH2_10

115

DO_10

HSMC_DO_10

J3/12

HSMC_DO_CH1_10

116

DO_25

HSMC_DO_25

J3/13

HSMC_DO_CH2_09

119

DO_09

HSMC_DO_09

J3/14

HSMC_DO_CH1_09

120

DO_24

HSMC_DO_24

J3/15

HSMC_DO_CH2_08

121

DO_08

HSMC_DO_08

J3/16

HSMC_DO_CH1_08

122

DO_23

HSMC_DO_23

J3/17

HSMC_DO_CH2_07

125

DO_07

HSMC_DO_07

J3/18

HSMC_DO_CH1_07

126

DO_22

HSMC_DO_22

J3/19

HSMC_DO_CH2_06

127

DO_06

HSMC_DO_06

J3/20

HSMC_DO_CH1_06

128

DO_21

HSMC_DO_21

J3/21

HSMC_DO_CH2_05

131

DO_05

HSMC_DO_05

J3/22

HSMC_DO_CH1_05

132

DO_20

HSMC_DO_20

J3/23

HSMC_DO_CH2_04

133

DO_04

HSMC_DO_04

J3/24

HSMC_DO_CH1_04

134

DO_19

HSMC_DO_19

J3/25

HSMC_DO_CH2_03

137

DO_03

HSMC_DO_03

J3/26

HSMC_DO_CH1_03

138

DO_18

HSMC_DO_18

J3/27

HSMC_DO_CH2_02

139

DO_02

HSMC_DO_02

J3/28

HSMC_DO_CH1_02

140

DO_17

HSMC_DO_17

J3/29

HSMC_DO_CH2_01

143

DO_01

HSMC_DO_01

J3/30

HSMC_DO_CH1_01

144

DO_16

HSMC_DO_16

J3/31

HSMC_DO_CH2_00

145

DO_00

HSMC_DO_00

J3/32

HSMC_DO_CH1_00

146

REN_1

HSMC_DO_DE2

J3/35

HSMC_DO_Ch2_REN

149

REN_0

HSMC_DO_DE1

J3/36

HSMC_DO_Ch1_REN

150

RRST_0

HSMC_DO_VS2

J3/37

HSMC_DO_Ch2_RST

151

RRST_1

HSMC_DO_VS1

J3/38

HSMC_DO_Ch1_RST

152

OE_1

HSMC_DO_CH2_OE

J3/33

HSMC_DO_Ch2_OE

155

OE_0

HSMC_DO_CH1_OE

J3/34

HSMC_DO_Ch1_OE

156

RCLK_1

HSMC_DO_CLK2

J3/39

HSMC_DO_Ch2_CLK

157

RCLK_0

HSMC_DO_CKL1

J3/40

HSCM_DO_Ch1_CLK

158

Table: HSMC Pin Description

AL462B-EVB-A0-User Manual

©2018 Copyright by AverLogic Technologies, Corp. Version 1.0 9

The HSMC connector pin-map for the adaptor is illustrated in the figure below.

Figure: HSMC Connector Pin-Map.

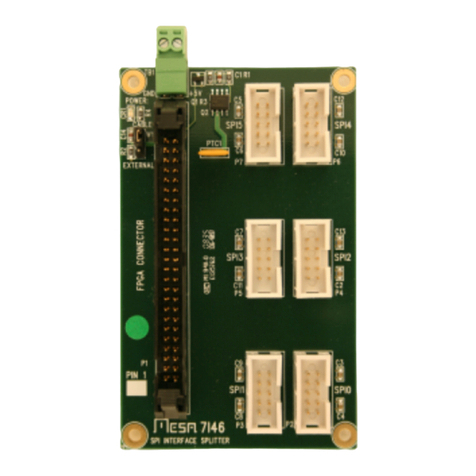

3.2 J1/J3 Debug Port –40-pin Headers

The pin-maps for the two headers are shown in the figure below.

Figure: Two Debug Port Pin-Map

J1 J3

AL462B-EVB-A0-User Manual

©2018 Copyright by AverLogic Technologies, Corp. Version 1.0 10

4 Mechanical Specification

Diagram

150mm

150mm

164mm

35.6mm

35.6mm

Table of contents

Other Averlogic Motherboard manuals