v1.1

Table of Contents

1Introduction .................................................................................................................... 3

1.1 Glossary ...............................................................................................................................3

1.2 Additional Documentation....................................................................................................3

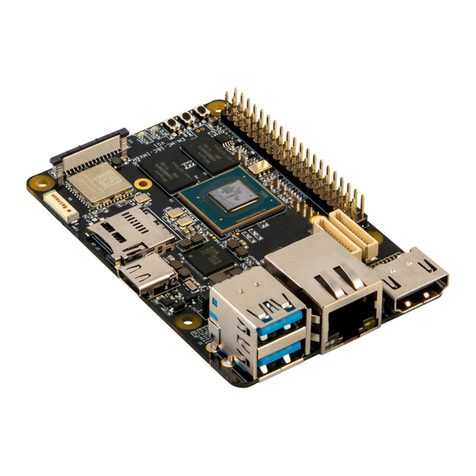

1.3 PZCC-FMC-V2 Features: ........................................................................................................4

2Functional Description..................................................................................................... 8

2.1 Reset sources .......................................................................................................................8

2.2 User I/O – Switches and LEDs................................................................................................9

2.3 I2C Address space and registers ..........................................................................................11

2.4 Clocks.................................................................................................................................12

2.5 PCIe x1 Gen2 Interface........................................................................................................13

2.6FMC LPC Connector ............................................................................................................14

2.7 SFP+ Interface – P1 (7015/30 SOM only)..............................................................................17

2.8 PS/PL PMOD™ Interfaces – JA, JB, JZ & JPS1 ........................................................................18

2.9 JX1, JX2 and JX3 SOM Interface MicroHeaders.....................................................................19

2.10 Multi-Gigabit Transceivers (MGTs)...................................................................................22

2.11 USB UART – J1.................................................................................................................23

2.12 USB OTG Interface – J8 ....................................................................................................24

2.13 SOM 10/100/1000 Ethernet RJ45 – J9 ..............................................................................25

2.14 MAC ID – EEPROM...........................................................................................................26

2.15 MAC ID – UNI/O EEPROM (7Z015/30 only).......................................................................27

2.16 Real Time Clock – Maxim DS3231MZ................................................................................27

2.17 HDMI Interface – J10 .......................................................................................................29

2.18 microSD Card Interface....................................................................................................30

2.19 Fan Header – JP3 .............................................................................................................31

2.20 JTAG Configuration – J7 ...................................................................................................31

3Power ........................................................................................................................... 32

3.1 Power Input – J2/SW7 ........................................................................................................32

3.2 Molex to Non-ATX connection ............................................................................................33

3.3 Power Rails ........................................................................................................................33

3.4 2.5V LDO – U12...................................................................................................................33

3.5 JP1 – FPGA VBAT (VCCBATT) ...............................................................................................34

3.6 VADJ selection - JP5 ............................................................................................................34

3.7 Sequencing.........................................................................................................................35

3.8 Bypassing/Decoupling/Filtering ..........................................................................................36

3.9 PG Module Power Good LED ...............................................................................................36

4Jumpers, configuration and test points: ......................................................................... 37

4.1 FMC GA [1:0] jumper header...............................................................................................38

4.2 Clock Synthesizer test header..............................................................................................38

4.3 Power Supply monitor header – J12 ....................................................................................39

5Mechanical ................................................................................................................... 39

5.1 Diagram and Model ............................................................................................................39

5.2 Weight ...............................................................................................................................39

6Revision History ............................................................................................................ 40

Appendix A – additional information/test results................................................................. 41