Chassis Plans MX8 Use and care manual

MX8

S6240-xxx

TECHNICAL REFERENCE

Intel®Pentium®4

or

Intel®Celeron®

PROCESSOR-BASED

SBC

WARRANTY The product is warranted against material and manufacturing defects for two years from

date of delivery. Buyer agrees that if this product proves defective Chassis Plans. is only

obligated to repair, replace or refund the purchase price of this product at Chassis Plans’

discretion. The warranty is void if the product has been subjected to alteration, neglect,

misuse or abuse; if any repairs have been attempted by anyone other than Chassis Plans;

or if failure is caused by accident, acts of God, or other causes beyond the control of

Chassis Plans. Chassis Plans reserves the right to make changes or improvements in any

product without incurring any obligation to similarly alter products previously

purchased.

In no event shall Chassis Plans be liable for any defect in hardware or software or loss or

inadequacy of data of any kind, or for any direct, indirect, incidental or consequential

damages arising out of or in connection with the performance or use of the product or

information provided. Chassis Plans’ liability shall in no event exceed the purchase

price of the product purchased hereunder. The foregoing limitation of liability shall be

equally applicable to any service provided by Chassis Plans.

RETURN POLICY Products returned for repair must be accompanied by a Return Material Authorization

(RMA) number, obtained from Chassis Plans prior to return. Freight on all returned

items must be prepaid by the customer, and the customer is responsible for any loss or

damage caused by common carrier in transit. Items will be returned from Chassis Plans

via Ground, unless prior arrangements are made by the customer for an alternative

shipping method

To obtain an RMA number, call us at (858) 571-4330. We will need the following infor-

mation:

Return company address and contact

Model name and model # from the label on the back of the board

Serial number from the label on the back of the board

Description of the failure

An RMA number will be issued. Mark the RMA number clearly on the outside of each

box, include a failure report for each board and return the product(s) to our San Diego,

CA facility:

Chassis Plans

8295 Aero Place, Suite 200

San Diego, CA 92123

Attn: Repair Department

(858) 571-4330

TRADEMARKS IBM, PC, VGA, EGA, OS/2 and PS/2 are trademarks or registered

trademarks of International Business Machines Corp.

AMI and AMIBIOS are trademarks of American Megatrends Inc.

Intel, Pentium and Celeron are registered trademarks of Intel Corporation.

ATI is a registered trademark of ATI Technologies Incorporated.

MS-DOS and Microsoft are registered trademarks of Microsoft Corp.

PICMG and the PICMG logo are registered trademarks of the PCI

Industrial Computer Manufacturers Group.

SCSISelect is a trademark of Adaptec, Inc.

All other brand and product names may be trademarks or registered

trademarks of their respective companies.

LIABILITY

DISCLAIMER

This manual is as complete and factual as possible at the time of printing; however, the

information in this manual may have been updated since that time. Chassis Plans

reserves the right to change the functions, features or specifications of their products at

any time, without notice.

Copyright ©2004 by Chassis Plans. All rights reserved.

E-mail: [email protected]

Web: www.chassisplans.com

Chassis Plans

8295 Aero Place • Suite 200 • San Diego, California 92123

Sales: (858) 571-4330 • Fax: (858) 571-6146 •Web: www.chassisplans.com

MX8 Technical Reference

Chassis Plans i

Table of Contents

Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-2

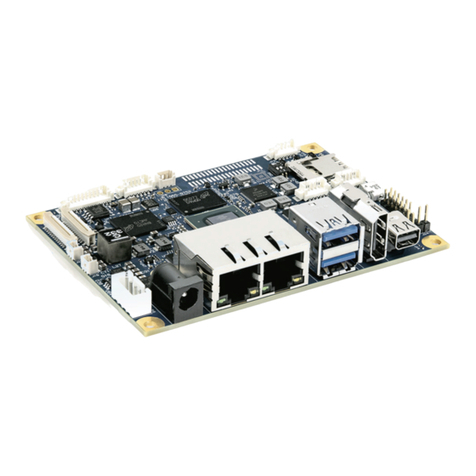

SBC Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-4

SBC Board Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-5

Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

Bus Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

Data Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

Bus Speed - PCI and PCI-X . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

Bus Speed - System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

System Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

DMA Channels. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

BIOS (Flash). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

Cache Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

NetBurst Micro-Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-7

DDR Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-7

Error Checking and Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-8

ISA Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-8

PCI-X/PCI Local Bus Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . .1-8

Universal Serial Bus (USB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-8

Ultra XGA Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-8

System Hardware Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-8

PCI Ethernet Interfaces (Dual) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-9

Hub Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-10

PCI SCSI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-10

Serial ATA/150 Ports (Dual) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-10

PCI Enhanced IDE Interfaces (Dual) . . . . . . . . . . . . . . . . . . . . . . . .1-10

Floppy Drive Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-10

Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-10

Enhanced Parallel Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-10

PS/2 Mouse Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-11

Keyboard Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-11

Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-11

MX8 Technical Reference

Chassis Plansii

Table of Contents

Specifications (continued)

Power Fail Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-11

Battery . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-11

Power Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-12

Temperature/Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-12

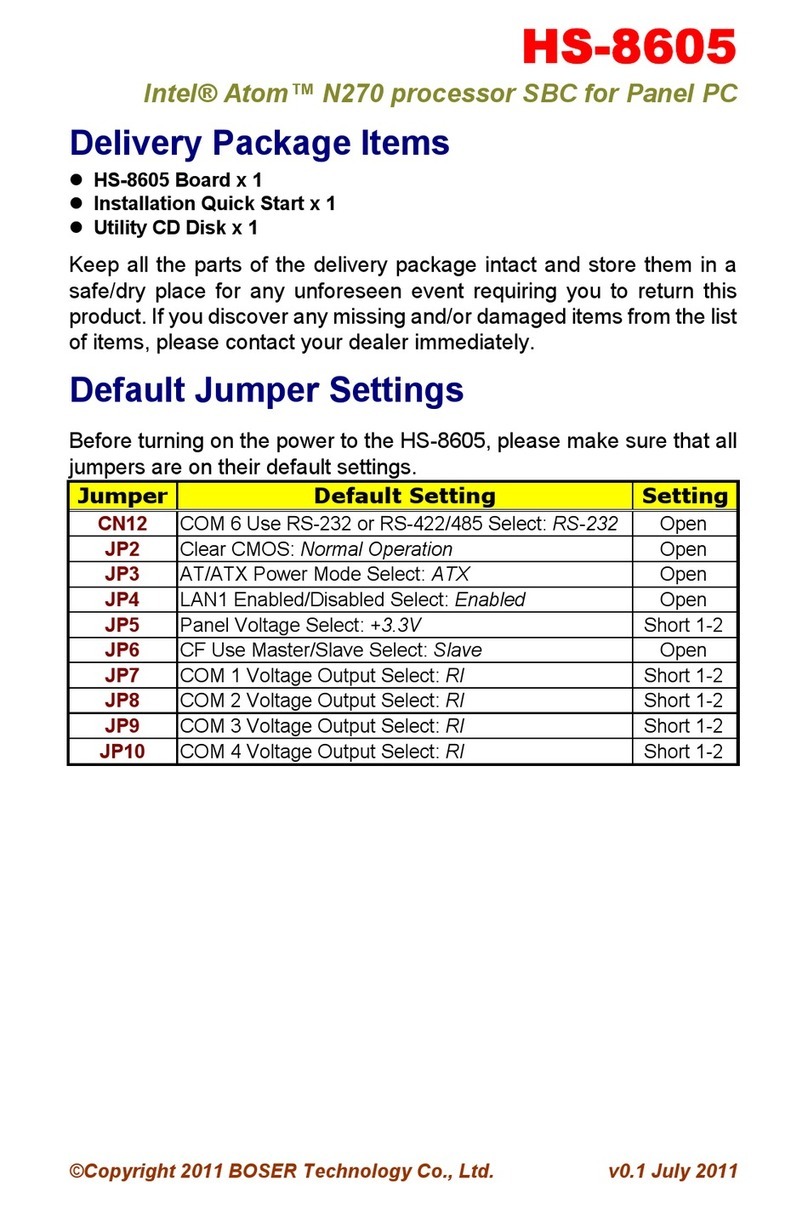

Configuration Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-13

Ethernet LEDs and Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-14

System BIOS Setup Utility. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-15

Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-16

ISA/PCI Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

ISA Bus Pin Numbering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

ISA Bus Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

ISA Bus Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

I/O Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

Interrupt Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

PCI Local Bus Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

PCI Local Bus Signal Definition . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

PCI Local Bus Pin Numbering. . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

PCI Local Bus Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

PCI Local Bus Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . .2-14

PICMG Edge Connector Pin Assignments . . . . . . . . . . . . . . . . . . .2-18

System BIOS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

BIOS Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

Password Entry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-2

BIOS Errors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-4

Running AMIBIOS Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-5

BIOS Setup Utility Main Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-6

BIOS Setup Utility Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-7

Security Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-11

Change Supervisor Password . . . . . . . . . . . . . . . . . . . . . . . . . . .3-11

Disabling Supervisor Password. . . . . . . . . . . . . . . . . . . . . . . . . .3-14

Change User Password . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-14

Clear User Password . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-14

Boot Sector Virus Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . .3-14

Exit Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-17

MX8 Technical Reference

Chassis Plans iii

Table of Contents

Advanced Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

CPU Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-5

IDE Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-7

IDE Device Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-13

Floppy Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-17

SuperIO Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-19

Remote Access Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-23

USB Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-25

PCI Plug and Play Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

Boot Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-1

Boot Settings Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3

Boot Device Priority. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-7

Hard Disk Drives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-9

Removable Drives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-11

CD/DVD Drives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-13

Chipset Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-1

NorthBridge Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-3

SouthBridge Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-9

Appendix A - BIOS Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-1

BIOS Beep Codes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-1

BIOS Error Messages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-2

Bootblock Initialization Code Checkpoints . . . . . . . . . . . . . . . . . . .A-6

Bootblock Recovery Code Checkpoints. . . . . . . . . . . . . . . . . . . . . .A-7

Post Code Checkpoints. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-8

DIM Code Checkpoints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-10

Additional Checkpoints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-11

MX8 Technical Reference

Chassis Plansiv

This page intentionally left blank.

Copyright 2004 by Trenton Technology Inc. All rights reserved.

MX8 Technical Reference

Chassis Plans v

HANDLING

PRECAUTIONS

_______________________________________________________________________

WA R N I N G: This product has components which may be damaged by electrostatic

discharge.

_______________________________________________________________________

To protect your single board computer (SBC) from electrostatic damage, be sure to

observe the following precautions when handling or storing the board:

•Keep the SBC in its static-shielded bag until you are ready to perform your

installation.

•Handle the SBC by its edges.

•Do not touch the I/O connector pins. Do not apply pressure or attach labels

to the SBC.

•Use a grounded wrist strap at your workstation or ground yourself

frequently by touching the metal chassis of the system before handling any

components. The system must be plugged into an outlet that is connected to

an earth ground.

•Use antistatic padding on all work surfaces.

•Avoid static-inducing carpeted areas.

SOLDER-SIDE

COMPONENTS

This SBC has components on both sides of the PCB. It is important for you to observe

the following precautions when handling or storing the board to prevent solder-side

components from being damaged or broken off:

•Handle the board only by its edges.

•Store the board in padded shipping material or in an anti-static board rack.

•Do not place an unprotected board on a flat surface.

MX8 Technical Reference

Chassis Plansvi

This page intentionally left blank.

Copyright 2004 by Trenton Technology Inc. All rights reserved.

Before You BeginMX8 Technical Reference

Chassis Plans

Before You Begin

INTRODUCTION It is important to be aware of the system considerations listed below before installing

your MX8 SBC. Overall system performance may be affected by incorrect usage of

these features.

MOUSE/KEYBOARD

“Y” CABLE

When using a “Y” cable attached to the bracket mounted mouse/keyboard mini Din

connector, be sure to use Chassis Plans’ “Y” cable, part number 5886-000. Using a non-

Chassis Plans cable may result in improper SBC operation.

DDR MEMORY The memory modules used in the MX8 may be PC2100, PC2700 or PC3200 ECC or

non-ECC, unbuffered DIMMs. If two modules of different speeds are used, the DIMMs

will operate in dual-channel mode at the speed of the slowest DIMM. If the modules are

different sizes, they will operate in single-channel mode. Registered DIMMs are not

supported. All memory modules must have gold contacts.

In addition, the DIMMs must have the following features:

•184-pin with gold-plated contacts

•ECC (72-bit) or non-ECC (64-bit) DDR memory

•Unbuffered configuration

BOOT FROM LAN The MX8 supports bootup from a LAN device. If you are not booting from a LAN

device, the boot from LAN options on the Boot Device Priority screen should always be

set to Disabled to eliminate unnecessary delays during the bootup process. This may be

done via the Boot Device Priority option on the Boot Setup screen of the BIOS Setup

Utility.

POWER

REQUIREMENTS

The following are typical values:

______________________________________________________________________

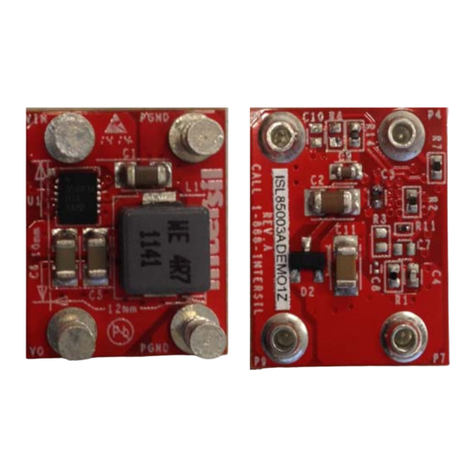

NOTE: The MX8 requires an additional on-board power connector due to the power

requirements of the Intel®Pentium®4 processor. This 4-pin connector (P24) requires

+12V from an external power supply that conforms to the ATX12V power specification.

The external power supply must have a wattage rating of 250W or higher.

Processor

Speed +5V * +12V ** +3.3V * -12V *

Intel®Pentium®4 Processor - 533MHz FSB/512K cache:

2.8GHz

2.4GHz

4.95 Amps

4.95 Amps

4.63 Amps

5.00 Amps

2.50 Amps

2.50 Amps

< 100 mAmps

< 100 mAmps

Intel®Celeron®Processor - 400MHz FSB/128K cache:

2.5GHz

2.0GHz

4.95 Amps

4.95 Amps

4.60 Amps

4.20 Amps

2.50 Amps

2.50 Amps

< 100 mAmps

< 100 mAmps

* From backplane via PICMG connector.

** From ATX12V power supply or equivalent via P24 connector.

Before You Begin MX8 Technical Reference

Chassis Plans

The MX8 also requires that +3.3V must be applied to the backplane from the power

supply, as specified in the PCI Industrial Computer Manufacturers Group (PICMG®)1.0

Specification. When using a backplane which is not a Chassis Plans product, check with

your backplane manufacturer to ensure that the backplane provides +3.3V to the SBC.

______________________________________________________________________

OPERATING

TEMPERATURE

Adequate airflow is essential to ensure effective operation of the MX8. The following

are operating temperature requirements:

0ºC. to 45ºC.

0ºC. to 45ºC. with 250 LFM of airflow (for processors with 800MHz FSB/1M

cache and 3.06GHz processor with 533MHz FSB/512K cache)

HYPER-THREADING The factory setting of the HyperThreading option in the system BIOS is Disabled.

This option may be set to Enabled for processors which support Hyper-Threading

functionality.

Hyper-Threading improves overall performance in many systems designed for multi-

processing, high-demand multi-tasking and multi-threaded applications. If you are using

a system which can take advantage of Hyper-Threading technology, you may use the

BIOS Setup Utility to change the setting of the HyperThreading option to Enabled.

This option is found on the CPU Configuration screen in the Advanced Setup section of

the BIOS Setup Utility.

Intel®recommends enabling Hyper-Threading on systems that use Microsoft®

Windows®XP®or Linux®2.4.x operating systems.

For systems which use applications and operating systems which cannot take advantage

of Hyper-Threading technology, the HyperThreading option should remain Disabled.

Intel recommends disabling Hyper-Threading when using the following operating

systems: Microsoft Windows 98®, Windows NT®, Windows 2000®, Windows ME®,

IBM®OS/2®and any version of Linux before revision 2.4.x. These operating systems

are not optimized for Hyper-Threading technology and some applications may actually

experience some performance degradation.

FOR MORE

INFORMATION

For more information on any of these features, refer to the appropriate sections of the

MX8 Technical Reference Manual (#87-006243-000). The latest revision of this manual

may be found on Chassis Plans’ website - www.chassisplans.com.

Copyright 2004 by Trenton Technology Inc. All rights reserved.

SpecificationsMX8 Technical Reference

Chassis Plans 1-1

Chapter 1 Specifications

INTRODUCTION The MX8 full-featured PCI/ISA processors are single board computers (SBCs) which

feature the Intel®Pentium®4 or Intel®Celeron®microprocessor, 400/533/800MHz

system bus, ATI Technologies®video interface, support for 2GB DDR memory, PCI

Local Bus, cache memory, floppy controller, dual Ultra ATA/100 EIDE interfaces,

optional Ultra160 SCSI controller, dual Gigabit Ethernet interfaces, dual Serial ATA

ports, two serial ports, parallel port, speaker port and mouse/keyboard port on a single

ISA-size card. These single-slot high performance SBCs plug into PICMG®PCI/ISA

and PCI-X backplanes and provide full PC compatibility for the system expansion slots.

The MX8-NS models have all of the standard features of the MX8, except they do not

include the Adaptec SCSI controller or the Ultra160 SCSI port.

MODELS

Model # Model Name Speed

Intel®Pentium®4 Processor - 800MHz FSB/1M cache:

S6240-409-xM

S6240-408-xM

S6240-407-xM

MX8/3.2G1

MX8/3.0G1

MX8/2.8G1

3.2GHz

3.0GHz

2.8GHz

Intel®Pentium®4 Processor - 533MHz FSB/512K cache:

S6240-108-xM

S6240-107-xM

S6240-106-xM

S6240-105-xM

S6240-104-xM

MX8/3.06EN

MX8/2.8EN

MX8/2.66EN

MX8/2.53EN

MX8/2.4EN

3.06GHz

2.8GHz

2.66GHz

2.53GHz

2.4GHz

Intel®Celeron®Processor - 400MHz FSB/128K cache:

S6240-807-xM

S6240-806-xM

S6240-805-xM

S6240-804-xM

S6240-803-xM

S6240-802-xM

S6240-801-xM

S6240-800-xM

MX8/2.5C

MX8/2.4C

MX8/2.3C

MX8/2.2C

MX8/2.1C

MX8/2.0C

MX8/1.8C

MX8/1.7C

2.5GHz

2.4GHz

2.3GHz

2.2GHz

2.1GHz

2.0GHz

1.8GHz

1.7GHz

“No SCSI” Models:

Intel®Pentium®4 Processor - 800MHz FSB/1M cache:

S6240-429-xM

S6240-428-xM

S6240-427-xM

MX8/3.2G1-NS

MX8/3.0G1-NS

MX8/2.8G1-NS

3.2GHz

3.0GHz

2.8GHz

Intel®Pentium®4 Processor - 533MHz FSB/512K cache:

S6240-128-xM

S6240-127-xM

S6240-126-xM

S6240-125-xM

S6240-124-xM

MX8/3.06EN-NS

MX8/2.8EN-NS

MX8/2.66EN-NS

MX8/2.53EN-NS

MX8/2.4EN-NS

3.06GHz

2.8GHz

2.66GHz

2.53GHz

2.4GHz

Specifications MX8 Technical Reference

Chassis Plans1-2

MODELS

(CONTINUED)

where xM indicates memory size (0M = 0MB memory,

64M =64MB memory, etc.)

FEATURES •Intel®Pentium®4 microprocessor

•3.2GHz, 3.0GHz or 2.8GHz with 1M cache and a 800MHz Front Side Bus

(FSB)

•3.06GHz, 2.8GHz, 2.66GHz, 2.53GHz or 2.4GHz with 512K cache and a

533MHz FSB

or Intel®Celeron®microprocessor

•2.5GHz, 2.4GHz, 2.3GHz, 2.2GHz, 2.1GHz, 2.0GHz, 1.8GHz or 1.7GHz

with 128K cache and a 400MHz FSB

•Intel 875P chipset with 400/533/800MHz system bus

•PCI Local Bus operating in 32-bit/33MHz mode

•Ultra XGA on-board video interface (ATI Technologies®)

•Supports off-board PCI option cards, dual PCI 10/100/1000Base-T Ethernet

controllers and optional on-board PCI Ultra160 SCSI controller - Adaptec

AIC-7892

•Dual Ethernet interfaces for use with 10/100/1000Base-T networks

•Dual Serial ATA ports support two independent SATA storage devices

•Memory error checking and correction (ECC) support

•Compatible with PCI Industrial Computer Manufacturers Group (PICMG) 1.0

Specification

•Supports up to 2GB of Double Data Rate (DDR) on-board memory

•Floppy drive and dual PCI EIDE Ultra ATA/100 drive interfaces

•Two serial ports and one parallel port

•Dual Universal Serial Bus (USB 2.0) support

•Automatic or manual peripheral configuration

Model # Model Name Speed

“No SCSI” Models (continued):

Intel®Celeron®Processor - 400MHz FSB/128K cache:

S6240-827-xM

S6240-826-xM

S6240-825-xM

S6240-824-xM

S6240-823-xM

S6240-822-xM

S6240-821-xM

S6240-820-xM

MX8/2.5C-NS

MX8/2.4C-NS

MX8/2.3C-NS

MX8/2.2C-NS

MX8/2.1C-NS

MX8/2.0C-NS

MX8/1.8C-NS

MX8/1.7C-NS

2.5GHz

2.4GHz

2.3GHz

2.2GHz

2.1GHz

2.0GHz

1.8GHz

1.7GHz

SpecificationsMX8 Technical Reference

Chassis Plans 1-3

FEATURES

(CONTINUED)

•Watchdog timer

•System hardware monitor

•Full PC compatibility

Specifications MX8 Technical Reference

Chassis Plans1-4

SBC BLOCK

DIAGRAM

SpecificationsMX8 Technical Reference

Chassis Plans 1-5

SBC BOARD

LAYOUT

Specifications MX8 Technical Reference

Chassis Plans1-6

PROCESSOR •Intel®Pentium®4 microprocessor

•3.2GHz, 3.0GHz or 2.8GHz with 1M cache and a 800MHz Front Side Bus

(FSB)

•3.06GHz, 2.8GHz, 2.66GHz, 2.53GHz or 2.4GHz with 512K cache and a

533MHz FSB

or Intel®Celeron®microprocessor

•2.5GHz, 2.4GHz, 2.3GHz, 2.2GHz, 2.1GHz, 2.0GHz, 1.8GHz or 1.7GHz

with 128K cache and a 400MHz FSB

•Processor uses the mPGA 478 packaging

BUS INTERFACES ISA and PCI Local Bus compatible

DATA PATH DDR Memory - 64-bit (per channel)

PCI Bus - 32-bit or 64-bit

PCI-X Bus - 64-bit

BUS SPEED - PCI

AND PCI-X

PCI - 33MHz or 66MHz

PCI-X - 33MHz or 66MHz

BUS SPEED -

SYSTEM

400/533/800MHz Front Side Bus

MEMORY

INTERFACE

Dual Double Data Rate (DDR) memory channels for 2100MB/s, 2700MB/s or

3200MB/s memory bandwidth

SYSTEM BUS The Intel 875P chipset supports the system bus at 400MHz, 533MHz or 800MHz, which

provides a higher bandwidth path for transferring data between main memory/chipset

and the processor.

DMA CHANNELS The SBC is fully PC compatible with seven DMA channels, each supporting type F

transfers.

INTERRUPTS The SBC is fully PC compatible with interrupt steering for PCI plug and play compati-

bility.

BIOS (FLASH)The BIOS is an AMIBIOS with built-in advanced CMOS setup for system parameters,

peripheral management for configuring on-board peripherals and other system param-

eters. The Flash BIOS resides in the Intel 82802AC Firmware Hub (FWH). The BIOS

may be upgraded from floppy disk by pressing <Ctrl> + <Home> immediately after

reset or power-up with the floppy disk in drive A:. Custom BIOSs are available.

CACHE MEMORY The processor includes integrated on-die, 1MB 8-way set associative level two (L2)

cache, which implements the Advanced Transfer Cache architecture and runs at the full

speed of the processor core. Intel®Pentium®4 processors provide either 512K or 1M of

L2 cache memory; Intel®Celeron®processors have a 128K L2 cache.

SpecificationsMX8 Technical Reference

Chassis Plans 1-7

All processors include a 12K level 1 (L1) Execution Trace Cache. Processors which

have 1M of L2 cache memory have a 16K data cache; all other processors have an 8K

data cache.

NETBURST™

MICRO-

ARCHITECTURE

NetBurst micro-architecture defines the techniques Intel uses to enhance the processor’s

execution of the BIOS, operating system and application software. These techniques

include hyper-pipelined technology, a rapid execution engine, advanced dynamic

execution, enhanced floating point and multimedia unit and Streaming SIMD

Extensions 2 (SSE2). The processor’s system bus speed and memory cache are also part

of the NetBurst micro-architecture.

Hyper-pipelined technology doubles the pipeline depth inside the processor, which

enables more instructions to be loaded, resulting in higher core frequencies. Advanced

dynamic execution includes an improved speculative execution algorithm that minimizes

processor instruction misdirects and results in faster instruction execution.

The rapid execution engine enables the two arithmetic logic units (ALUs) of the

processor to operate at twice the core frequency. Many integer instructions can now

execute in half the internal core clock period, resulting in improved software execution

speeds.

NetBurst micro-architecture improvements in the floating point and multimedia unit

include making the registers 128 bits wide and adding a separate register for moving

data.

The SSE2 has 144 instructions which improve performance in secure transactions and

multimedia processing. These instructions are used for double-precision floating point,

SIMD integer and memory management improvements.

DDR MEMORY The Double Data Rate (DDR) memory interface supports up to 2GB of memory and can

operate as either a single-channel (64-bit) or dual-channel (128-bit) DDR interface. Each

of the channels terminates in a dual in-line memory module (DIMM) socket. Installing

two DIMMs doubles the interface bandwidth. The System BIOS automatically detects

memory type, size and speed.

The SBC uses industry standard 72-bit wide ECC or 64-bit wide non-ECC gold finger

PC2100, PC2700 or PC3200 memory modules in two 184-pin sockets.

______________________________________________________________________

NOTE: Memory modules can be installed in one or both DIMM sockets. If two

modules of different speeds are used, the DIMMs will operate in dual-channel mode at

the speed of the slowest DIMM. If the modules are different sizes, they will operate in

single-channel mode. Registered DIMMs are not supported. All memory modules must

have gold contacts.

______________________________________________________________________

The SBC supports DIMMs which are PC2100/PC2700/PC3200 compliant and have the

following features:

•184-pin with gold-plated contacts

•ECC (72-bit) or non-ECC (64-bit) DDR memory

•Unbuffered configuration

Specifications MX8 Technical Reference

Chassis Plans1-8

The following DIMM sizes are supported:

DIMM

Size DIMM Type ECC

64MB Unbuffered 8M x 72

128MB Unbuffered 16M x 72

256MB Unbuffered 32M x 72

512MB Unbuffered 64M x 72

1GB Unbuffered 128M x 72

ERROR CHECKING

AND CORRECTION

The memory interface supports ECC modes via BIOS setting for multiple-bit error

detection and correction of all errors confined to a single nibble.

ISA BUS

INTERFACE

The ISA bus interface supports legacy ISA slots, but does not support ISA Bus

Mastering, 16-bit I/O and 16-bit memory accesses. When a 16-bit access is executed to

the ISA bus, the transfer is divided into two 8-bit accesses. If the ISA option card being

used only operates in word (16-bit) mode, transfer data will be missed. If the ISA option

card supports both byte (8-bit) mode and word mode, the data transfer will be correct,

but performance will be reduced.

PCI-X/PCI LOCAL

BUS INTERFACES

The SBC is fully compliant with the PCI Local Bus 2.1 Specification. The PCI Local

Bus is 32 bits wide and runs at 33MHz. It interfaces to one of the on-board 10/100/

1000Base-T Ethernet controllers (Intel 82540) and optional Ultra160 SCSI controller.

The PCI-X/PCI bus interface connects the SBC’s I/O Controller Hub directly to the

backplane and is capable of running at a 33MHz or 66MHz bus speed. This interface is

compliant with the PCI Industrial Computer Manufacturers Group (PICMG) 1.0 Specifi-

cation.

UNIVERSAL SERIAL

BUS (USB)

The SBC supports two high-speed USB 2.0 ports for data transfers up to 480Mbit/sec. It

also supports USB 1.1 devices for data transfers at 12 or 1.5Mbit/sec. The Universal

Serial Bus (USB) is an interface allowing for connectivity to many standard PC periph-

erals via an external port.

ULTRA XGA

INTERFACE

The ATI Technologies M6-C16H video controller enables 2D/3D video acceleration and

provides 16MB of integrated video DDR memory. The video controller’s DVI

compliant 165MHz TMDS transmitter supports pixel resolutions from VGA (640 x 480)

up to UXGA (1600 x 1200).

Software drivers are available for most popular operating systems.

SYSTEM

HARDWARE

MONITOR

The system hardware monitoring system monitors system voltages, temperature and fan

speeds.

The circuitry is based on Winbond’s W83783S hardware monitoring IC that is interfaced

via the system’s SMBus. System voltages of +12V, +5V, +3.3V, +2.5V, VCCORE

(processor voltage) and -12V are monitored. Each of these six voltages has program-

mable “high” and “low” watchdog limits. Also monitored are the processor die temper-

ature and the fan speed associated with the processor’s active heatsink thermal solution.

Programmable watchdog limits are also associated with fan speed RPMs. When any of

these programmed limits are exceeded, monitor software can be used to report the out-

of-limit condition.

Table of contents

Other Chassis Plans Motherboard manuals

Chassis Plans

Chassis Plans ATXR-QZ45Q Use and care manual

Chassis Plans

Chassis Plans ATXN-5520 Use and care manual

Chassis Plans

Chassis Plans ATXP-965Q Use and care manual

Chassis Plans

Chassis Plans ATXP-945G Use and care manual

Chassis Plans

Chassis Plans MTXP-945G Use and care manual

Chassis Plans

Chassis Plans ATXP-875P Use and care manual

Chassis Plans

Chassis Plans JXT6966 Use and care manual