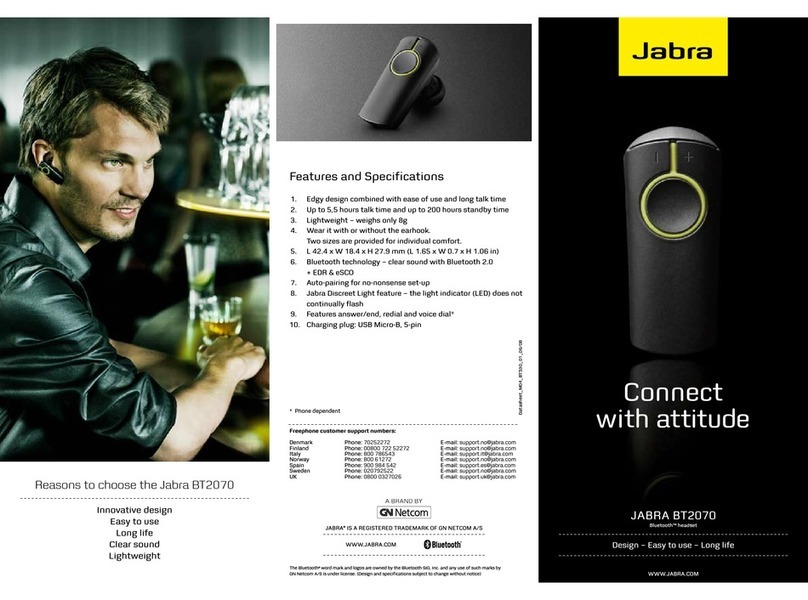

CSR BlueCore CSR8640 BGA User manual

Features BlueCore

®

CSR8640™ BGA

■

80MHz RISC MCU and 80MIPS Kalimba DSP

■

Internal ROM, serial flash memory and EEPROM

interfaces

■

Stereo codec with 2 microphone inputs

■

Radio includes integrated balun

■

5-band fully configurable EQ

■

CSR's latest CVC technology for narrow-band

and wideband voice connections including wind

noise reduction

■

HFP v1.6 includes wideband speech and mSBC

codec

■

Voice recognition support for answering a call,

enables true hands-free use

■

Multipoint HFP connection to 2 phones for voice

■

Multipoint A2DP connection enables a headset

(A2DP) connection to 2 A2DP source devices for

music playback

■

Secure simple pairing, CSR's proximity pairing

and CSR's proximity connection

■

Audio interfaces: I²S and PCM

■

Serial interfaces: UART, USB 2.0 (full-speed),

I²C and SPI

■

SBC, MP3 and AAC decoder support

■

Wired audio support (USB and analogue)

■

Support for smartphone/tablet applications

■

Integrated dual switch-mode regulators, linear

regulators and battery charger

■

External crystal load capacitors not required for

typical crystals

■

3 LED outputs

■

68‑ball VFBGA 5.5 x 5.5 x 1mm 0.5mm pitch

■

Green (RoHS compliant and no antimony or

halogenated flame retardants)

Stereo Headset Solution

Low-power Solution for

DSP Intensive Audio Applications

2-mic CVC Audio Enhancement

Fully Qualified Single-chip

Bluetooth

®

v3.0 System

Advance Information

CSR8640A03

Issue 1

2.4GHz

Radio

+

Balun

I/ OBT _RF

RAM

Baseband

MCU

Kalimba

DSP

ROMXTAL

Seri al Flash /

EEPROM

UART/USB

Audio In/Out

SPI/I

2

C

External Memory

PIO

General Description

The BlueCore® CSR8640™ BGA is a product from

CSR's Connectivity Centre. It is a single-chip radio and

baseband IC for Bluetooth 2.4GHz systems.

The integrated peripherals reduce the number of

external components required, including no

requirement for external codec, battery charger,

SMPS, LDOs, balun or external program memory,

ensuring minimum production costs.

The battery charger architecture enables the

CSR8640 BGA to independently operate from the

charger supply, ensuring dependable operation for all

battery conditions.

Applications

■

Stereo headsets

■

Wired stereo headsets and headphones

■

Portable stereo speakers

The enhanced Kalimba DSP coprocessor with

80MIPS supports enhanced audio and DSP

applications.

The integrated audio codec supports 2 channels of

ADC, 2 digital microphone inputs and stereo output, as

well as a variety of audio standards.

See

CSR Glossary

at www.csrsupport.com.

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 1 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA

Data Sheet

Device Details

Bluetooth Radio

■

On-chip balun (50Ω impedance in TX and RX

modes)

■

No trimming of external components required in

production

■

Bluetooth v3.0 specification compliant

Bluetooth Transmitter

■

9dBm RF transmit power with level control from on-

chip 6-bit DAC

■

Class 1, Class 2 and Class 3 support without the

need for an external power amplifier or TX/RX

switch

Bluetooth Receiver

■

Receiver sensitivity of -90dBm

■

Integrated channel filters

■

Digital demodulator for improved sensitivity and co-

channel rejection

■

Real-time digitised RSSI available to application

■

Fast AGC for enhanced dynamic range

■

Channel classification for AFH

Bluetooth Synthesiser

■

Fully integrated synthesiser requires no external

VCO, varactor diode, resonator or loop filter

■

Compatible with crystals 16MHz to 32MHz

Kalimba DSP

■

Enhanced Kalimba DSP coprocessor, 80MIPS,

24‑bit fixed point core

■

2 single-cycle MACs; 24 x 24-bit multiply and 56-bit

accumulator

■

32-bit instruction word, dual 24-bit data memory

■

6K x 32-bit program RAM including 1K instruction

cache for executing out of internal ROM

■

16K x 24-bit + 16K x 24-bit 2-bank data RAM

Audio Interfaces

■

Audio codec with 2 high-quality dedicated ADCs

■

Microphone bias generator and up to 2 analogue

microphone inputs

■

2 digital microphone inputs (MEMS)

■

Enhanced side-tone gain control

■

Supported sample rates of 8, 11.025, 16, 22.05, 32,

44.1, 48 and 96kHz (DAC only)

Auxiliary Features

■

Crystal oscillator with built-in digital trimming

Package Option

■

68‑ball VFBGA 5.5 x 5.5 x 1mm 0.5mm pitch

Physical Interfaces

■

UART interface for debug

■

USB 2.0 (full-speed) interface for audio and charger

enumeration

■

1-bit SPI flash memory interface

■

SPI interface for debug and programming

■

I²C interface for EEPROM

■

Up to 22 general purpose PIOs

■

PCM and I²S interfaces

■

3 LED drivers (includes RGB) with PWM flasher

independent of MCU

Integrated Power Control and Regulation

■

Automatic power switching to charger when present

■

2 high-efficiency switch-mode regulators with 1.8V

and 1.35V outputs direct from battery supply

■

3.3V linear regulator for USB supply

■

Low-voltage linear regulator for internal digital

circuits

■

Low-voltage linear regulator for internal analogue

circuits

■

Power-on-reset detects low supply voltage

■

Power management includes digital shutdown and

wake-up commands for ultra-low power modes

Battery Charger

■

Lithium ion / Lithium polymer battery charger

■

Instant-on function automatically selects the power

supply between battery and USB, which enables

operation even if the battery is fully discharged

■

Fast charging support up to 200mA with no external

components

■

Higher charge currents using external pass device

■

Supports USB charger detection

■

Support for thermistor protection of battery pack

■

Support to enable end product design to PSE law:

■

Design to JIS-C 8712/8714 (batteries)

■

Testing based on IEEE 1725

Baseband and Software

■

Internal ROM

■

Memory protection unit supporting accelerated VM

■

56KB internal RAM, enables full-speed data

transfer, mixed voice/data and full piconet support

■

Logic for forward error correction, header error

control, access code correlation, CRC,

demodulation, encryption bit stream generation,

whitening and transmit pulse shaping

■

Transcoders for A-law, µ-law and linear voice from

host and A-law, µ-law and CVSD voice over air

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 2 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA

Data Sheet

CSR8640 Stereo Headset Details

Bluetooth Profiles

■

Bluetooth v3.0 specification support

■

HFP v1.6 wideband speech (HD voice ready)

■

HSP v1.2

■

A2DP v1.2

■

AVRCP v1.4

■

Support for smartphone applications (apps)

Improved Audio Quality

CSR’s latest 2-mic CVC audio enhancements for

narrowband and wideband connections including:

■

2-mic far-end audio enhancements

■

Near-end audio enhancements (noise suppression

and AEQ)

■

Wind noise reduction

■

Packet loss concealment

■

Bit error concealment

■

Automatic gain control and automatic volume

control

■

Frequency expansion for improved speech

intelligibility

■

mSBC codec support for wideband speech

Music Enhancements

■

Configurable 5-band EQ for music playback (rock,

pop, classical, jazz, dance etc)

■

SBC, MP3, AAC and Faststream decoder

■

Stereo widening (S3D)

■

Volume Boost

Additional Functionality

■

Support for voice recognition

■

Support for multi-language programmable audio

prompts

■

CSR's proximity pairing and CSR's proximity

connection

■

Multipoint support for HFP connection to 2 handsets

for voice

■

Multipoint support for A2DP connection to 2 A2DP

sources for music playback

■

Talk-time extension

Headset Configurator Tool

Configures the CSR8640 stereo headset ROM software

features:

■

Bluetooth v3.0 specification features

■

Reconnection policies, e.g. reconnect on power-on

■

Audio features, including default volumes

■

Button events: configuring button presses and

durations for certain events, e.g. double press on

PIO for last number redial

■

LED indications for states, e.g. headset connected,

and events, power on etc.

■

Indication tones for events and ringtones

■

HFP v1.6 supported features

■

Battery divider ratios and thresholds, e.g.

thresholds for battery low indication, full battery etc.

■

Advanced Multipoint settings

CSR8640 Stereo Headset Development Kit

■

CSR8640 stereo headset demonstrator board

■

Music and voice dongle

■

Interface adapters and cables are available

■

Works in conjunction with the CSR8640 stereo

headset Configurator tool and other supporting

utilities

■

For order code details contact CSR

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 3 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA

Data Sheet

Functional Block Diagram

G-TW-0007440.4.3

Memory

Management

Unit

Bluetooth Modem

80MHz DSP

I2C/SPI

Master

/Slave

SPI

(Debug)

UART

4Mbps

System

RAM

Serial Flash

Interface

DMA ports

DMA ports

PCM1 / I2S

ROM

SPI_DEBUG Serial Flash

I2C

MIC_AN

UART

80MHz MCU

SPKR_LN

Audio

Interface

MIC_BIAS

USB v2.0

Full-speed

USB

3.3V

MIC Bias

Digital

Microphone

Inputs

(MEMS)

2 x Digital MICs

VM Accelerator

(MPU)

PMU

Interface

and

BIST

Engine

LED PWM

Control and

Output

PM

DM1

DM2

RGB

Digital Audio

1.35V

Switch-

mode

Regulator

Bypass

LDO

LXL_1V8

Li-ion

Charger

VCHG

1.8V

Switch-

mode

Regulator

LX_1V35

SMPS_1V8_SENSE

3V3_USB

Voltage / Temperature

Monitor

BT_RF

Clock

Generation AUX ADC

XTAL AIO[0]

MIC_AP

MIC_BN

MIC_BP

SPKR_LP

SPKR_RN

SPKR_RP

SENSE SENSE

Bluetooth

Baseband

Bluetooth Radio

and Balun

TX

RX

High-quality ADC

High-quality ADC

High-quality DAC

High-quality DAC

1.35V

Low-voltage

VDD_AUX

Linear

Regulator

1.35V

Low-voltage

VDD_ANA

Linear

Regulator

0.85V to

1.2V

Low-voltage

VDD_DIG

Linear

Regulator

DMA ports

VDD_AUX

SENSE

VDD_ANA_RADIO

SENSE

VDD_DIG_MEM

SENSE

CHG_EXT

Switch

SMPS_1V35_SENSE

SENSE

VBAT

VDD_AUX_1V8

VREGIN_DIG

PIO Port

PIO

PIO Port

VBAT_SENSE

VDD_AUDIO

VDD_AUDIO_DRV

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 4 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA Data Sheet

Document History

Revision Date Change Reason

113 JUL 11 Original publication of this document.

If you have any comments about this document, email [email protected] giving

number, title and section with your feedback.

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 5 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA Data Sheet

Status Information

The status of this Data Sheet is Advance Information.

CSR Product Data Sheets progress according to the following format:

Advance Information

Information for designers concerning CSR product in development. All values specified are the target values of the

design. Minimum and maximum values specified are only given as guidance to the final specification limits and must

not be considered as the final values.

All detailed specifications including pinouts and electrical specifications may be changed by CSR without notice.

Pre-production Information

Pinout and mechanical dimension specifications finalised. All values specified are the target values of the design.

Minimum and maximum values specified are only given as guidance to the final specification limits and must not be

considered as the final values.

All electrical specifications may be changed by CSR without notice.

Production Information

Final Data Sheet including the guaranteed minimum and maximum limits for the electrical specifications.

Production Data Sheets supersede all previous document versions.

Life Support Policy and Use in Safety-critical Applications

CSR's products are not authorised for use in life-support or safety-critical applications. Use in such applications is

done at the sole discretion of the customer. CSR will not warrant the use of its devices in such applications.

CSR Green Semiconductor Products and RoHS Compliance

CSR8640 BGA devices meet the requirements of Directive 2002/95/EC of the European Parliament and of the

Council on the Restriction of Hazardous Substance (RoHS).

CSR8640 BGA devices are also free from halogenated or antimony trioxide-based flame retardants and other

hazardous chemicals. For more information, see CSR's

Environmental Compliance Statement for CSR Green

Semiconductor Products

.

Trademarks, Patents and Licences

Unless otherwise stated, words and logos marked with ™ or ® are trademarks registered or owned by CSR plc or its

affiliates. Bluetooth ® and the Bluetooth ® logos are trademarks owned by Bluetooth ® SIG, Inc. and licensed to

CSR. Other products, services and names used in this document may have been trademarked by their respective

owners.

The publication of this information does not imply that any license is granted under any patent or other rights owned

by CSR plc and/or its affiliates.

CSR reserves the right to make technical changes to its products as part of its development programme.

While every care has been taken to ensure the accuracy of the contents of this document, CSR cannot accept

responsibility for any errors.

Refer to www.csrsupport.com for compliance and conformance to standards information.

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 6 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA Data Sheet

Contents

Device Details ................................................................................................................................................. 2

CSR8640 Stereo Headset Details .................................................................................................................. 3

Functional Block Diagram .............................................................................................................................. 4

1 Package Information ..................................................................................................................................... 13

1.1 Pinout Diagram .................................................................................................................................... 13

1.2 Pin Configuration ................................................................................................................................. 14

1.3 Device Terminal Functions .................................................................................................................. 15

1.4 Package Dimensions ........................................................................................................................... 21

1.5 PCB Design and Assembly Considerations ......................................................................................... 22

1.6 Typical Solder Reflow Profile ............................................................................................................... 22

2 Bluetooth Modem .......................................................................................................................................... 23

2.1 RF Ports ............................................................................................................................................... 23

2.1.1 BT_RF .................................................................................................................................... 23

2.2 RF Receiver ......................................................................................................................................... 23

2.2.1 Low Noise Amplifier ............................................................................................................... 23

2.2.2 RSSI Analogue to Digital Converter ....................................................................................... 23

2.3 RF Transmitter ..................................................................................................................................... 24

2.3.1 IQ Modulator .......................................................................................................................... 24

2.3.2 Power Amplifier ...................................................................................................................... 24

2.4 Bluetooth Radio Synthesiser ............................................................................................................... 24

2.5 Baseband ............................................................................................................................................. 24

2.5.1 Burst Mode Controller ............................................................................................................ 24

2.5.2 Physical Layer Hardware Engine ........................................................................................... 24

3 Clock Generation .......................................................................................................................................... 25

3.1 Clock Architecture ................................................................................................................................ 25

3.2 Input Frequencies and PS Key Settings .............................................................................................. 25

3.3 Crystal Oscillator: XTAL_IN and XTAL_OUT ....................................................................................... 25

3.3.1 Crystal Calibration .................................................................................................................. 25

3.3.2 Crystal Specification ............................................................................................................... 26

4 Bluetooth Stack Microcontroller .................................................................................................................... 27

4.1 VM Accelerator .................................................................................................................................... 27

5 Kalimba DSP ................................................................................................................................................ 28

6 Memory Interface and Management ............................................................................................................. 29

6.1 Memory Management Unit .................................................................................................................. 29

6.2 System RAM ........................................................................................................................................ 29

6.3 Kalimba DSP RAM .............................................................................................................................. 29

6.4 Internal ROM ....................................................................................................................................... 29

6.5 Serial Flash Interface ........................................................................................................................... 29

7 Serial Interfaces ............................................................................................................................................ 30

7.1 USB Interface ...................................................................................................................................... 30

7.2 UART Interface .................................................................................................................................... 30

7.3 Programming and Debug Interface ...................................................................................................... 32

7.3.1 Multi-slave Operation ............................................................................................................. 32

7.4 I²C EEPROM Interface ........................................................................................................................ 32

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 7 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA Data Sheet

8 Interfaces ...................................................................................................................................................... 34

8.1 Programmable I/O Ports, PIO .............................................................................................................. 34

8.2 Analogue I/O Ports, AIO ...................................................................................................................... 34

8.3 LED Drivers ......................................................................................................................................... 34

9 Audio Interface .............................................................................................................................................. 36

9.1 Audio Input and Output ........................................................................................................................ 37

9.2 Audio Codec Interface ......................................................................................................................... 37

9.2.1 Audio Codec Block Diagram .................................................................................................. 38

9.2.2 ADC ........................................................................................................................................ 38

9.2.3 ADC Sample Rate Selection .................................................................................................. 38

9.2.4 ADC Audio Input Gain ............................................................................................................ 39

9.2.5 ADC Pre-amplifier and ADC Analogue Gain .......................................................................... 39

9.2.6 ADC Digital Gain .................................................................................................................... 39

9.2.7 ADC Digital IIR Filter .............................................................................................................. 40

9.2.8 DAC ........................................................................................................................................ 40

9.2.9 DAC Sample Rate Selection .................................................................................................. 40

9.2.10 DAC Digital Gain .................................................................................................................... 40

9.2.11 DAC Analogue Gain ............................................................................................................... 41

9.2.12 DAC Digital FIR Filter ............................................................................................................. 41

9.2.13 Microphone Input ................................................................................................................... 42

9.2.14 Digital Microphone Inputs ....................................................................................................... 43

9.2.15 Line Input ............................................................................................................................... 43

9.2.16 Output Stage .......................................................................................................................... 44

9.2.17 Mono Operation ..................................................................................................................... 44

9.2.18 Side Tone ............................................................................................................................... 45

9.2.19 Integrated Digital IIR Filter ..................................................................................................... 46

9.3 PCM1 Interface .................................................................................................................................... 47

9.3.1 PCM Interface Master/Slave .................................................................................................. 48

9.3.2 Long Frame Sync ................................................................................................................... 49

9.3.3 Short Frame Sync .................................................................................................................. 49

9.3.4 Multi-slot Operation ................................................................................................................ 49

9.3.5 GCI Interface .......................................................................................................................... 50

9.3.6 Slots and Sample Formats ..................................................................................................... 50

9.3.7 Additional Features ................................................................................................................ 51

9.3.8 PCM Timing Information ........................................................................................................ 52

9.3.9 PCM_CLK and PCM_SYNC Generation ................................................................................ 55

9.3.10 PCM Configuration ................................................................................................................. 56

9.4 Digital Audio Interface (I²S) .................................................................................................................. 56

10 Power Control and Regulation ...................................................................................................................... 60

10.1 1.8V Switch-mode Regulator ............................................................................................................... 63

10.2 1.35V Switch-mode Regulator ............................................................................................................. 63

10.3 1.8V and 1.35V Switch-mode Regulators Combined .......................................................................... 64

10.4 Bypass LDO Linear Regulator ............................................................................................................. 65

10.5 Low-voltage VDD_DIG Linear Regulator ............................................................................................. 66

10.6 Low-voltage VDD_AUX Linear Regulator ............................................................................................ 66

10.7 Low-voltage VDD_ANA Linear Regulator ............................................................................................ 66

10.8 Voltage Regulator Enable .................................................................................................................... 66

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 8 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA Data Sheet

10.9 External Regulators and Power Sequencing ....................................................................................... 66

10.10Reset, RST# ........................................................................................................................................ 66

10.10.1 Digital Pin States on Reset .................................................................................................... 67

10.10.2 Status After Reset .................................................................................................................. 68

11 Battery Charger ............................................................................................................................................ 69

11.1 Battery Charger Hardware Operating Modes ...................................................................................... 69

11.1.1 Disabled Mode ....................................................................................................................... 70

11.1.2 Trickle Charge Mode .............................................................................................................. 70

11.1.3 Fast Charge Mode ................................................................................................................. 70

11.1.4 Standby Mode ........................................................................................................................ 70

11.1.5 Error Mode ............................................................................................................................. 70

11.2 Battery Charger Trimming and Calibration .......................................................................................... 71

11.3 VM Battery Charger Control ................................................................................................................ 71

11.4 Battery Charger Firmware and PS Keys .............................................................................................. 71

11.5 External Mode ...................................................................................................................................... 71

12 Example Application Schematic ................................................................................................................... 73

13 Electrical Characteristics .............................................................................................................................. 74

13.1 Absolute Maximum Ratings ................................................................................................................. 74

13.2 Recommended Operating Conditions .................................................................................................. 75

13.3 Input/Output Terminal Characteristics ................................................................................................. 76

13.3.1 Regulators: Available For External Use ................................................................................. 76

13.3.2 Regulators: For Internal Use Only .......................................................................................... 78

13.3.3 Regulator Enable ................................................................................................................... 79

13.3.4 Battery Charger ...................................................................................................................... 79

13.3.5 USB ........................................................................................................................................ 81

13.3.6 Clocks .................................................................................................................................... 81

13.3.7 Stereo Codec: Analogue to Digital Converter ........................................................................ 82

13.3.8 Stereo Codec: Digital to Analogue Converter ........................................................................ 83

13.3.9 Digital ..................................................................................................................................... 84

13.3.10 LED Driver Pads .................................................................................................................... 85

13.3.11 Auxiliary ADC ......................................................................................................................... 85

13.3.12 Auxiliary DAC ......................................................................................................................... 86

13.4 ESD Protection .................................................................................................................................... 87

14 Power Consumption ..................................................................................................................................... 88

15 CSR Green Semiconductor Products and RoHS Compliance ..................................................................... 90

16 Software ........................................................................................................................................................ 92

16.1 CSR8640 Stereo Headset ................................................................................................................... 92

16.1.1 Advanced Multipoint Support ................................................................................................. 93

16.1.2 A2DP Multipoint Support ........................................................................................................ 93

16.1.3 Wired Audio Mode .................................................................................................................. 93

16.1.4 USB Modes Including USB Audio Mode ................................................................................ 94

16.1.5 Smartphone Applications (Apps) ............................................................................................ 94

16.1.6 Programmable Audio Prompts ............................................................................................... 94

16.1.7 CSR’s Intelligent Power Management ................................................................................... 95

16.1.8 Proximity Pairing .................................................................................................................... 96

16.1.9 Proximity Connection ............................................................................................................. 96

16.2 6th Generation 2-mic CVC Audio Enhancements ................................................................................ 96

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 9 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA Data Sheet

16.2.1 Wind Noise Reduction ............................................................................................................ 97

16.2.2 Dual-microphone Signal Separation ...................................................................................... 97

16.2.3 Noise Suppression ................................................................................................................. 97

16.2.4 Acoustic Echo Cancellation .................................................................................................... 97

16.2.5 Comfort Noise Generator ....................................................................................................... 98

16.2.6 Equalisation ............................................................................................................................ 98

16.2.7 Automatic Gain Control .......................................................................................................... 98

16.2.8 Packet Loss Concealment ..................................................................................................... 98

16.2.9 Adaptive Equalisation ............................................................................................................. 98

16.2.10 Auxiliary Stream Mix .............................................................................................................. 98

16.2.11 Clipper .................................................................................................................................... 98

16.2.12 Noise Dependent Volume Control .......................................................................................... 99

16.2.13 Fixed Gains ............................................................................................................................ 99

16.2.14 Frequency Enhanced Speech Intelligibility ............................................................................ 99

16.3 Music Enhancements .......................................................................................................................... 99

16.3.1 Audio Decoders ...................................................................................................................... 99

16.3.2 Configurable EQ ................................................................................................................... 100

16.3.3 Stereo Widening (S3D) ........................................................................................................ 100

16.3.4 Volume Boost ....................................................................................................................... 101

16.4 CSR8640 Stereo Headset Development Kit ...................................................................................... 101

17 Ordering Information ................................................................................................................................... 102

17.1 CSR8640 Stereo Headset Development Kit Ordering Information .................................................... 102

18 Tape and Reel Information ......................................................................................................................... 103

18.1 Tape Orientation ................................................................................................................................ 103

18.2 Tape Dimensions ............................................................................................................................... 103

18.3 Reel Information ................................................................................................................................ 104

18.4 Moisture Sensitivity Level .................................................................................................................. 104

19 Document References ................................................................................................................................ 105

Terms and Definitions .......................................................................................................................................... 106

List of Figures

Figure 1.1 Device Pinout .................................................................................................................................. 13

Figure 1.1 Pin Configuration, Orientation from Top of Device .......................................................................... 14

Figure 2.1 Simplified Circuit BT_RF ................................................................................................................. 23

Figure 3.1 Clock Architecture ........................................................................................................................... 25

Figure 5.1 Kalimba DSP Interface to Internal Functions .................................................................................. 28

Figure 6.1 Serial Flash Interface ...................................................................................................................... 29

Figure 7.1 Universal Asynchronous Receiver .................................................................................................. 30

Figure 7.2 Example I²C EEPROM Connection ................................................................................................. 33

Figure 8.1 LED Equivalent Circuit .................................................................................................................... 35

Figure 9.1 Audio Interface ................................................................................................................................ 36

Figure 9.2 Audio Codec Input and Output Stages ............................................................................................ 38

Figure 9.3 Audio Input Gain ............................................................................................................................. 39

Figure 9.4 Microphone Biasing ......................................................................................................................... 42

Figure 9.5 Differential Input .............................................................................................................................. 43

Figure 9.6 Single-ended Input .......................................................................................................................... 44

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 10 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA Data Sheet

Figure 9.7 Speaker Output ............................................................................................................................... 44

Figure 9.8 Side Tone ........................................................................................................................................ 45

Figure 9.9 PCM Interface Master ..................................................................................................................... 48

Figure 9.10 PCM Interface Slave ....................................................................................................................... 48

Figure 9.11 Long Frame Sync (Shown with 8-bit Companded Sample) ............................................................ 49

Figure 9.12 Short Frame Sync (Shown with 16-bit Sample) .............................................................................. 49

Figure 9.13 Multi-slot Operation with 2 Slots and 8-bit Companded Samples ................................................... 50

Figure 9.14 GCI Interface ................................................................................................................................... 50

Figure 9.15 16-bit Slot Length and Sample Formats .......................................................................................... 51

Figure 9.16 PCM Master Timing Long Frame Sync ........................................................................................... 53

Figure 9.17 PCM Master Timing Short Frame Sync .......................................................................................... 53

Figure 9.18 PCM Slave Timing Long Frame Sync ............................................................................................. 55

Figure 9.19 PCM Slave Timing Short Frame Sync ............................................................................................ 55

Figure 9.20 Digital Audio Interface Modes ......................................................................................................... 57

Figure 9.21 Digital Audio Interface Slave Timing ............................................................................................... 58

Figure 9.22 Digital Audio Interface Master Timing ............................................................................................. 59

Figure 10.1 1.80V and 1.35V Dual-supply Switch-mode System Configuration ................................................ 61

Figure 10.2 1.80V Parallel-supply Switch-mode System Configuration ............................................................. 62

Figure 10.3 1.8V Switch-mode Regulator Output Configuration ........................................................................ 63

Figure 10.4 1.35V Switch-mode Regulator Output Configuration ...................................................................... 64

Figure 10.5 1.8V and 1.35V Switch-mode Regulators Outputs Parallel Configuration ...................................... 65

Figure 11.1 Battery Charger Mode-to-Mode Transition Diagram ....................................................................... 70

Figure 11.2 Battery Charger External Mode Typical Configuration .................................................................... 72

Figure 16.1 Programmable Audio Prompts in External SPI Flash ..................................................................... 95

Figure 16.2 Programmable Audio Prompts in External I²C EEPROM ................................................................ 95

Figure 16.3 2-mic CVC Block Diagram .............................................................................................................. 97

Figure 16.4 Configurable EQ GUI with Drag Points ......................................................................................... 100

Figure 16.5 Volume Boost GUI with Drag Points ............................................................................................. 101

Figure 18.1 Tape Orientation ........................................................................................................................... 103

Figure 18.2 Tape Dimensions .......................................................................................................................... 103

Figure 18.3 Reel Dimensions ........................................................................................................................... 104

List of Tables

Table 3.1 Crystal Specification ......................................................................................................................... 26

Table 7.1 Possible UART Settings ................................................................................................................... 31

Table 7.2 Standard Baud Rates ....................................................................................................................... 31

Table 8.1 Alternative PIO Functions ................................................................................................................. 34

Table 9.1 Alternative Functions of the Digital Audio Bus Interface on the PCM1 Interface ............................. 36

Table 9.2 ADC Audio Input Gain Rate ............................................................................................................. 40

Table 9.3 DAC Digital Gain Rate Selection ...................................................................................................... 41

Table 9.4 DAC Analogue Gain Rate Selection ................................................................................................. 41

Table 9.5 Sidetone Gain ................................................................................................................................... 46

Table 9.6 PCM Master Timing .......................................................................................................................... 52

Table 9.7 PCM Slave Timing ............................................................................................................................ 54

Table 9.8 Alternative Functions of the Digital Audio Bus Interface on the PCM Interface ............................... 56

Table 9.9 Digital Audio Interface Slave Timing ................................................................................................ 57

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 11 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA Data Sheet

Table 9.10 I²S Slave Mode Timing ..................................................................................................................... 58

Table 9.11 Digital Audio Interface Master Timing .............................................................................................. 59

Table 9.12 I²S Master Mode Timing Parameters, WS and SCK as Outputs ...................................................... 59

Table 10.1 Recommended Configurations for Power Control and Regulation ................................................... 60

Table 10.2 Pin States on Reset .......................................................................................................................... 67

Table 11.1 Battery Charger Operating Modes Determined by Battery Voltage and Current ............................. 69

Table 13.1 ESD Handling Ratings ...................................................................................................................... 87

Table 15.1 Chemical Limits for Green Semiconductor Products ........................................................................ 90

List of Equations

Equation 3.1 Crystal Calibration Using PSKEY_ANA_FTRIM_OFFSET .............................................................. 26

Equation 3.2 Example of PSKEY_ANA_FTRIM_OFFSET Value for 2402.0168MHz .......................................... 26

Equation 3.3 Example of PSKEY_ANA_FTRIM_OFFSET Value for 2401.9832MHz .......................................... 26

Equation 7.1 Baud Rate ....................................................................................................................................... 31

Equation 8.1 LED Current .................................................................................................................................... 35

Equation 8.2 LED PAD Voltage ............................................................................................................................ 35

Equation 9.1 IIR Filter Transfer Function, H(z) ..................................................................................................... 47

Equation 9.2 IIR Filter Plus DC Blocking Transfer Function, HDC(z) .................................................................... 47

Equation 9.3 PCM_CLK Frequency Generated Using the Internal 48MHz Clock ................................................ 56

Equation 9.4 PCM_SYNC Frequency Relative to PCM_CLK ............................................................................... 56

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 12 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA Data Sheet

1 Package Information

1.1 Pinout Diagram

G-TW-0007438.1.1

B

C

D

E

F

G

H

J

K

12345678910

Orientation from Top of Device

A

B10

K10

A10

C10

D10

E10

F10

G10

H10

J10

K1

A1

C1

D1

E1

F1

G1

H1

J1

B1

K2

A2

C2

D2

E2

F2

G2

H2

J2

B2

K3

A3

J3

B3

K4

A4

J4

B4

K5

A5

J5

B5

K8

A8

J8

B8

K9

A9

C9

D9

E9

F9

G9

H9

J9

B9

K6

A6

J6

B6

K7

A7

J7

B7

F5

E5

F6

E6

Figure 1.1: Device Pinout

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 13 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA Data Sheet

1.2 Pin Configuration

G-TW-0008090.2.3

VDD_AUX_1V8 VSS _ BT_LO _ AUX BT_ RF SPKR_ LP VSS _AUD IO SPKR _RP VDD_AUDIO AU_REF MIC_AP MIC_AN

XTAL _OUT VDD_AUX VSS _BT_ RF SPKR _ LN VDD_AUDIO_DRV SPKR _RN MIC_BP MIC_BN MIC_BIAS LED [2 ]

XTAL _ IN VDD _ANA _RAD IO PIO [19 ] PIO [20]

PIO [15] AIO [0 ] PIO [18 ] PIO [21]

PIO [4 ] PIO [12] VDD_PADS_1 VDD _PADS _2 PIO[ 6] PIO[ 8]

PIO [16 ] PIO [14] PIO [10 ] VSS_DIG PIO[ 0] PIO[ 1]

PIO [13 ] PIO [11] PIO[ 9] PIO[ 7]

PIO [2 ] PIO [17] SM PS _1V8 _SENSE USB_P

PIO [5 ] LED [0 ] RST# SPI _PCM# PIO [3 ] CHG_EXT VBAT_ SENSE VSS _SM PS _ 1V8 3V3_USB USB_N

LED [1 ] VDD_ DIG_MEM VREGIN _DIG VREGENABLE VCHG LX_ 1V 8 VBAT LX _ 1V35 VSS _SMPS _1 V35 SMPS_1V35_SENSE

1

A

B

C

D

E

F

G

H

J

K

234 5678910

A

B

C

D

E

F

G

H

J

K

12345678910

Figure 1.1: Pin Configuration, Orientation from Top of Device

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 14 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA

Data Sheet

1.3 Device Terminal Functions

Radio Ball Pad Type Supply Domain Description

BT_RF A3 RF VDD_ANA_RADIO Bluetooth 50Ω transmitter output /

receiver input

Oscillator Ball Pad Type Supply Domain Description

XTAL_IN C1

Analogue VDD_AUX

For crystal or external clock input

XTAL_OUT B1 Drive for crystal

USB Ball Pad Type Supply Domain Description

USB_P H10

Bidirectional 3V3_USB

USB data plus with selectable internal

1.5kΩ pull-up resistor

USB_N J10 USB data minus

SPI/PCM Interface Ball Pad Type Supply Domain Description

SPI_PCM# J4 Input with weak pull-

down VDD_PADS_1

SPI/PCM# select input:

■ 0 = PCM/PIO interface

■ 1 = SPI

Note:

SPI and PCM1 interfaces are mapped as alternative functions on the PIO port.

PIO Port Ball Pad Type Supply Domain Description

PIO[21] D10 Bidirectional with weak

pull-down VDD_PADS_2 Programmable input / output line 21.

PIO[20] C10 Bidirectional with weak

pull-down VDD_PADS_2 Programmable input / output line 20.

PIO[19] C9 Bidirectional with weak

pull-down VDD_PADS_2 Programmable input / output line 19.

PIO[18] D9 Bidirectional with weak

pull-down VDD_PADS_2 Programmable input / output line 18.

PIO[17] H2 Bidirectional with strong

pull-down VDD_PADS_1

Programmable input / output line 17.

Alternative functions:

■ UART_CTS: UART clear to send,

active low

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 15 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA

Data Sheet

PIO Port Ball Pad Type Supply Domain Description

PIO[16] F1 Bidirectional with strong

pull-up VDD_PADS_1

Programmable input / output line 16.

Alternative functions:

■ UART_RTS: UART request to

send, active low

PIO[15] D1 Bidirectional with strong

pull-up VDD_PADS_1

Programmable input / output line 15.

Alternative functions:

■ UART_TX: UART data output

PIO[14] F2 Bidirectional with strong

pull-up VDD_PADS_1

Programmable input / output line 14.

Alternative functions:

■ UART_RX: UART data input

PIO[13] G1 Bidirectional with strong

pull-down VDD_PADS_1

Programmable input / output line 13.

Alternative function:

■ QSPI_IO[1]: serial quad I/O flash

data bit 1

PIO[12] E2 Bidirectional with strong

pull-up VDD_PADS_2

Programmable input / output line 12.

Alternative function:

■ QSPI_FLASH_CS#: serial quad

I/O flash chip select

■ I2C_WP: I²C bus memory write

protect line

PIO[11] G2 Bidirectional with strong

pull-down VDD_PADS_1

Programmable input / output line 11.

Alternative function:

■ QSPI_IO[0]: serial quad I/O flash

data bit 0

■ I2C_SDA: I²C serial data line

PIO[10] F5 Bidirectional with strong

pull-down VDD_PADS_1

Programmable input / output line 10.

Alternative function:

■ QSPI_FLASH_CLK: serial quad

I/O flash clock

■ I2C_SCL: I²C serial clock line

PIO[9] G9 Bidirectional with strong

pull-down VDD_PADS_2 Programmable input / output line 9.

PIO[8] E10 Bidirectional with strong

pull-up VDD_PADS_2 Programmable input / output line 8.

PIO[7] G10 Bidirectional with strong

pull-down VDD_PADS_2 Programmable input / output line 7.

PIO[6] E9 Bidirectional with strong

pull-down VDD_PADS_2 Programmable input / output line 6.

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 16 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA

Data Sheet

PIO Port Ball Pad Type Supply Domain Description

PIO[5] J1 Bidirectional with weak

pull-down VDD_PADS_1

Programmable input / output line 5.

Alternative functions:

■ SPI_CLK: SPI clock

■ PCM1_CLK: PCM1 synchronous

data clock

PIO[4] E1 Bidirectional with weak

pull-down VDD_PADS_1

Programmable input / output line 4.

Alternative functions:

■ SPI_CS#: chip select for SPI, active

low

■ PCM1_SYNC: PCM1 synchronous

data sync

PIO[3] J5 Bidirectional with weak

pull-down VDD_PADS_1

Programmable input / output line 3.

Alternative functions:

■ SPI_MISO: SPI data output

■ PCM1_OUT: PCM1 synchronous

data output

PIO[2] H1 Bidirectional with weak

pull-down VDD_PADS_1

Programmable input / output line 2.

Alternative functions:

■ SPI_MOSI: SPI data input

■ PCM1_IN: PCM1 synchronous data

input

PIO[1] F10 Bidirectional with strong

pull-up VDD_PADS_2 Programmable input / output line 1.

PIO[0] F9 Bidirectional with strong

pull-up VDD_PADS_2 Programmable input / output line 0.

AIO[0] D2 Bidirectional VDD_AUX Analogue programmable input / output

line 0.

Test and Debug Ball Pad Type Supply Domain Description

RST# J3 Input with strong pull-up VDD_PADS_1 Reset if low. Pull low for minimum 5ms to

cause a reset.

Codec Ball Pad Type Supply Domain Description

MIC_AP A9

Analogue in VDD_AUDIO

Microphone input positive, channel A

MIC_AN A10 Microphone input negative, channel A

MIC_BP B7

Analogue in VDD_AUDIO

Microphone input positive, channel B

MIC_BN B8 Microphone input negative, channel B

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 17 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA

Data Sheet

Codec Ball Pad Type Supply Domain Description

MIC_BIAS B9 Analogue out VBAT / 3V3_USB Microphone bias

SPKR_LP A4

Analogue out VDD_AUDIO_DRV

Speaker output positive, left

SPKR_LN B4 Speaker output negative, left

SPKR_RP A6

Analogue out VDD_AUDIO_DRV

Speaker output positive, right

SPKR_RN B6 Speaker output negative, right

AU_REF A8 Analogue in VDD_AUDIO Decoupling of audio reference (for high-

quality audio)

LED Drivers Ball Pad Type Supply Domain Description

LED[2] B10

Bidirectional VDD_PADS_1

LED driver.

Alternative function: programmable

output PIO[31]

Note:

As output is open-drain, an external

pull-up is required when PIO[31] is

configured as a programmable

output.

LED[1] K1

LED driver.

Alternative function: programmable

output PIO[30].

Note:

As output is open-drain, an external

pull-up is required when PIO[30] is

configured as a programmable

output.

LED[0] J2

LED driver.

Alternative function: programmable

output PIO[29].

Note:

As output is open-drain, an external

pull-up is required when PIO[29] is

configured as a programmable

output.

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 18 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA

Data Sheet

Power Supplies and Control Ball Description

3V3_USB J9

3.3V bypass linear regulator output

Positive supply for USB port

Connect external minimum 2.2µF ceramic decoupling capacitor

CHG_EXT J6

External battery charger control

External battery charger transistor base control when using

external charger boost. Otherwise leave unconnected.

LX_1V35 K8 1.35V switch-mode power regulator inductor connection

LX_1V8 K6 1.8V switch-mode power regulator inductor connection

SMPS_1V35_SENSE K10 1.35V switch-mode power regulator sense input

SMPS_1V8_SENSE H9 1.8V switch-mode power regulator sense input

VBAT K7 Battery positive terminal

VBAT_SENSE J7 Battery charger sense input

Connect directly to the battery positive pin.

VCHG K5 Charger input

Typically connected to VBUS (USB supply) as Section 12 shows

VDD_ANA_RADIO C2 Bluetooth radio supply

Connect to 1.35V supply, see Section 12 for connections

VDD_AUDIO A7 Positive supply for audio

Connect to 1.35V supply, see Section 12 for connections

VDD_AUDIO_DRV B5 Positive supply for audio output amplifiers

Connect to 1.8V supply

VDD_AUX B2 Auxiliary supply

Connect to 1.35V supply, see Section 12 for connections

VDD_AUX_1V8 A1 Auxiliary LDO regulator input

Connect to 1.8V supply, see Section 12 for connections

VDD_DIG_MEM K2 Digital LDO regulator output, see Section 12 for connections

VDD_PADS_1 E5 1.8V positive supply input for input/output ports

VDD_PADS_2 E6 1.8V positive supply input for input/output ports

VREGENABLE K4

Regulator enable input.

Can also be sensed as an input.

Regulator enable and multifunction button. A high input (tolerant to

VBAT) enables the on-chip regulators, which can then be latched

on internally and the button used as a multifunction input.

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 19 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA

Data Sheet

Power Supplies and Control Ball Description

VREGIN_DIG K3 Digital LDO regulator input, see Section 12 for connections

Connect to a 1.35V supply

VSS_AUDIO A5 Ground connection for audio and audio driver

VSS_BT_LO_AUX A2 Ground connections for analogue circuitry and Bluetooth radio local

oscillator

VSS_BT_RF B3 Bluetooth radio ground

VSS_DIG F6 Ground connection for internal digital circuitry

VSS_SMPS_1V35 K9 1.35V switch-mode regulator ground

VSS_SMPS_1V8 J8 1.8V switch-mode regulator ground

Advance Information

This material is subject to CSR's non-disclosure agreement

© Cambridge Silicon Radio Limited 2011

Page 20 of 110

CS-209182-DSP1

www.csr.com

CSR8640 BGA

Data Sheet

Table of contents

Other CSR Headset manuals