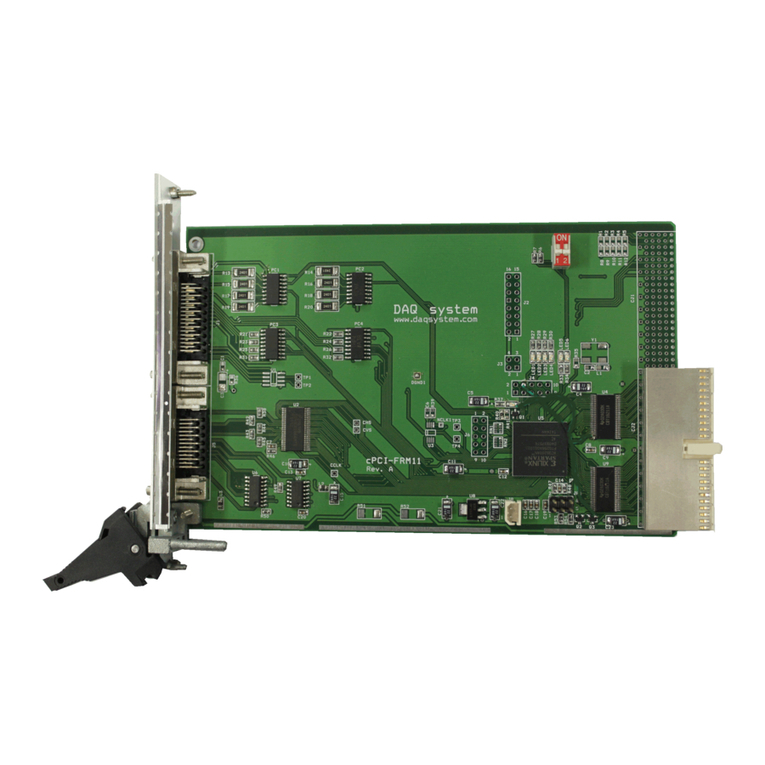

DAQ PCI-FRM01 User guide

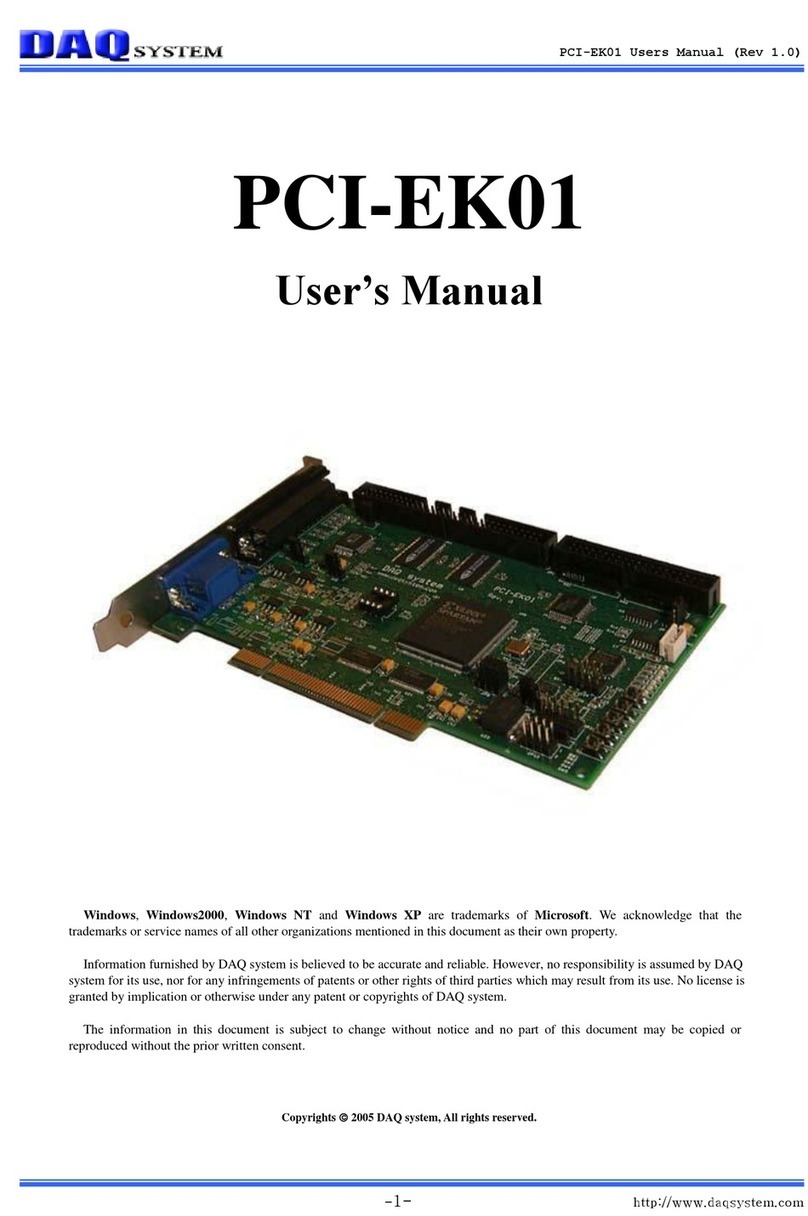

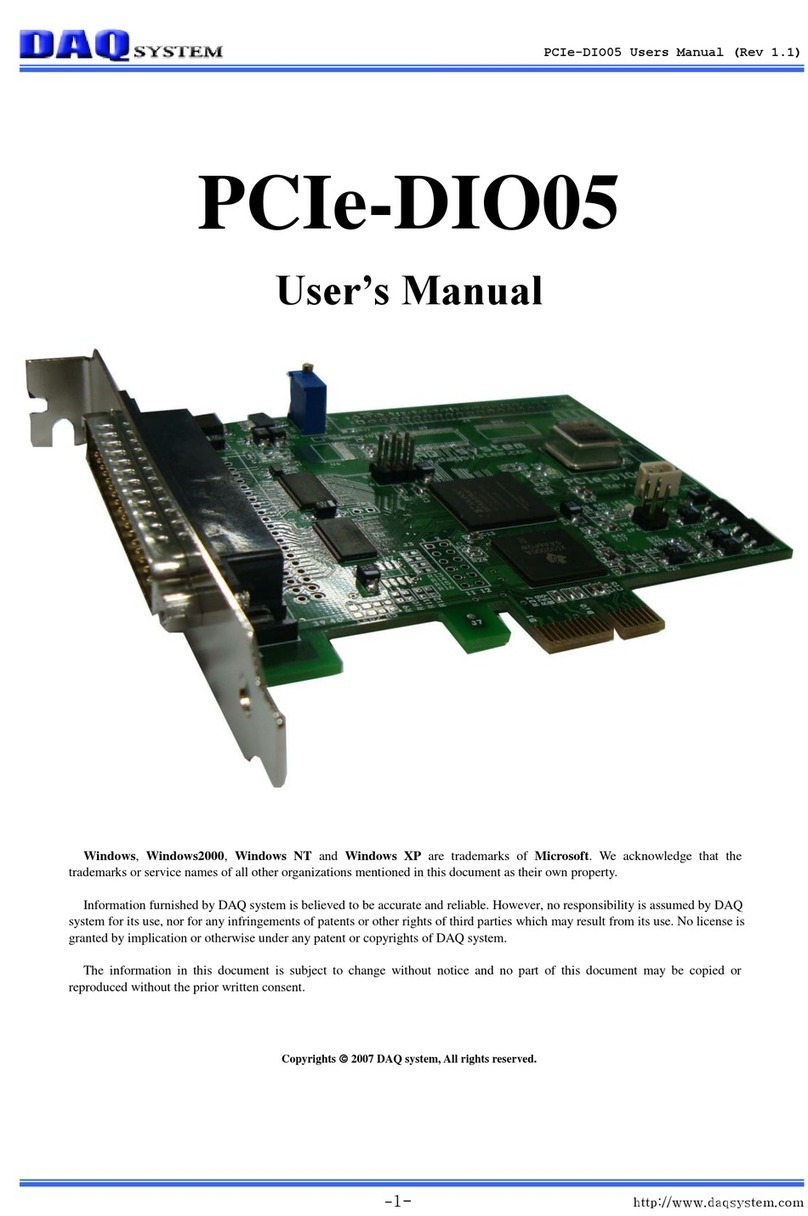

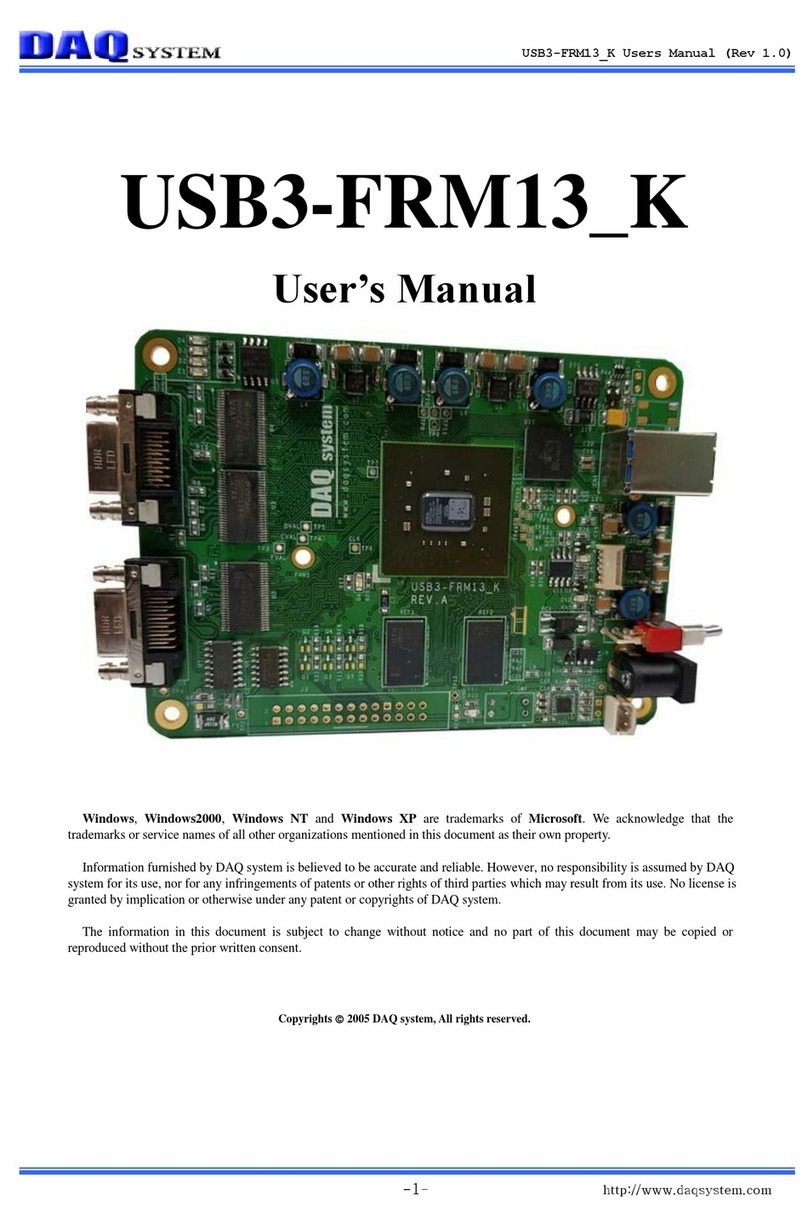

Other DAQ PCI Card manuals

Popular PCI Card manuals by other brands

ICP DAS USA

ICP DAS USA PCI-1002H user manual

Exsys

Exsys EX-60102 manual

Chelsio Communications

Chelsio Communications T5 Series Installation and user guide

Conrad Electronic

Conrad Electronic 97 46 71 operating instructions

Micro Innovations

Micro Innovations USB650A Quick installation guide

KTI Networks

KTI Networks KF-310 user guide