7

7

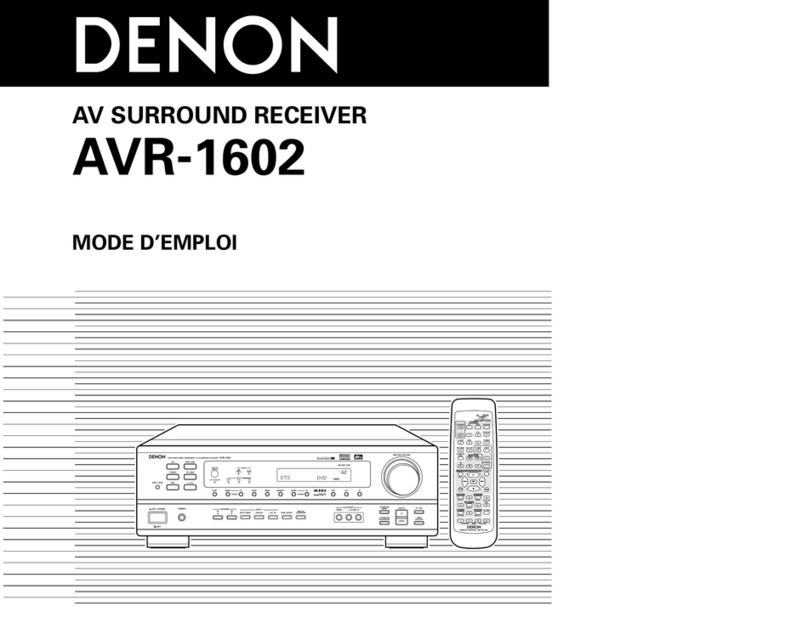

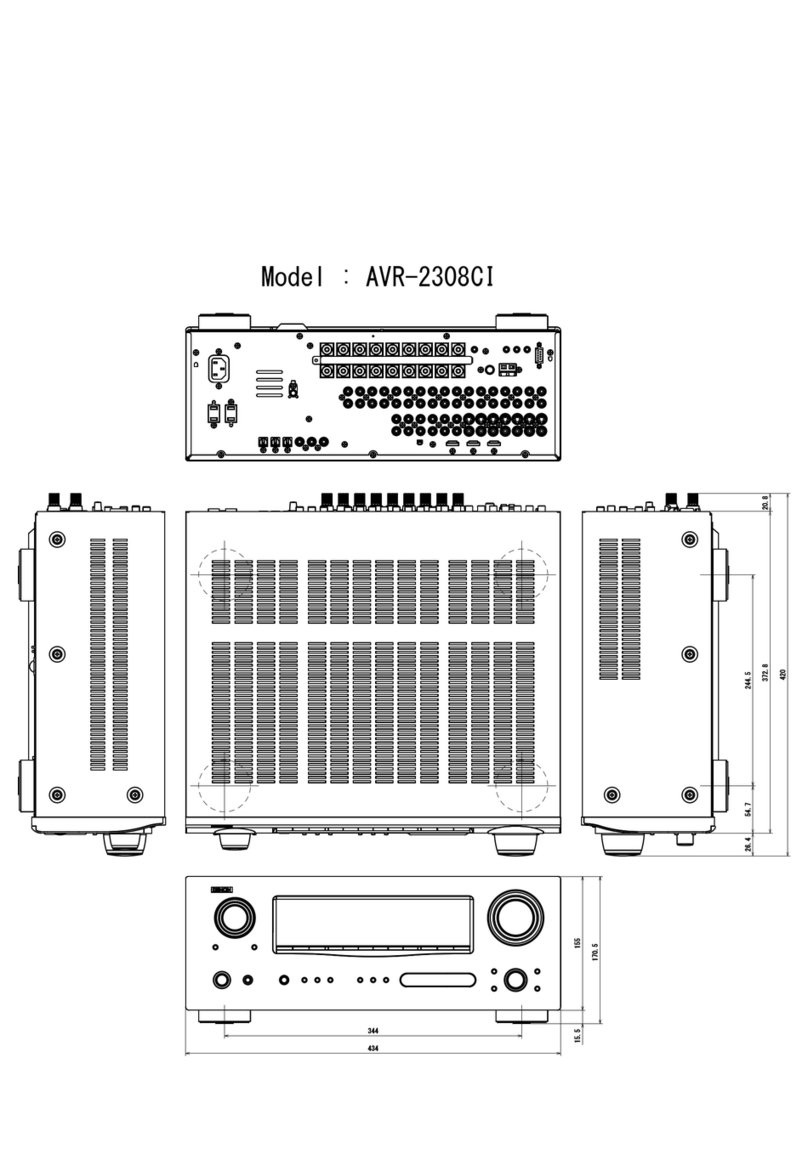

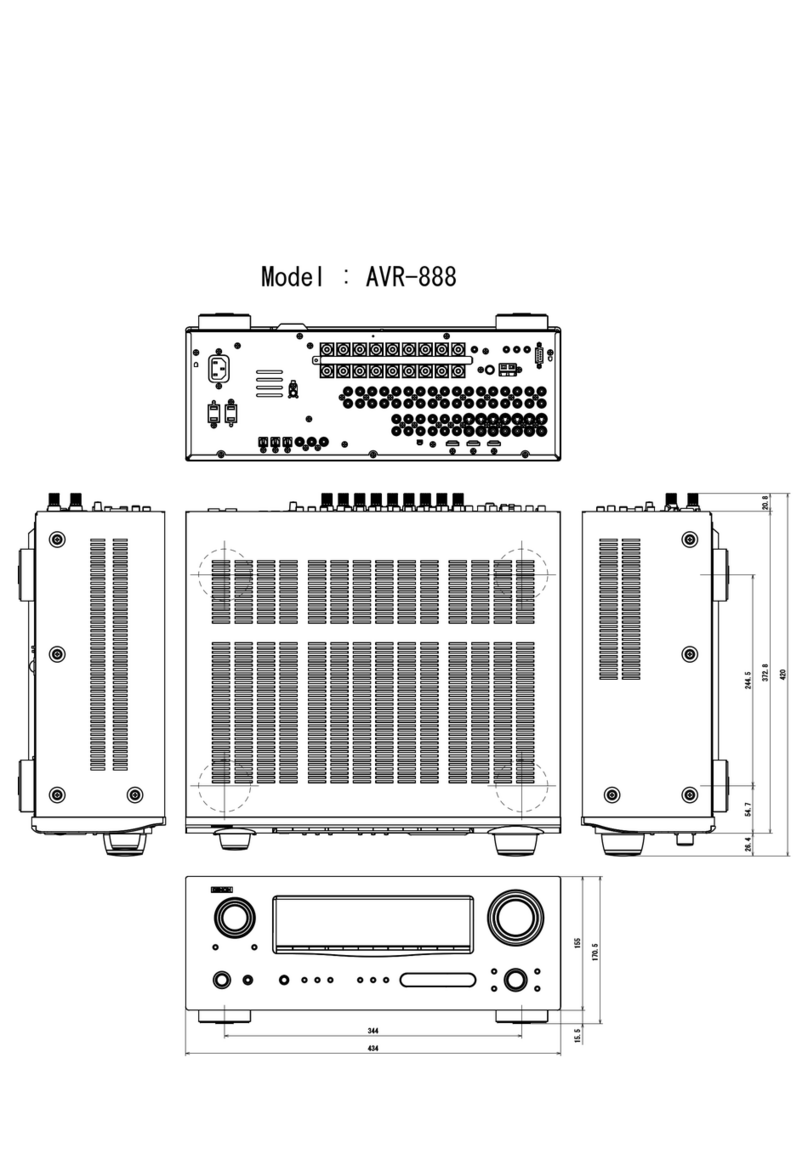

ADV-M71

DVD ENGINE UNIT RL-871 1U-3528 AMP/POWER UNIT

:IC :DVD Engine Block

SWITCHING POWER SUPPLY EEPROM PROG/INTE

16k DVD MECHA ROM RAM VCNT1/YC_H

PU/Traverse FRONT END VCNT2/WIDE

Loadin

_

LINE_2

DVD ON/OFF DI/DO/CS/CK

FL TUBE P ON/OFF for VDAC ex

and VIDEO DRIVER LINE_3

HNV-15SS04T SUB ON/OFF

UD-M30DVx : no use

with Filter

-

BH7862 PY/Y

13digit Dot Matrix SYSTEM uCOM ES6028 PY/Y PY IN

VIDEO DAC 4ch

Pb/Cb

M30626 FHPGP with Pro

ressive scan Pb/Cb Pb IN

r

rPr IN Pr/Cr

CLK YIN Y

SDATA I/O CIN C OUT C

FL DRIVER DA/CK/CE/RST

MIXOUT V

.

PLII/MP3/

WMA

/2chVirtual

User I/F ( MCLK)

PPCM

DVD-Audio

-

A/B TBCK

-

Develo

ed TWS

own

x

.

Y

LED-R

y

LED LED-G DENON BASS Management C

Config-1(ON/OFF each CH)

ROM

REMOCON REMOTE

e

ay

ompos

e

GP1UE271XK AUDIO DSP MONITOR OUT

MELODY 100

RXD ADSST-MEL100 SPDIF RSD TSD3 TSD 2 TSD 1 TSD 0

TXD

DENON BUS

x2

SD-RAM FAN ON/OFF COOLING FAN

Communicate with DENON-BUS : MD/DECK/CD-R 64MB

PCM/D.D/DTS bitstream H/P AMP

OPT OUT RESET/ACK/REQUEST/BUSY NJM4556AD

[GP1Z352TZ] WRIGHT/OSC/IOPOWER/POM_RST

䌾

1U-3527 MAIN UNIT H/P

[GP1F352RZ] SPDIF SDATA

PCM/AAC/D.D/DTS bitstream SPDIF RWS

OPT IN 2 DIN 0 RBCK

[GP1F352RZ] PCM MCLK H/P MUTE

H/P SW

TUNED [I2S x 3] ERR/CS FLAG/96DET

PROTECT

THERMO

FM/AM SDATA(AD) DO/CE/CLK/RST ERR MUTE SUB SUM VR OUTPUT GAIN SW

TUNER PACK LRCK/BCK for SP Config-2 SWITCHING 0䌾+18dB PRE AMP

AM ANT NJM2068 BA15218 BA15218 DSP/EXT/DIRECT BASS/TREBLE SDB 2dBstep BA15218

+

[STK-402-050]

MUTING

.

FR

LINE-1 IN C

MUTE

LINE-2 IN SL

SR

LINE-1 OUT LFE

BA15218

8ch CODEC Max output

LINE-2 OUT AD1837 DMIXL [0dB] 4.2Vrms

INPUT GAIN AMP

for RECOUT 0/+6dB

DMIXR FUNCTION/VR/TONE/SDB IC

BD3811K1

1U-3528 AMP/POWER UNIT

㪤㪬㪫㪜

㪤㪬㪫㪜

㪤㪬㪫㪜

㪤㪬㪫㪜

㪤㪬㪫㪜

㪤㪬㪫㪜

MUTE

MUTE

MUTE

FL

A/D CONVERTER

㪏㪺㪿㩷㪛㪆㪘㩷㪚㪦㪥㪭㪜㪩㪫㪜㪩

DIGITAL IN/OUTAUDIO IN/OUT

SPEAKER OUT

J:D-TERMINAL VIDEO OUT

FR

SR

SL

SW

C

MUTE

MUTE

MUTE

MUTE

MUTE

PRE OUT

DISC information is

received from DVD

and it displays it in the

FL tube.

Mute PY/Pb/Pr or Y/C/V

constantly

Route of

DIRECT mode

E3:COMPONENT VIDEO OUT

㪤㪬㪫㪜

㪤㪬㪫㪜

BLOCK DIAGRAMS

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com