Denon AVR-550SD User manual

Other Denon Stereo Receiver manuals

Denon

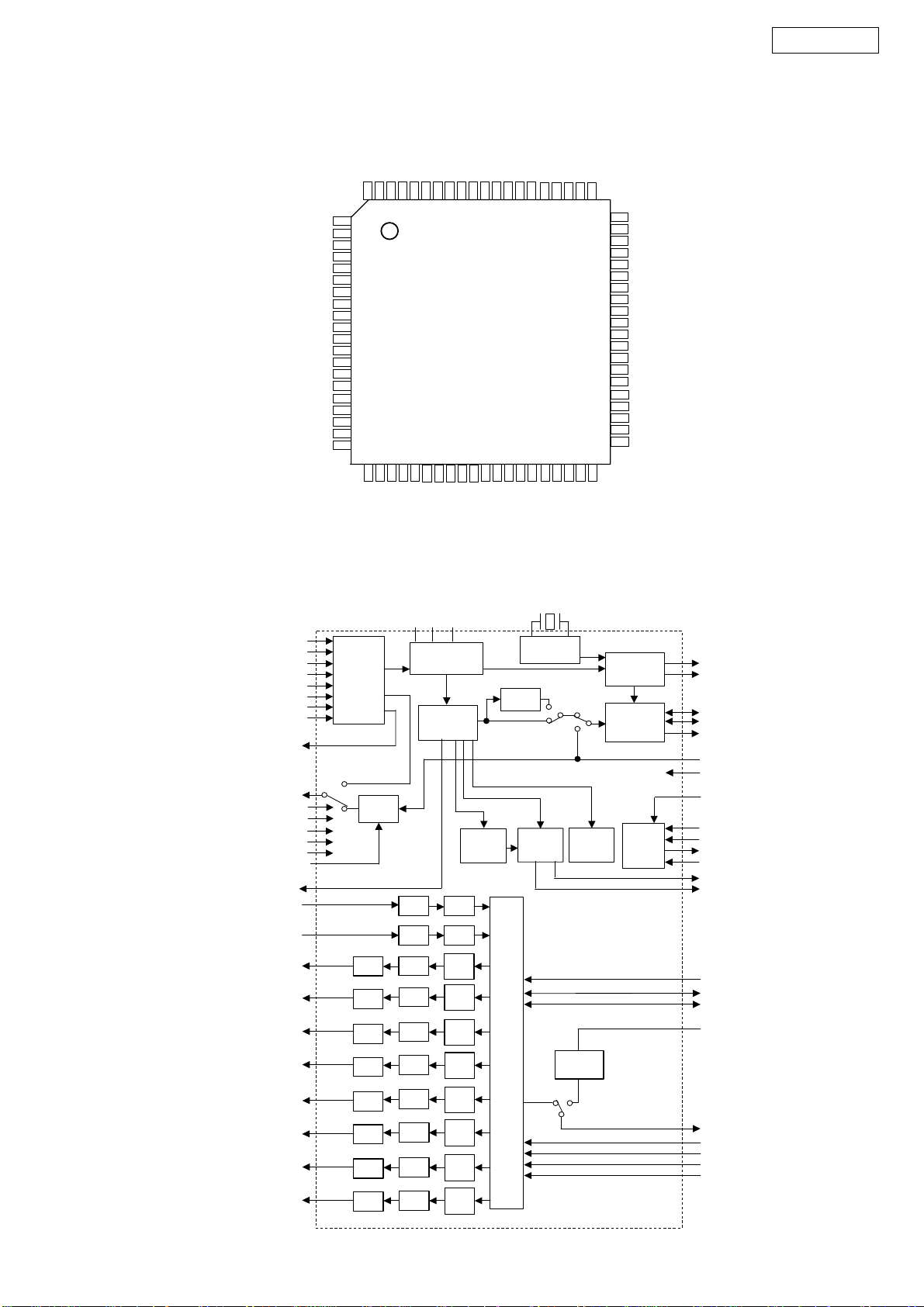

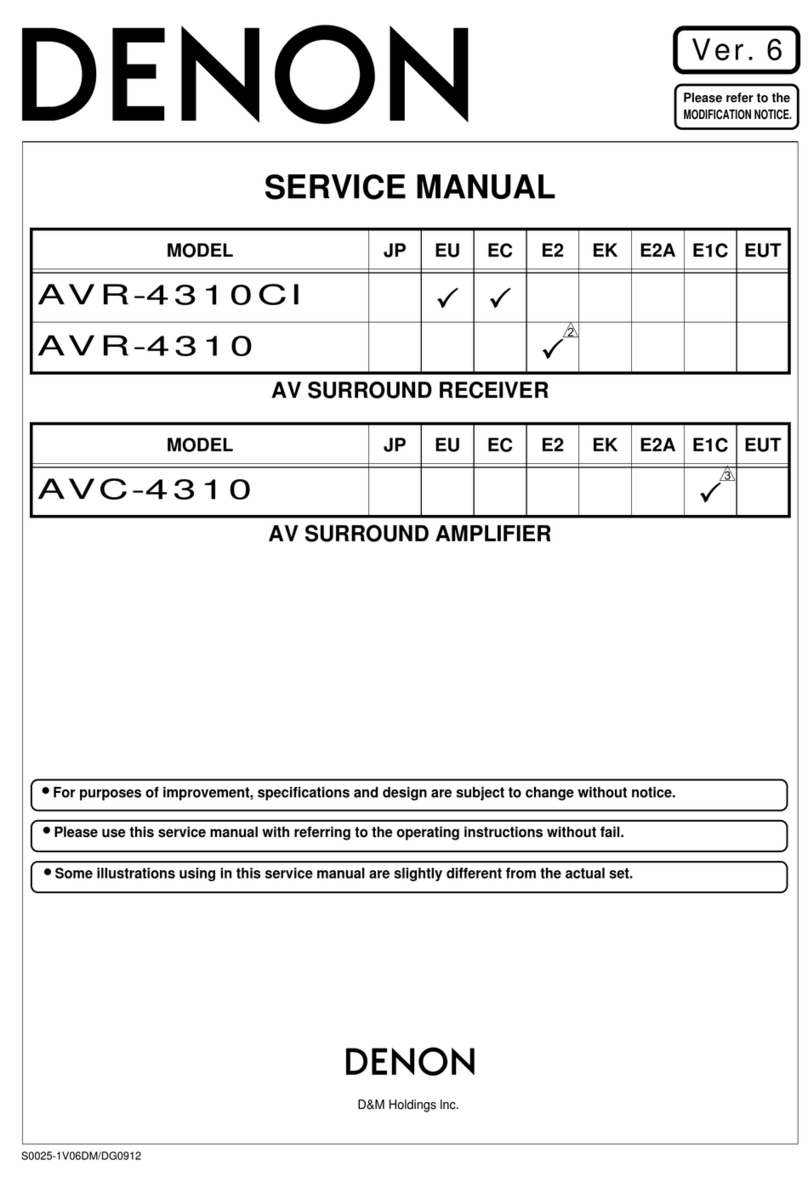

Denon AVC-4310 User manual

Denon

Denon AVR-1508 User manual

Denon

Denon AVRS650HOM User manual

Denon

Denon AVR-S500BT User manual

Denon

Denon AVR-1712 Quick start guide

Denon

Denon AVR-1506 User manual

Denon

Denon AVR-1312 User manual

Denon

Denon AVR-1312 User manual

Denon

Denon AVR-1601 User manual

Denon

Denon AVR-2801 User manual

Denon

Denon MULTEQXT AVR-4806 User manual

Denon

Denon AVR-2307CI User manual

Denon

Denon DRA-565RD User manual

Denon

Denon AVR-983 User manual

Denon

Denon AVR-2310 User manual

Denon

Denon AVR-X1600H User manual

Denon

Denon AVR-550SD User manual

Denon

Denon AVR-X550BT User manual

Denon

Denon MULTEQXT AVR-4306 User manual

Denon

Denon AVR-X2400H User manual

Popular Stereo Receiver manuals by other brands

Sony

Sony XAV-1500 operating instructions

Radio Shack

Radio Shack DX-399 owner's manual

Sony

Sony STR-DE535 - Fm Stereo/fm-am Receiver operating instructions

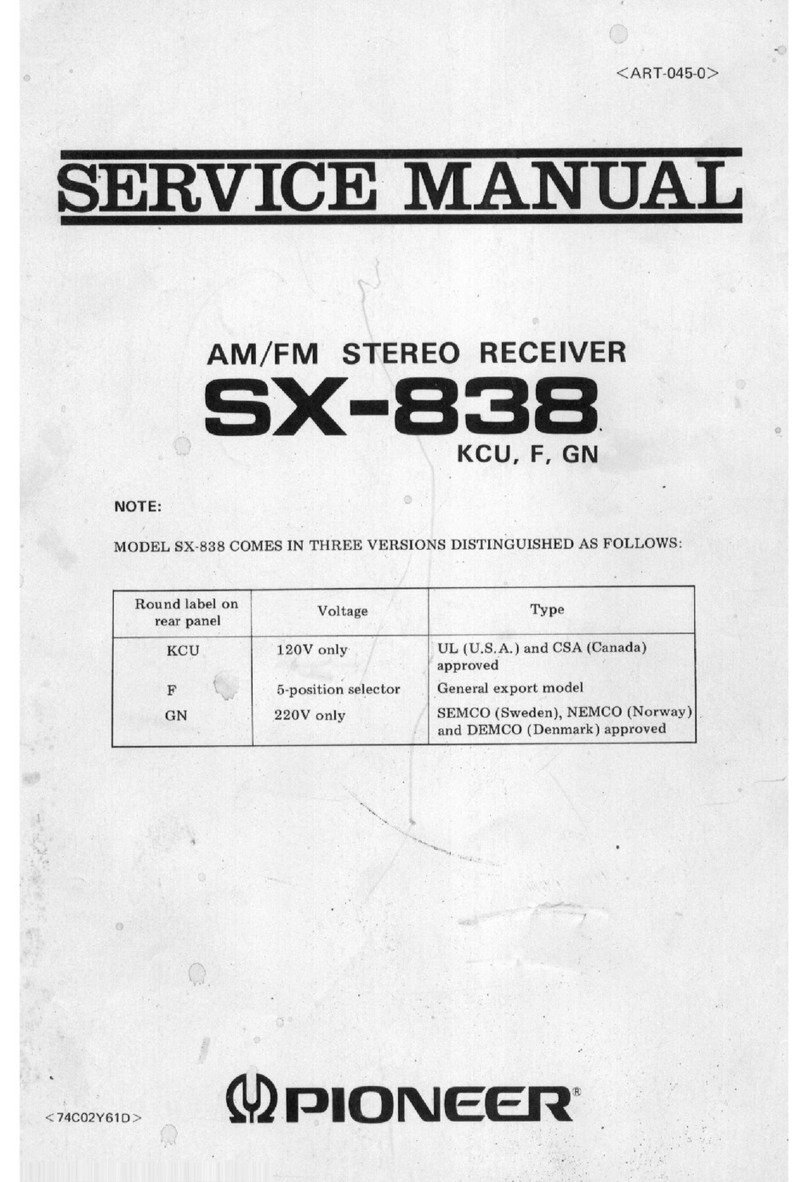

Pioneer

Pioneer SX-1000TA operating instructions

Yamaha

Yamaha MusicCast TSR-5B3D owner's manual

Sony

Sony STR-DE335 - Fm Stereo/fm-am Receiver operating instructions