Introduction1-1

Chapter 1

Introduction

R

The P55TV2mainboard is a high performance system hardware based on

Intel Pentium processor and is equipped with four PCI slots, four standard

ISAslots, Ultra I/O controllerand dual port PCI-IDEconnectors for the

futureexpansion.Thehardwaredimensionis220mmx260mmwithafour-

layer-design technology.

Specification

Intel 82430VX PCIset chipset.

Intel Pentium Processor, Pentium Processor with MMX technology,

AMD K5/K6 and Cyrix M1/M2 operating at 90 ~ 266 MHz with 321 ZIF

socket 7 provides scalability to accept faster processors in the future.

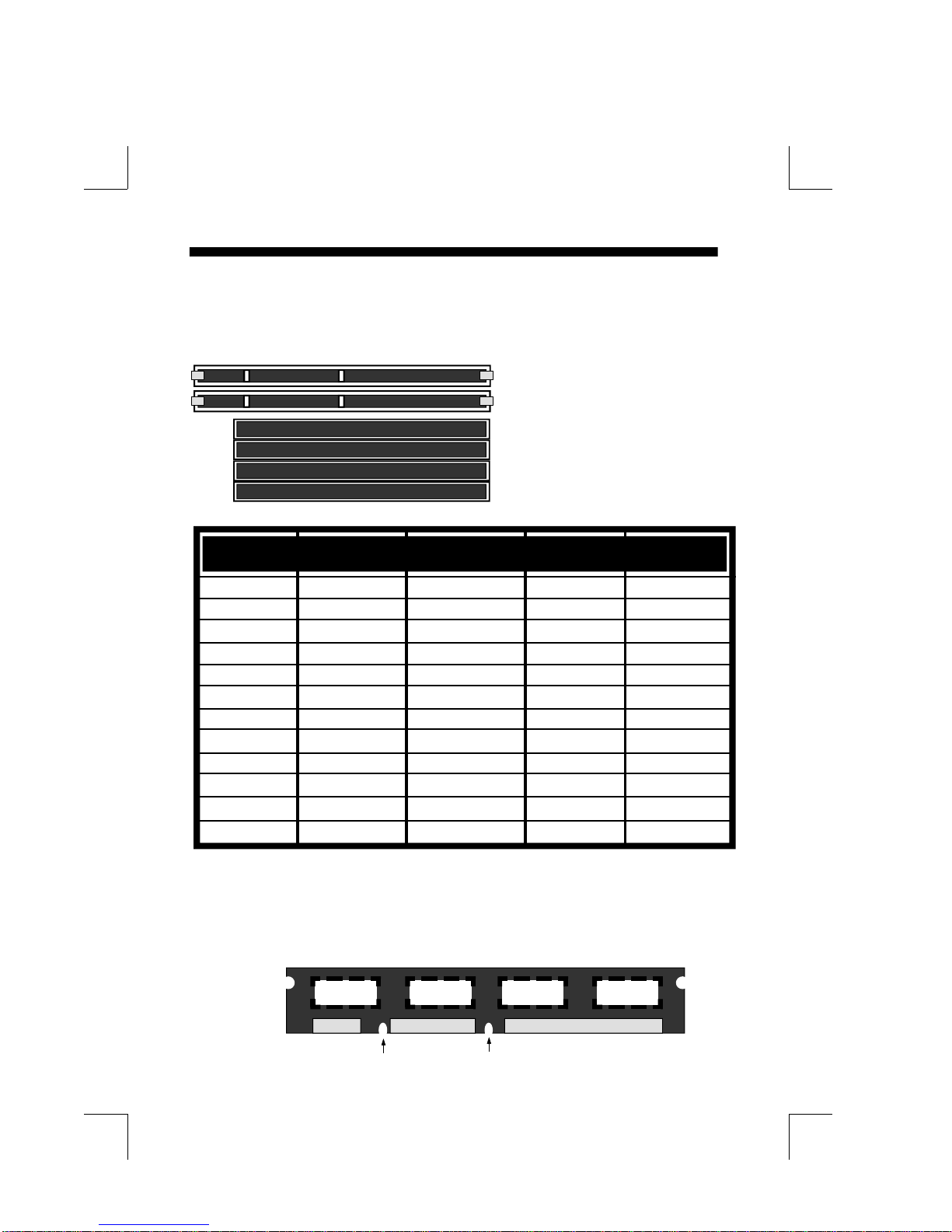

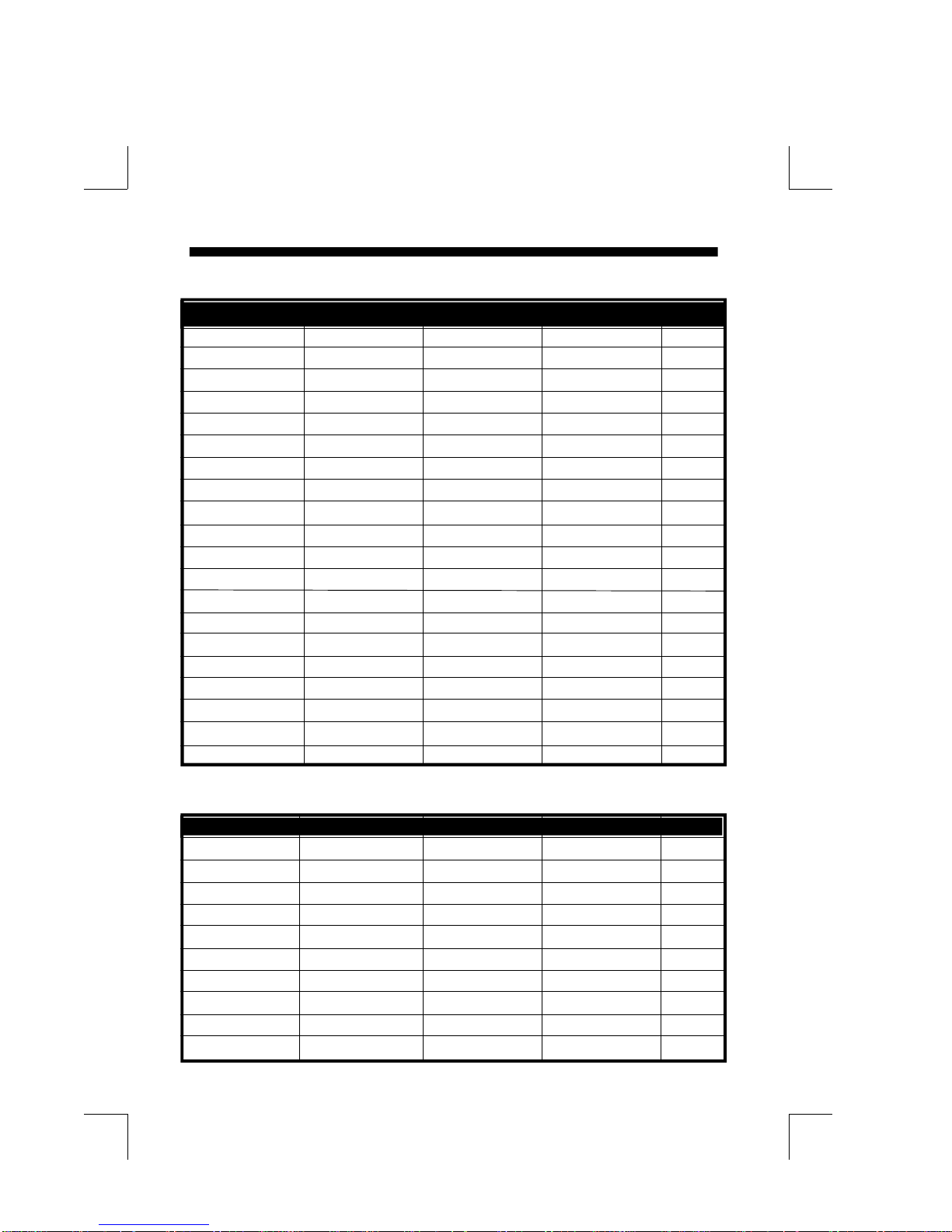

Supports up to 128 MegaBytes of DRAM (a minimum of 8 MB) on board

(72 Pins SIMM x 4, 168 Pins DIMM x 2). BIOS will autometically detect

and configure FP DRAM, EDO DRAM and SDRAM (Refer to Chapter 2-

3, System Memory Configuration).

Supports Onboard Pipelined Burst synchronous L2 Write Back Cache.

The cache memory combination can be 256KB/512KB (32KB*32 and

64KB*32 SRAM, respectively).

Supports four 16 bits ISA slots, four 32 bits PCI slots, and provides two

independent high performance PCI IDE interfaces capable of supporting

PIOMode3andMode 4 devices. TheP55TV2supportsfourPCIBus

Masters and a jumperless PCI INT# control scheme which reduces configu-

rationconfusionwhenpluggingin PCII/Ocontrollercard(s).

Supports AT API (e.g., CD-ROM) devices on both IDE interfaces.

Supports 1 floppy port, 1 parallel port (EPP,ECP port), 2 serial ports

(16550 Fast UART compatible) and 2 USB ports.

Supports a PS/2 style mouse and standard AT style keyboard connectors.

Supports Award Plug & Play BIOS. The BIOS is stored in Flash EPROM

form. It provides better upgradability for the system.

Supports CPU Hardware sleep and SMM (System Management Mode).

TheP55TV2utilizesaLithiumbatterywhichprovidesenvironmental

protection and longer battery life.

RTM

R