P6F169 User’s Manual

Preface 5

3.5.5 Front IEEE1394 connectors (1394_1 & 1394_2) ....................... 25

3.5.6 Front USB Header (USB1/2 & USB 3/4) .................................... 26

3.5.7 Floppy Driver Connector (FDD1)................................................ 26

3.5.8 IDE connectors (PRIMARY1 & SECONDARY1)........................ 27

3.5.9 Back Panel Connectors.............................................................. 28

3.5.10 Power Supply Connector (ATXPWR1) ..................................... 31

3.5.11 CPU/System Fan connectors ................................................... 32

3.5.12 PCI Slot .................................................................................... 32

3.5.13 Serial COM2 connector (COM2) .............................................. 33

3.5.14 Front MIC-in connector (JP2) ................................................... 34

3.5.15 Front AUX connector (J1)......................................................... 34

3.5.16 LVDS connector........................................................................ 35

3.5.17 Optional DVO interface ............................................................ 36

3.6 Installing System Memory ...................................................................... 37

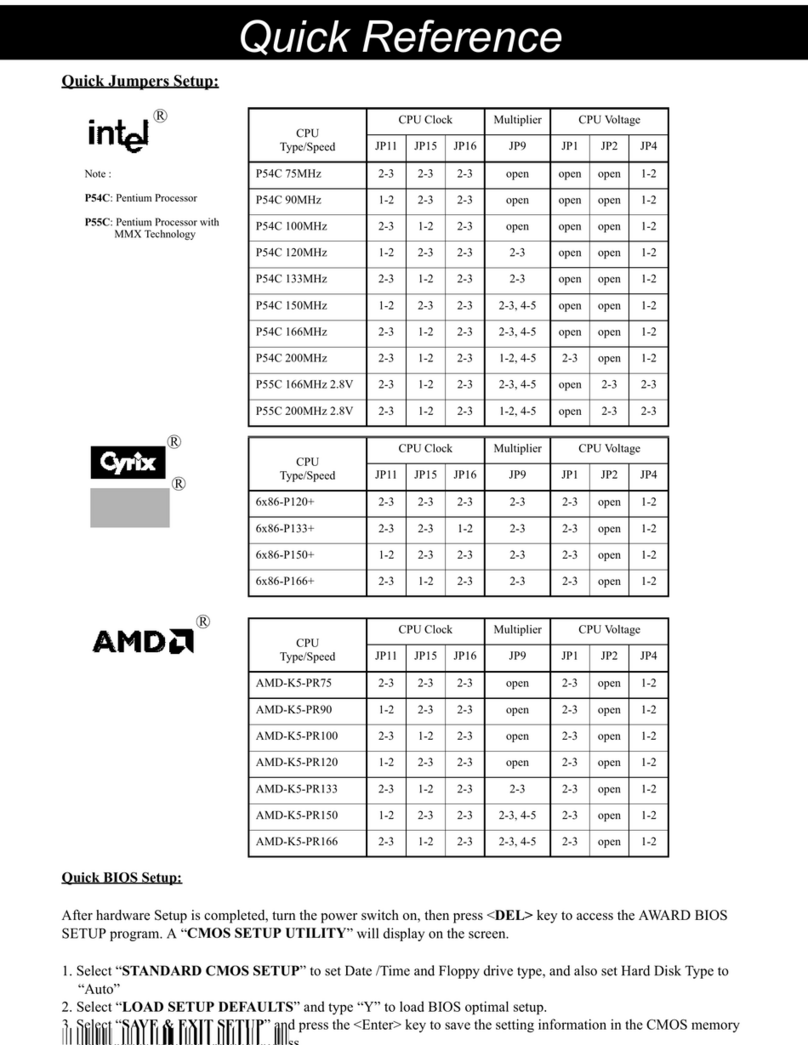

3.7 CPU & CMOS Jumper Setting ............................................................... 38

4. BIOS Configuration ........................................................................................... 40

4.1 Entering Setup........................................................................................ 41

4.2 Standard CMOS Features...................................................................... 42

4.3 Advanced BIOS Features....................................................................... 45

4.4 Advanced Chipset Features ................................................................... 48

4.4.1 DRAM clock/drive control ........................................................... 48

4.4.2 AGP & P2P bridge control .......................................................... 50

4.4.3 CPU & PCI Bus Control.............................................................. 51

4.5 Integrated Peripherals............................................................................ 53

4.5.1 VIA OnChip IDE Device.............................................................. 53

4.5.2 VIA OnChip PCI Device.............................................................. 55

4.5.3 SuperIO Device .......................................................................... 56

4.6 Power management Setup..................................................................... 58

4.6.1 IRQ/Event Activity Detect ........................................................... 60