v

CONTENTS

CHAPTER 1 OVERVIEW ................................................................................................... 1

1.1 Product Overview ............................................................................................................................... 2

1.2 Features .............................................................................................................................................. 3

1.3 Block Diagram of MB90V390H ........................................................................................................... 6

1.4 Block Diagram of MB90V390HA/MB90V390HB ................................................................................. 7

1.5 Block Diagram of MB90394HA/MB90F394H(A) ................................................................................. 8

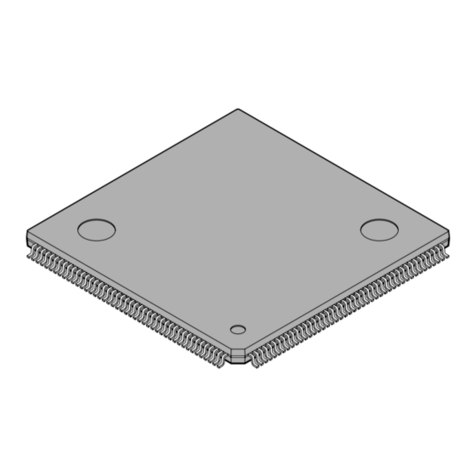

1.6 Pin Assignment ................................................................................................................................... 9

1.7 Package Dimensions ........................................................................................................................ 12

1.8 Pin Functions .................................................................................................................................... 13

1.9 Input-Output Circuits ......................................................................................................................... 19

1.10 Handling Device ................................................................................................................................ 22

CHAPTER 2 CPU ............................................................................................................ 25

2.1 Outline of the CPU ............................................................................................................................ 26

2.2 Memory Space .................................................................................................................................. 27

2.3 Memory Space Map .......................................................................................................................... 30

2.4 Linear Addressing ............................................................................................................................. 32

2.5 Bank Addressing Types .................................................................................................................... 33

2.6 Multi-byte Data in Memory Space ..................................................................................................... 35

2.7 Registers ........................................................................................................................................... 36

2.7.1 Accumulator (A) ........................................................................................................................... 39

2.7.2 User Stack Pointer (USP) and System Stack Pointer (SSP) ....................................................... 40

2.7.3 Processor Status (PS) ................................................................................................................. 41

2.7.4 Program Counter (PC) ................................................................................................................. 44

2.8 Register Bank ................................................................................................................................... 45

2.9 Prefix Codes ..................................................................................................................................... 47

2.10 Interrupt Disable Instructions ............................................................................................................ 49

2.11 Precautions for Use of "DIV A, Ri" and "DIVW A, RWi" Instructions ................................................ 51

CHAPTER 3 INTERRUPTS ............................................................................................. 53

3.1 Outline of Interrupts .......................................................................................................................... 54

3.2 Interrupt Vector ................................................................................................................................. 57

3.3 Interrupt Control Registers (ICR) ...................................................................................................... 59

3.4 Interrupt Flow .................................................................................................................................... 62

3.5 Hardware Interrupts .......................................................................................................................... 64

3.5.1 Hardware Interrupt Operation ...................................................................................................... 65

3.5.2 Occurrence and Release of Hardware Interrupt .......................................................................... 66

3.5.3 Multiple interrupts ........................................................................................................................ 68

3.6 Software Interrupts ........................................................................................................................... 69

3.7 Extended Intelligent I/O Service (EI2OS) .......................................................................................... 71

3.7.1 Extended Intelligent I/O Service Descriptor (ISD) ....................................................................... 73

3.7.2 EI2OS Status Register (ISCS) ..................................................................................................... 75

3.8 Operation Flow of and Procedure for Using the Extended Intelligent I/O Service (EI2OS) .............. 77