Publication No. CPCI3UX606-HRM/1 CPCI3UX606 7

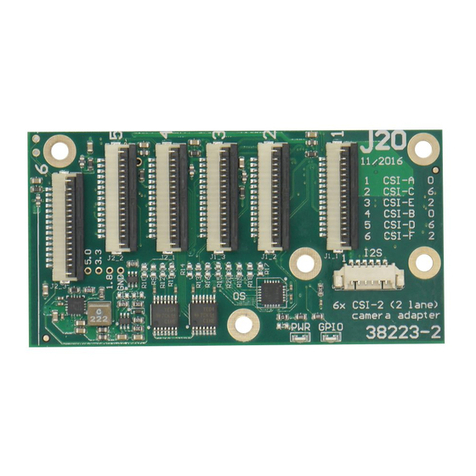

1.4 Pin Assignments

1.4.1 P1 (Ethernet Gigabit Signals)

If a build option that does not provide Gigabit Ethernet on either channel 0 or 1 is selected, then

these pins carry the GPIO signals shown. In this case, no links should be fitted across P1 to prevent

damage to or unexpected operation on any Gigabit Ethernet interface connected to J3 or J4.

AssumingthebuildoptionprovidesGigabitEthernet,forGigabitEthernet

operationonchannel0(atJ3),fitlinksacrossthepinsshownbelow:

ForGigabitEthernetoperationonchannel1(atJ4),fitlinksacrossthepinsshown

below:

ETH1_3‐andETH1_3+areselectedusingP9andP10.

1.4.2 P2 (COM1/COM2)

COM1is2‐wireRS232DTEasaminimum(noRTS/CTS);4‐wireoperation

dependsonavailabilityoftherequiredsignals,whichisanIMP3Abuildoption

(alsoseeP9andP10).RS232/RS422configurationofCOM1issoftwarecontrolled;

RS422optionsignalsaregiveninparentheses.

COM2is4‐wirepermanently.RS232/RS422configurationofCOM2issoftware

controlled;RS422optionsignalsaregiveninparentheses.

Table 1-4 P1 Pin Assignments for Gigabit Ethernet on Channel 0

Pins Linked Signal GPIO Signal

12 and 11 ETH0_2+ GPIO4

10 and 9 ETH0_2- GPIO5

8 and 7 ETH0_3+ GPIO7

6 and 5 ETH0_3- GPIO8

Table 1-5 P1 Pin Assignments for Gigabit Ethernet on Channel 1

Pins Linked Signal GPIO Signal

4 and 3 ETH1_2+ GPIO6

2 and 1 ETH1_2- GPIO9

Table 1-6 P2 Pin Assignments

Pin Signal Pin Signal

1COM1_LBa

a.Connected between pins 1, 2 and 3.

2COM1_LBa

3COM1_LBa4 No connection

5 COM1_TXD (TXD_A) 6 COM1_RXD (RXD_A)

7 COM1_CTS (RXD_B) 8 COM1_RTS (TXD_B)

9 No connection 10 No connection

11 No connection 12 COM2_LBb

13 COM2_TXD (TXD_A) 14 COM2_LBb

15 COM2_LBb

b.Connected between pins 12, 14 and 15.

16 COM2_RXD (RXD_A)

17 COM2_RTS (TXD_B) 18 COM2_CTS (RXD_B)

19 GND 20 GND