Room 02-04, 10/F, Block A, Building 8, Shenzhen International Innovation Valley, Dashi Road,

Nanshan District, Shenzhen, Guangdong, China

Contents

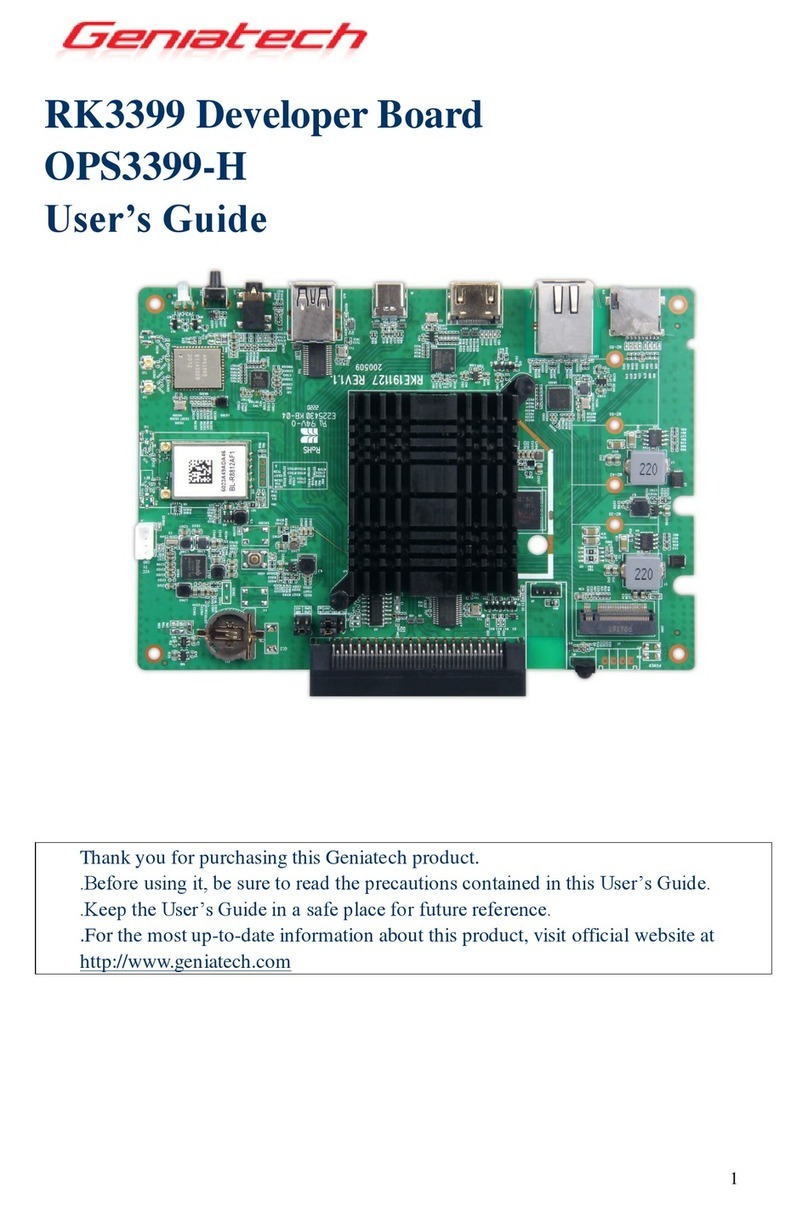

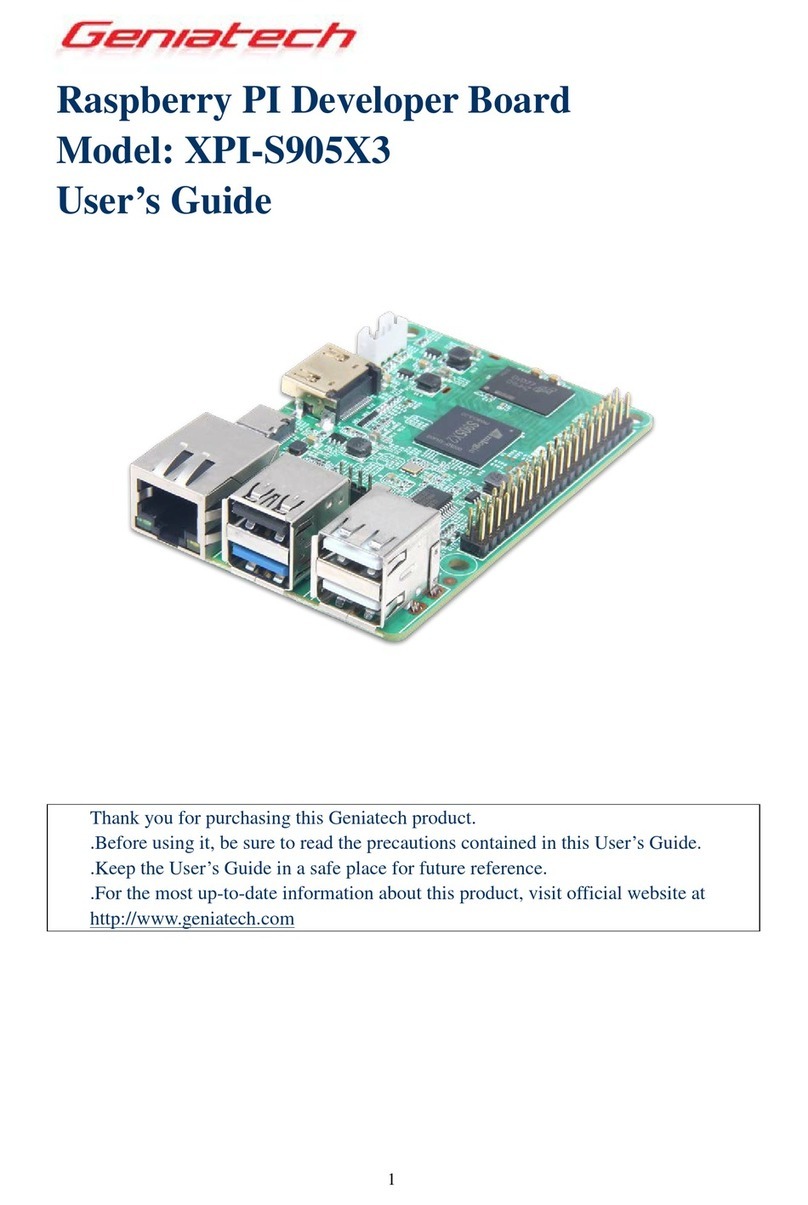

1 Introduction ......................................................................................................................................... 1

1.1 Board overview ................................................................................................................................ 2

2. What’s in the Box ............................................................................................................................... 3

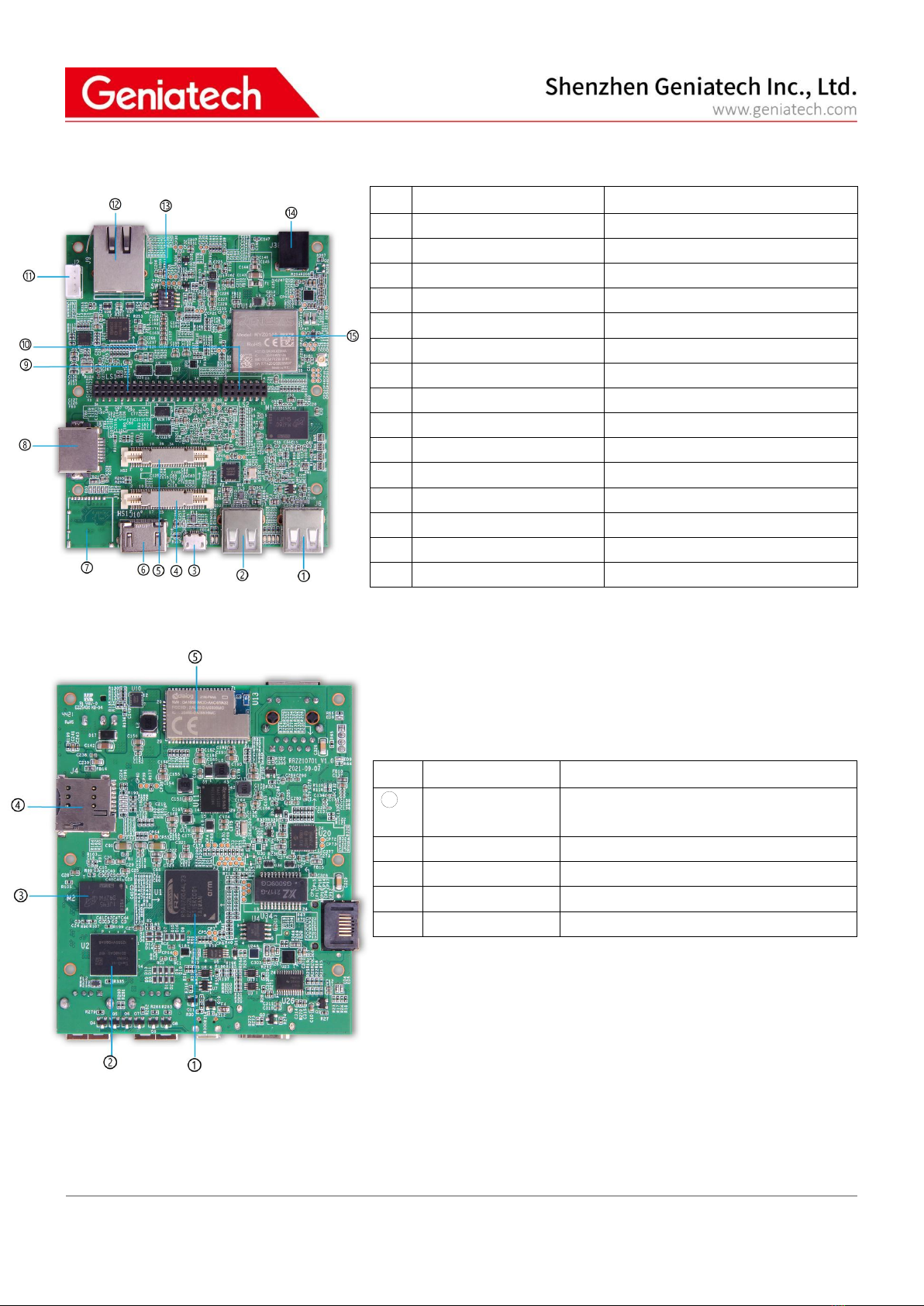

3.RS-G2L100&RS-V2L100 BOARD OVERVIEW ..............................................................................4

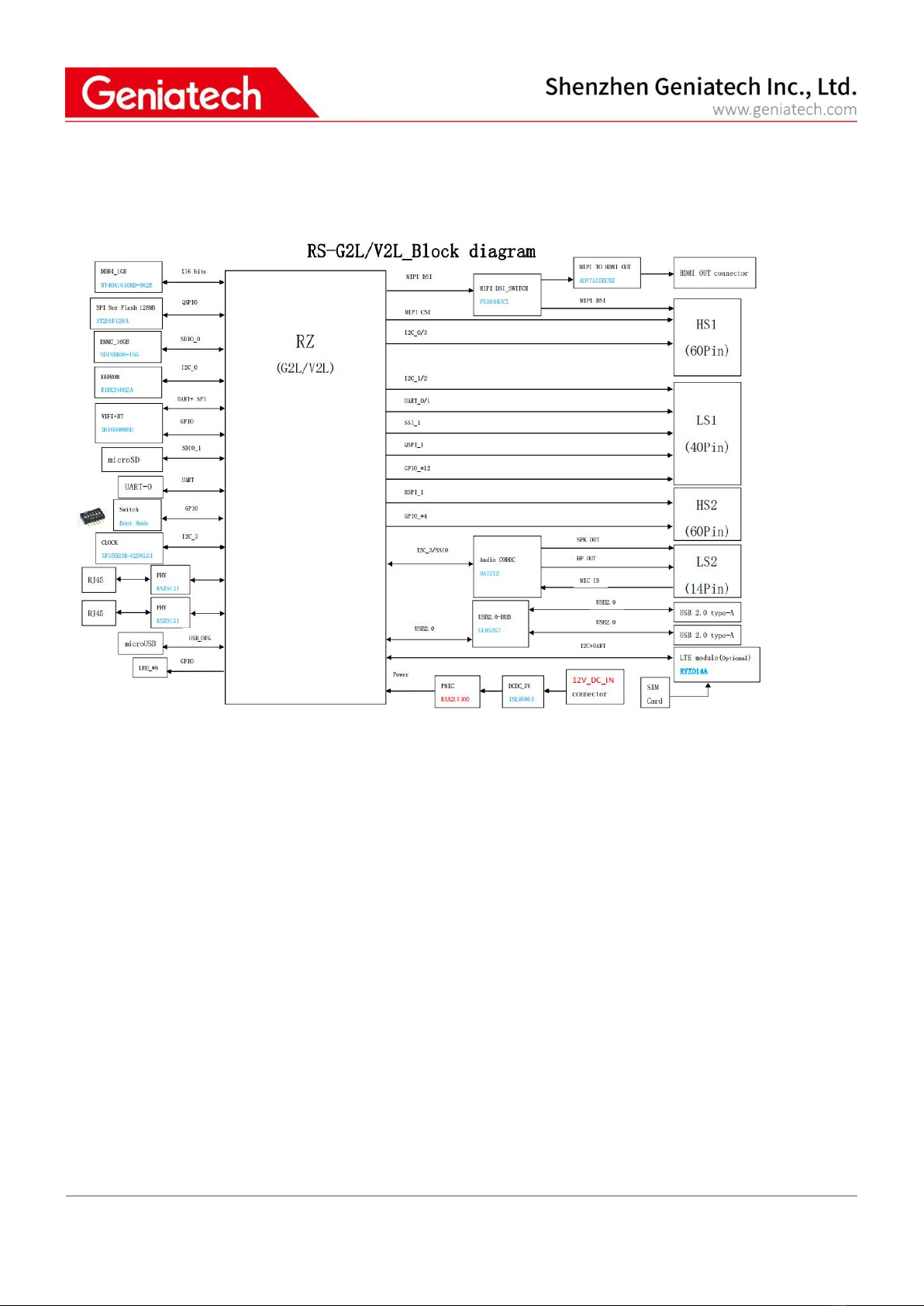

3.1 System Block Diagram .................................................................................................................4

3.2 Processor .......................................................................................................................................4

3.3 Memory ........................................................................................................................................ 4

3.4 MicroSDHC ..................................................................................................................................4

3.5 Display Interface .......................................................................................................................... 5

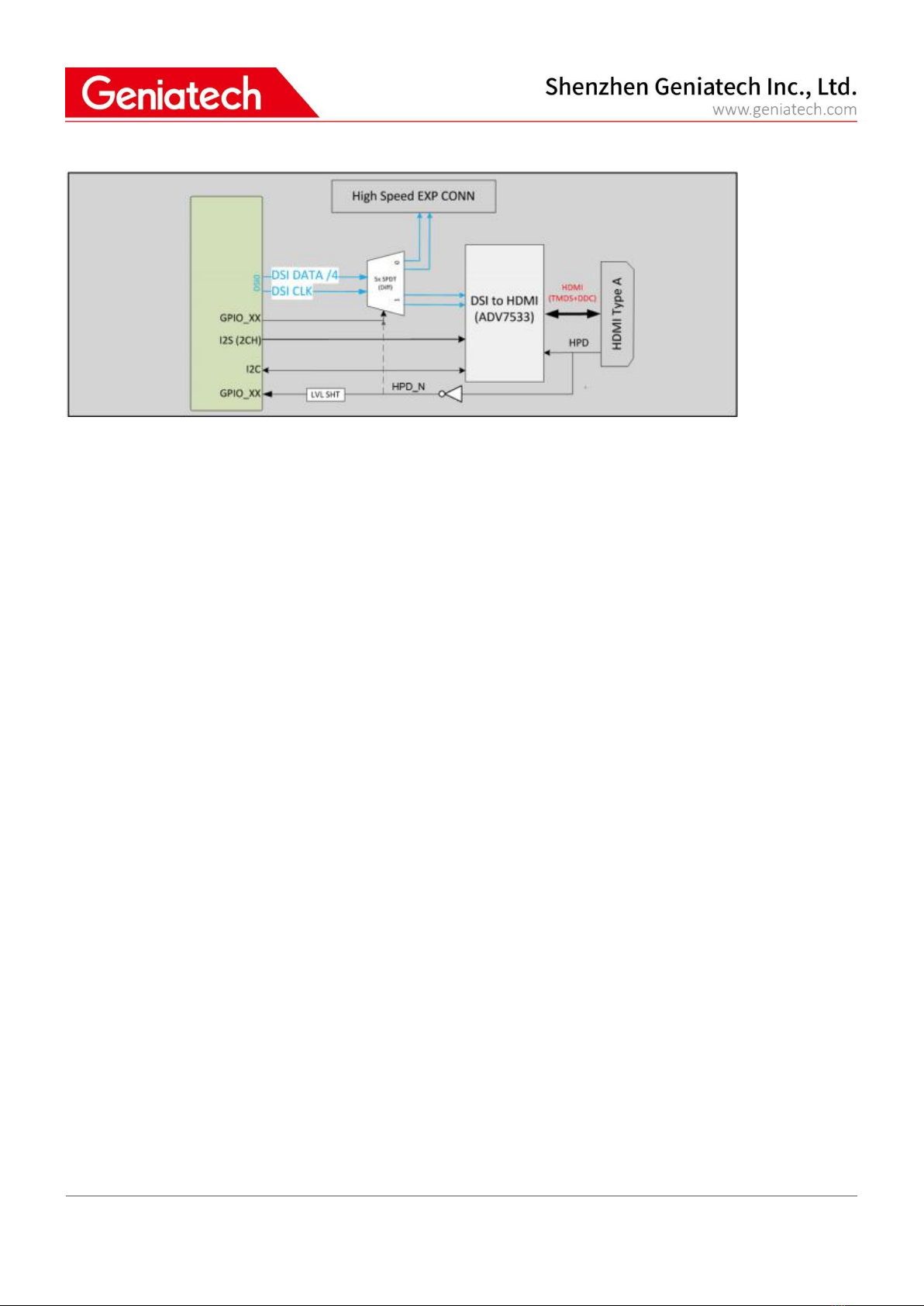

3.5.1 HDMI ..................................................................................................................................... 5

3.5.2 MIPI-DSI ................................................................................................................................5

3.6 Camera Support ............................................................................................................................ 5

3.7 Audio ............................................................................................................................................ 6

3.8 WiFi .............................................................................................................................................. 6

3.9 Bluetooth ...................................................................................................................................... 6

3.10 RGMII ........................................................................................................................................ 6

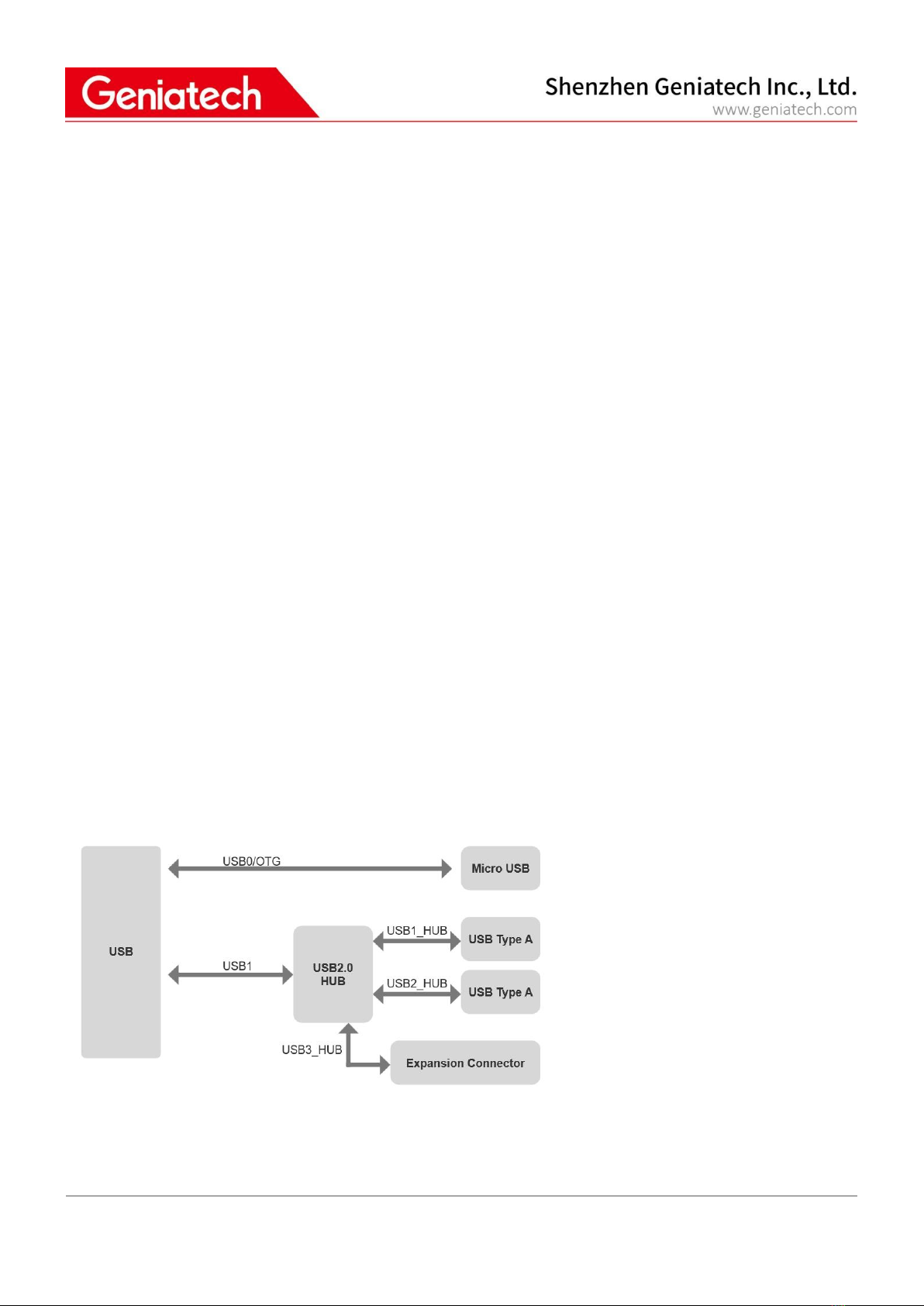

3.11 USB Port .....................................................................................................................................6

3.11.1 USB-Host ports .....................................................................................................................6

3.11.2 USB-Device port .................................................................................................................. 7

3.12 Debug ......................................................................................................................................... 7

3.12.1 Debug UART ........................................................................................................................7

3.12.2 Debug JTAG ......................................................................................................................... 7

4 40-pin Low Speed(LS) expansion connector ...................................................................................... 7

4.1 UART{0/1} ...................................................................................................................................8

4.2 I2C{0/1} ....................................................................................................................................... 8

4.3 GPIO{A-L} .................................................................................................................................. 8

4.4 SPI 0 ............................................................................................................................................. 8

4.5 I2S .................................................................................................................................................8

5 14-pin Low Speed(LS) expansion connector ...................................................................................... 9

5.1 Speaker ......................................................................................................................................... 9

5.2 Mic ................................................................................................................................................9

5.3 Headset ......................................................................................................................................... 9

6 60-pin High Speed(HS1) expansion connector ................................................................................... 9

6.1 MIPI DSI 2 ................................................................................................................................. 10

6.2 MIPI CSI 0 ..................................................................................................................................11