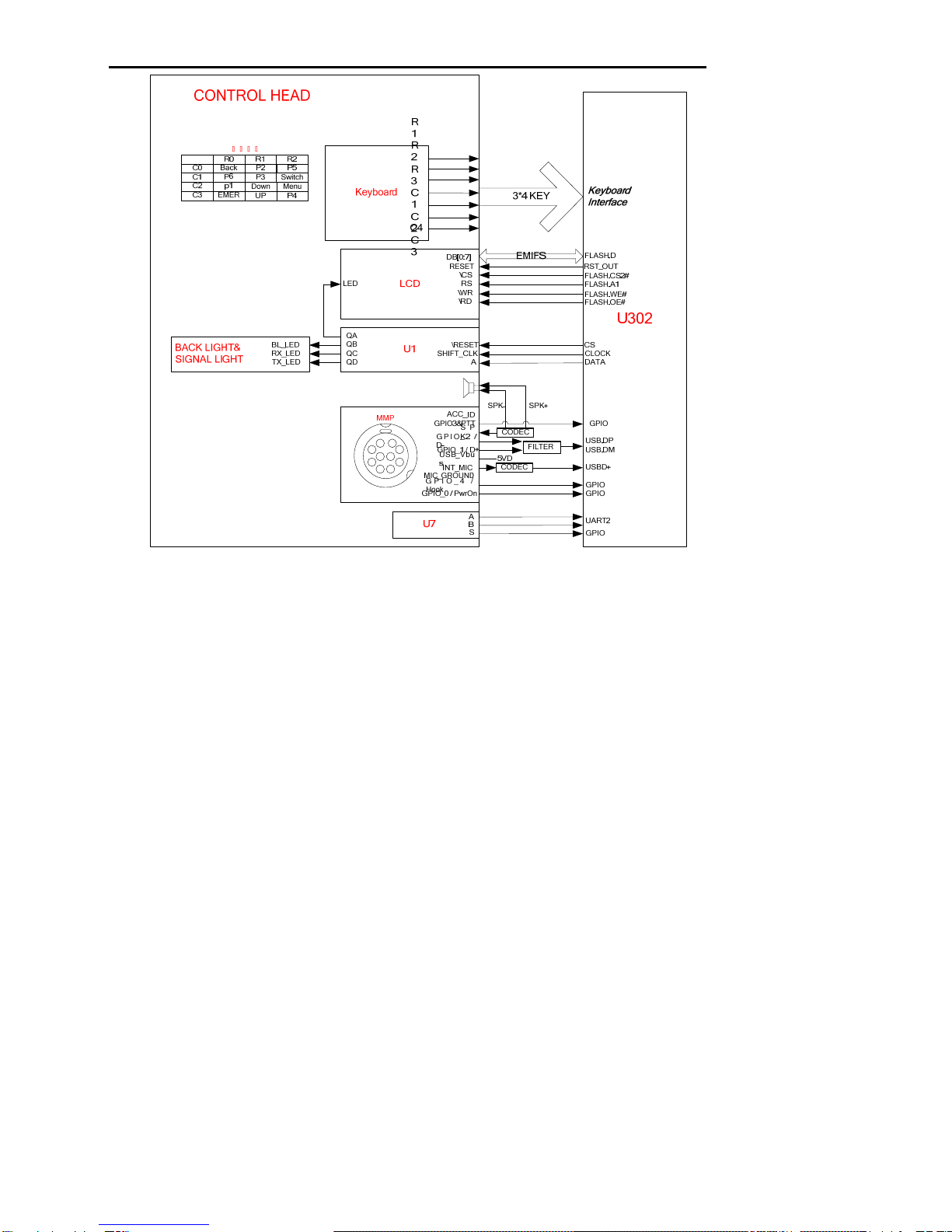

5

memory chip select, LCD chip select and reset signal, and the signals will be pulled up by R36, R35, R34,

R33 and R6 respectively. 5V voltage is converted to 3.3V by U5, and is then supplied to the LCD.

1.4 LED and Backlight

LED enable signal is fed to the serial-to-parallel converter IC, and then is output by U302. RX status is

indicated by green LED, and TX is by red LED. Backlight will be illuminated once any key is pressed.

The red and green LEDs in series are powered by 5V (U902) and controlled by Q2 and Q3. The

backlight is powered by 5V and controlled by Q1. Control signals are output via U1.

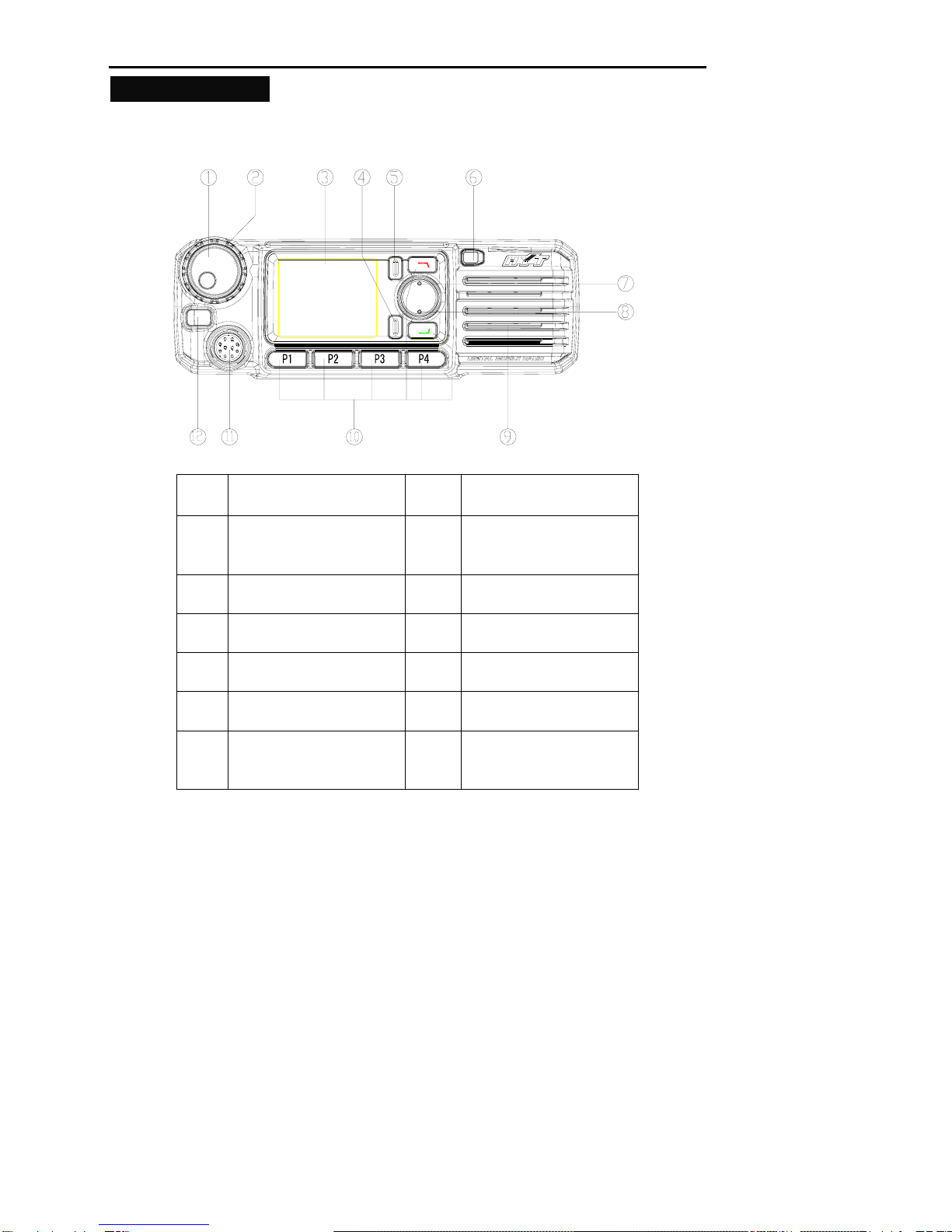

1.5 MMP Interfaces

The MMP interfaces are defined as follows:

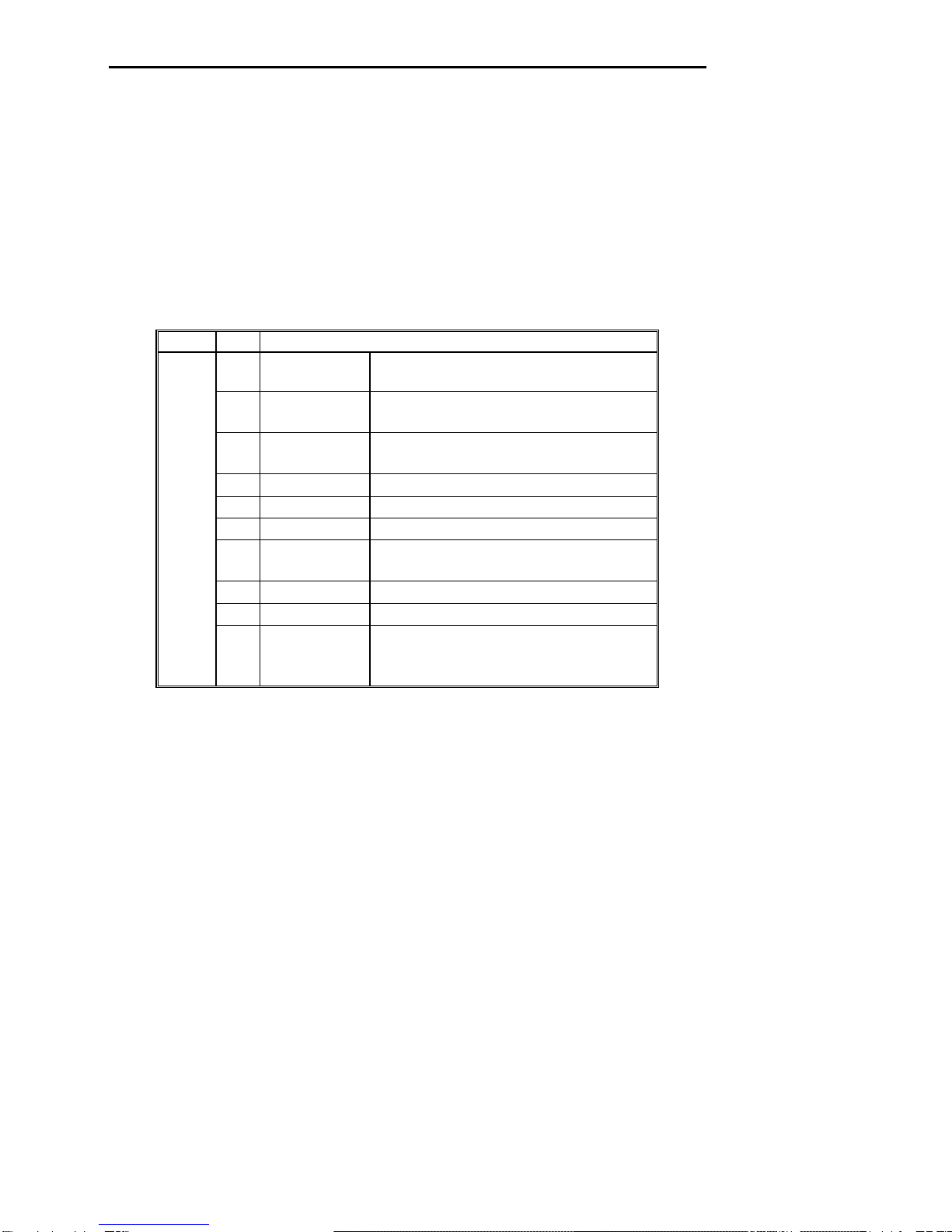

No. Definition & Description

1 Accessory identifier

port 1

The pin together with pin 10 can form an accessory

identification matrix.

2 PTT input Used to input PTT signal from microphone. The pin is at

low level when PTT is hold down.

3 Handset audio

output

Used to output audio received from accessories; the

Handset option must be checked in the CPS.

4 USB_D- USB data line D-

5 GND Ground

6 USB_VBUS Provides +5V for USB accessories.

7 Mic input Used to input external microphone signal. Vrms=80mV

@ 3K dev.

8 USB_D+ USB data +

9 HOOK Valid upon low level. The default is high level.

MMP10

10 Accessory identifier

port 2

The pin together with pin 1 can form an accessory

identification matrix, details of which are stated in the file

“Definition of External Interfaces”.

Table 1 Definition of MMP Interfaces

1.6 Audio output

The front panel provides two paths of audio output Handset_audio and SPK±. Handset_audio is the

output of received audio via MMP interface, and SPK± is the output by the PA U201 as audio signal for

the front panel speaker.

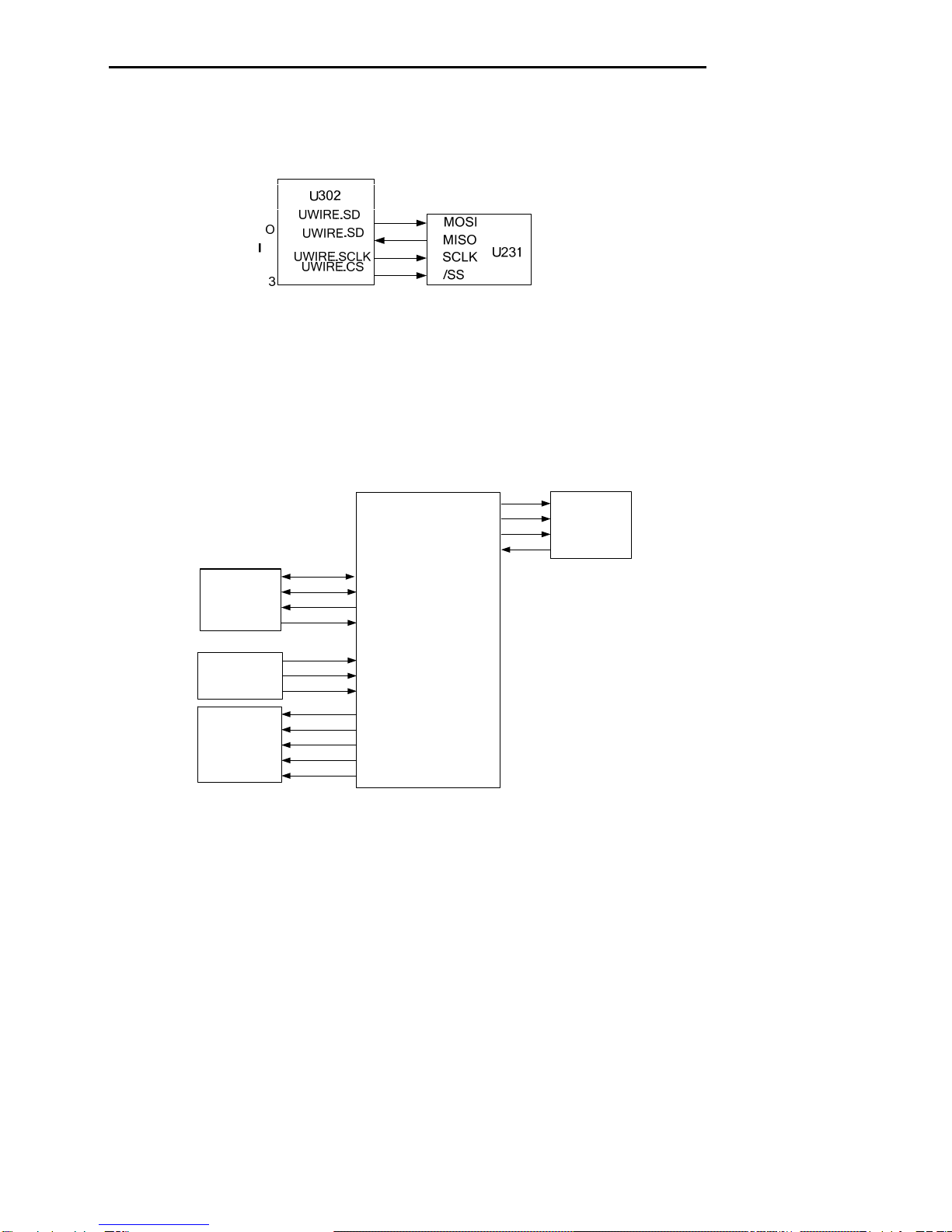

1.7 Volume Control

The encoder switch U7 will generate volume adjustment signals, which will be routed to U302 by

GPIO17 and GPIO18.