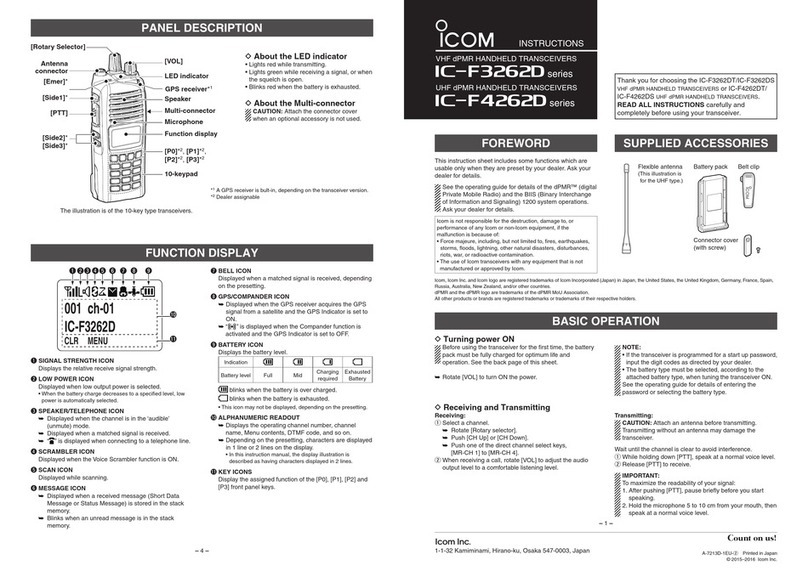

4·1·5

IF

CIRCUITS (MAIN UNIT)

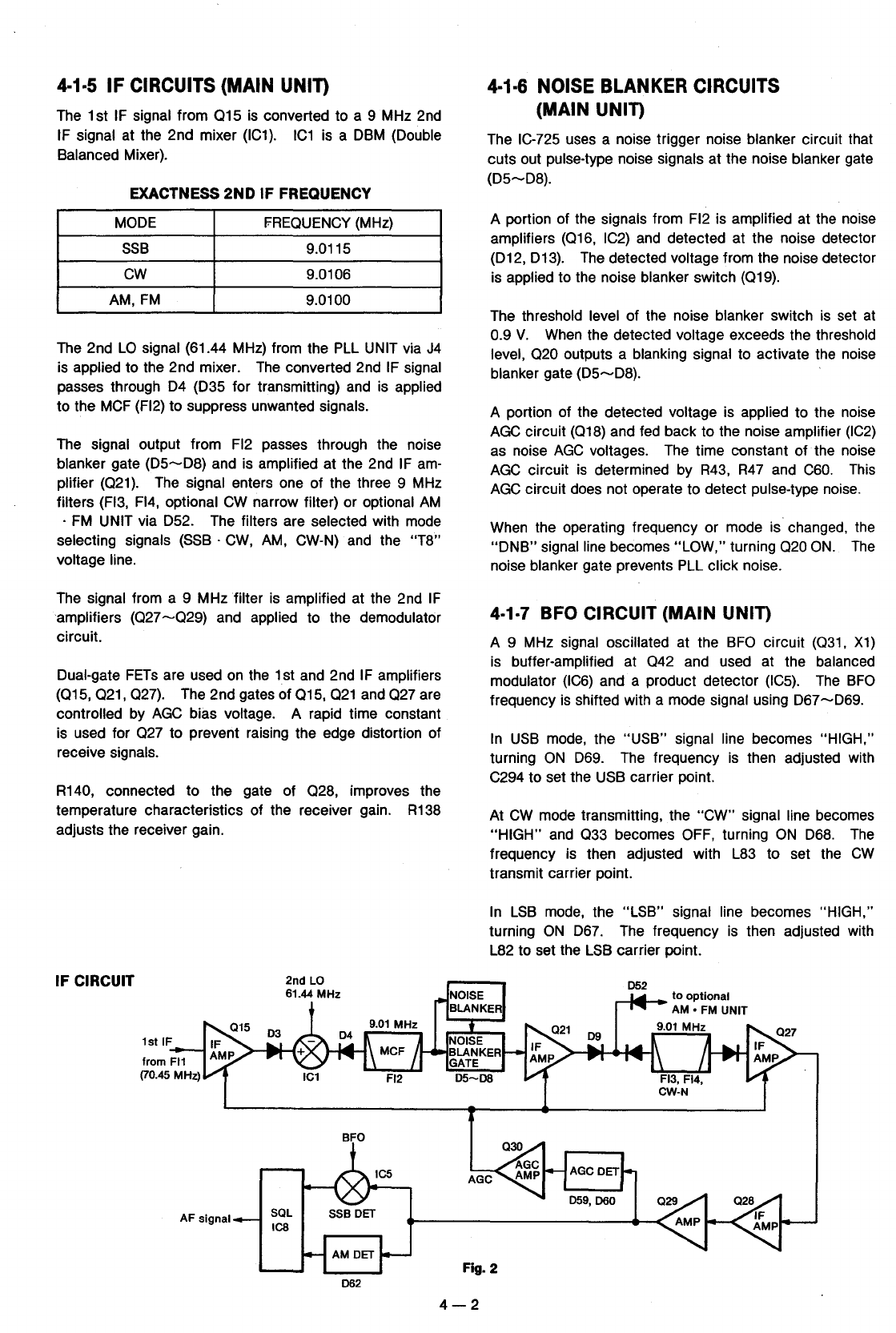

The 1st

IF

signal from

015

is

converted to a 9 MHz 2nd

IF signal at the 2nd mixer

(IC1).

IC1

is a

DBM

(Double

Balanced Mixer).

EXACTNESS

2ND

IF FREQUENCY

MODE

FREQUENCY

(MHz)

SSB

9.0115

cw

9.0106

AM,

FM

9.0100

The 2nd

LO

signal (61.44

MHz)

from the

PLL

UNIT via

J4

is applied to the 2nd mixer.

The

converted 2nd

IF

signal

passes through

D4

(D35 for transmitting)

and

is applied

to the

MCF

(Fl2) to suppress unwanted signals.

The

signal output from Fl2 passes through the noise

blanker gate

(D5-D8)

and is amplified at the 2nd IF

am-

plifier (021).

The

signal enters one of the three 9 MHz

filters (Fl3, Fl4, optional

CW

narrow filter) or optional

AM

·

FM

UNIT via D52. The filters are selected with mode

selecting signals

(SSB

·CW,

AM,

CW-N)

and the "TB"

voltage line.

The signal from a 9 MHz filter

is

amplified at the 2nd

IF

amplifiers

(027-029)

and applied to the demodulator

circuit.

Dual-gate

FETs

are used

on

the 1st and 2nd

IF

amplifiers

(015, 021, 027). The 2nd gates of 015, 021 and

027

are

controlled by

AGC

bias voltage. A rapid time constant

is used for 027 to prevent raising the edge distortion of

receive signals.

R140, connected to the gate of 028, improves the

temperature characteristics of the receiver gain.

R138

adjusts the receiver gain.

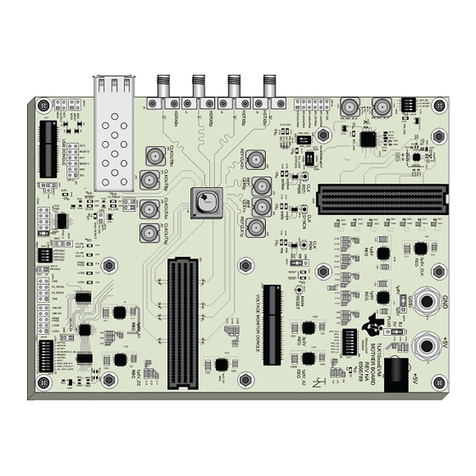

IF

CIRCUIT

AF signal SQL

IC8

BFO

SSB DET

AM

OET

062

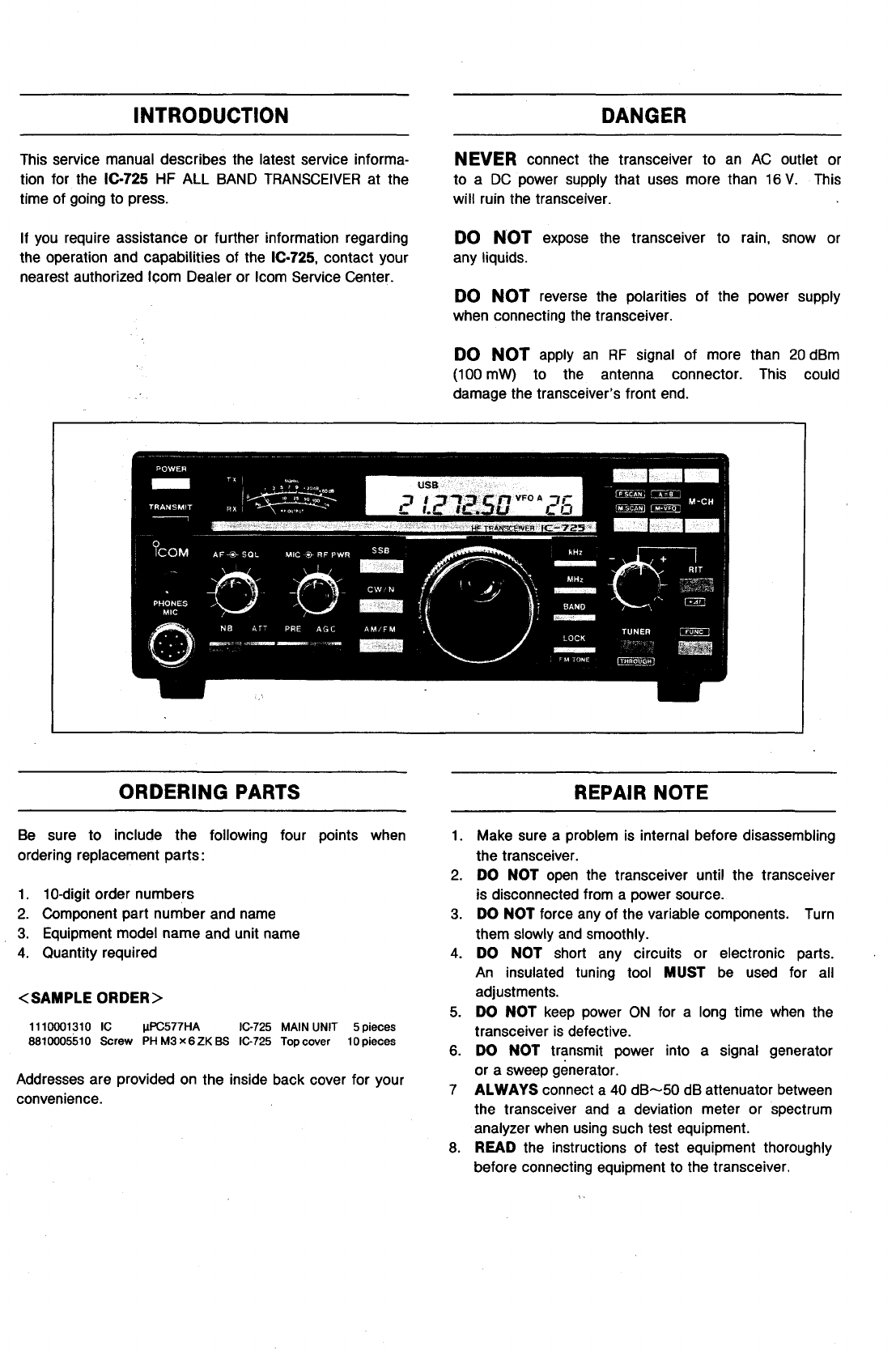

4·1·6 NOISE BLANKER CIRCUITS

(MAIN UNIT)

The

IC-725

uses a noise trigger noise blanker circuit that

cuts out pulse-type noise signals at the noise blanker gate

(D5-D8).

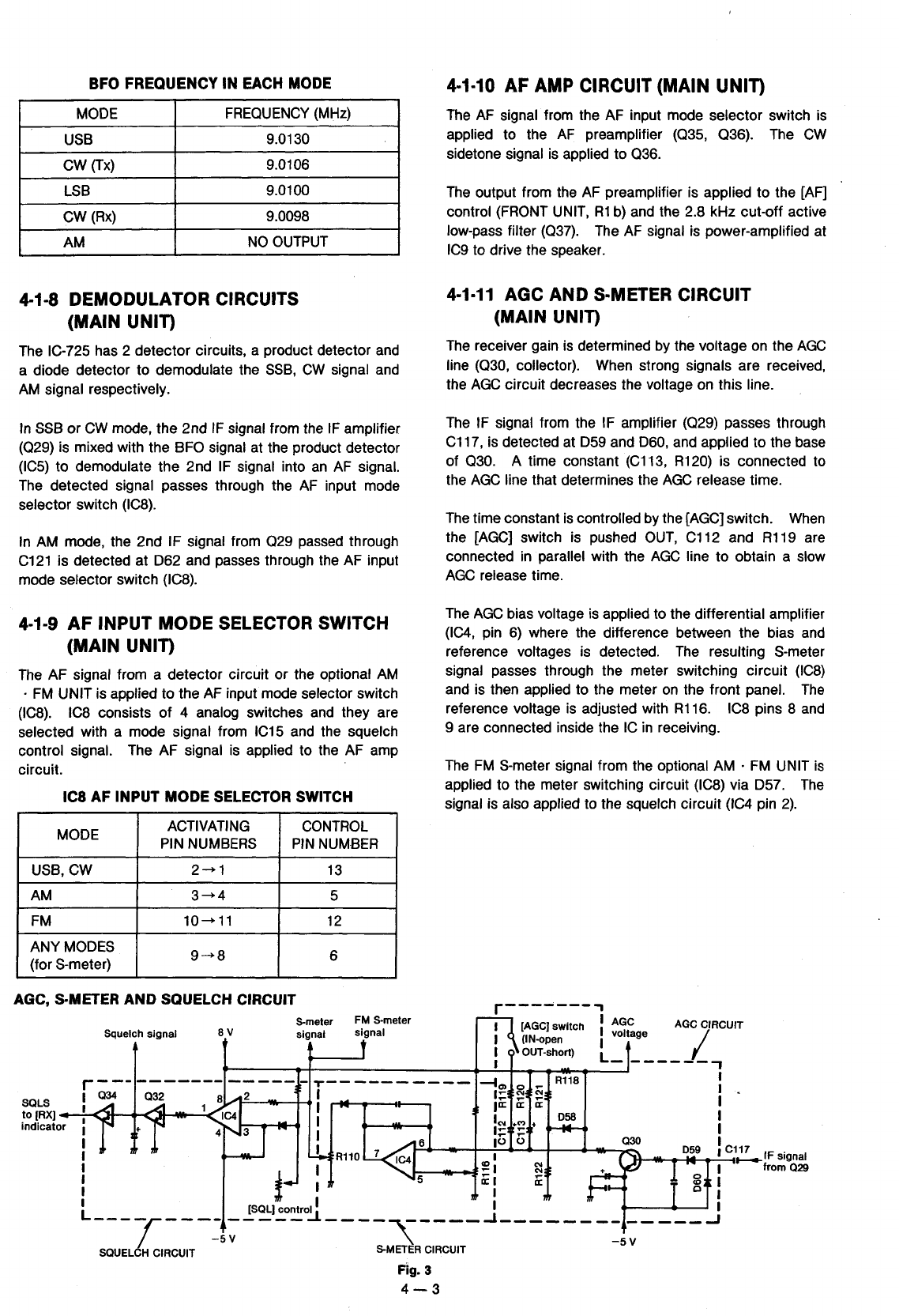

A portion of the signals from Fl2 is amplified at the noise

amplifiers (016,

IC2)

and

detected at the noise detector

(D12,

D13).

The

detected voltage from the noise detector

is applied to the noise blanker switch (019).

The threshold level of the noise blanker switch

is

set

at

0.9

V.

When the detected voltage exceeds the threshold

level,

020

outputs a blanking signal to activate the noise

blanker gate

(05-08).

A portion of the detected voltage is applied to the noise

AGC

circuit (018) and fed back to the noise amplifier

(IC2)

as noise

AGC

voltages. The time constant of the noise

AGC

circuit

is

determined by

R43,

R47

and

C60.

This

AGC

circuit does not operate to detect pulse-type noise.

When the operating frequency or mode is changed, the

"ONB"

signal line becomes "LOW," turning

020

ON.

The

noise blanker gate prevents

PLL

click noise.

4·1·7

BFO

CIRCUIT (MAIN

UNln

A 9 MHz signal oscillated at the

BFO

circuit (031,

X1)

is buffer-amplified at

042

and used at the balanced

modulator

(IC6)

and a product detector

(IC5).

The

BFO

frequency is shifted with a mode signal using

067-069.

In

USB

mode, the "USB" signal line becomes "HIGH,"

turning

ON

069.

The

frequency

is

then adjusted with

C294 to set the

USB

carrier point.

At

CW

mode transmitting, the

"CW"

signal line becomes

"HIGH"

and

033

becomes OFF, turning

ON

068.

The

frequency

is

then adjusted with

L83

to set the

CW

transmit carrier point.

In

LSB

mode, the "LSB" signal line becomes "HIGH,"

turning

ON

067. The frequency

is

then adjusted with

L82 to set the

LSB

carrier point.

NOISE

BLANKER

Fig. 2

059,

060

4-2