Infineon Technologies TC1796 User manual

User’s Manual, V2.0, July 2007

Microcontrollers

TC1796

32-Bit Single-Chip Microcontroller

Volume 1 (of 2): System Units

Volume 2 (of 2): Peripheral Units

Edition 2007-07

Published by

Infineon Technologies AG

81726 Munich, Germany

©2007 Infineon Technologies AG

All Rights Reserved.

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or

characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any

information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties

and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights

of any third party.

Information

For further information on technology, delivery terms and conditions and prices please contact your nearest

Infineon Technologies Office (www.infineon.com).

Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in

question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure

of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support

devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may

be endangered.

User’s Manual, V2.0, July 2007

Microcontrollers

TC1796

32-Bit Single-Chip Microcontroller

Volume 1 (of 2): System Units

Volume 2 (of 2): Peripheral Units

TC1796

System and Peripheral Units (Vol. 1 and 2)

User’s Manual V2.0, 2007-07

TC1796 User’s Manual

Volume 1 (of 2) System Units & Volume 2 (of 2) Peripheral Units

Revision History: V2.0, 2007-07

Previous Version: V1.0 2005-06

Page Subjects (major changes since last revision)

TC1796 User’s Manual Version 2.0 includes the contents of the TC1796 Documentation

Addendum, V1.2, Apr. 2007. Furthermore, the complete document and especially the

register description have been updated to allow document-automation processes based

on XML technologies.

Volume 1: System Units

1-20 MSC baud rate feature item is updated.

1-25 Figure 1-7 is updated.

1-34 Figure 1-11 is updated.

1-37, 1-38 Footnote marking for EBU pins is removed; pad driver class for BFCLKI

is added.

1-53 Pad driver classes for several System I/O pins are updated/added.

1-58 Table 1-6 is added.

2-10 CPU_ID is added.

2-12 MMU_CON long register name is updated.

2-13 CPS_ID is added.

2-14 CPU_SRCn.TOS bit description is updated.

2-21 Offset addresses in Table 2-6 are updated by absolute addresses.

2-26, 2-27 PMI_ID is added.

2-34, 2-35 DMI_ID is added.

3-18 Sequence of setting up the PLL after reset is updated.

4-1 Attention paragraph at the bottom is added.

4-10 Tuning Protection Section is removed.

4-24 Figure 4-6 is updated.

5-20, 5-22 Bit description of RENx is updated.

5-49 Figure 5-11 is updated.

5-61, 5-69 SCU_ID is added.

5-68 Bit description of PARAV is updated.

5-59 Bit description of ENON is updated.

TC1796

System and Peripheral Units (Vol. 1 and 2)

User’s Manual V2.0, 2007-07

6-4 Figure 6-2 is updated.

6-7, 6-8 DBCU_ID and PBCU_ID are added.

6-9 Bit description of LEC is updated.

6-16, 6-17 LFI_ID is added.

6-21 Section 6.4.3 is updated.

6-22 Figure 6-7 is updated.

6-30 BCU breakpoint Trigger Combination Logic in Figure 6-12 is updated.

6-34, 6-36 SBCU_ID and RBCU_ID are added.

7-16 DFLASH addresses in Table 7-7 are updated

7-40, 7-41,

7-42

FLASH_ID and PMU_ID are added.

7-43 Bit description of FABUSY is updated.

7-58 Footnote is added to FLASH_CON register.

8-7 Section 8.5.2 is updated.

8-10, 8-11 DMU_ID is added.

9-5, 9-7, 9-9 Short name for SBRAM and SPRAM is updated.

11-52, 11-54 PCP_ID is added.

11-59 PCP_ES bit 5 is updated.

11-74 Counter Reload Value (COPY) in Table 11-13 is updated.

11-78 Figure 11-14 is updated.

11-103 Syntax description of ST.PI is updated.

12-9 Figure 12-5 is updated.

12-10 Figure 12-6 is updated.

12-16 Section 12.1.4.5 is updated.

12-29 Figure 12-20 is updated.

12-30 Figure 12-21 is updated.

12-34 The pattern detection description in Section 12.1.9 is updated.

12-42, 12-43,

12-45

DMA_ID is added.

12-52, 12-53 Bit descriptions of CH0x/CH1x and HTRE0x/HTRE1x are updated.

TC1796 User’s Manual

Volume 1 (of 2) System Units & Volume 2 (of 2) Peripheral Units

Revision History: V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

User’s Manual V2.0, 2007-07

12-99 Address range for AEN21 is updated.

12-111,

12-112

MCHK_ID is added.

13-3 Section 13.2.1 is updated.

13-24 CONF32BIT description is updated.

13-72 BFCLKO configurations in Figure 13-27 are updated.

13-75 Burst Flash Read Cycle diagram in Figure 13-29 is added.

13-79, 13-81 EBU_ID is added.

14-13 NMI trap handler in Figure 14.5 is updated.

15-7, 15-8,

15-10

STM_ID is added.

18-16 Access modes in Table 18-7 are updated.

18-122 DBCU register adresses in Table 18-38 are updated.

Volume 2: Peripheral Units

19-19, 19-20 ASC0_ID and ASC1_ID register are added.

20-21 Note in Figure 20-11 corrected; TB write operation in

Section 20.1.2.11 is updated.

20-24, 20-31,

20-33

SSC error interrupt control in Section 20.1.2.12 and bit description

STIP, EN are updated.

20-27, 20-29 SSC0_ID and SSC1_ID registers are added.

20-37, 20-39, Notes below register SSOC and SSOTC are updated.

21-26 Figure 21-18 is updated (sampling start).

21-36, 21-38 MSC0_ID and MSC1_ID registers are added.

21-42 Bit description of NDBH is updated.

21-21, 21-25,

21-66

Values for baud rate selections corrected at several locations and

equations.

22-53 Usage of bit RXEN in Section 22.3.11.5 is updated.

22-54 First paragraph of Section 22.3.11.6 is updated.

22-59 Offset addresses for registers MSIMASK, PANCTR, MCR, and MITR in

Table 22-5 corrected.

TC1796 User’s Manual

Volume 1 (of 2) System Units & Volume 2 (of 2) Peripheral Units

Revision History: V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

User’s Manual V2.0, 2007-07

22-58, 22-59,

22-61

CAN_ID register is added.

22-60 Figure 22-24 is updated.

22-79 CPU write to LEC in last row of Table 22-7 is updated.

22-90 CAN Bus State for of NoBit and NewBit in Table 22-9 is corrected.

22-201 Configuration of CAN_FDR.DM for Equation (22.1) and

Equation (22.2) is updated.

Chapter 23 The functional description of the MLI , the module kernel description,

and operation the MLI module is completely reworked.

23-75, 23-76,

23-78

MLI0_ID and MLI1_ID registers are added.

23-3 Programmable baud rate in Section 23.1.1.1 is updated.

23-115 Register description of RPxBAR (x = 0-3) is updated.

23-129 Equation (23.6) is added.

23-142 Selected address range for AEN21 corrected.

24-31, 24-32,

24-33, 24-34

Figure 24-20, Figure 24-21, Figure 24-22, and Figure 24-23 are

updated.

24-61, 24-77 Cell Enabling on Event sections for GTC and LTC are updated.

24-76 Header of Table 24-4 is updated.

24-150,

24-151,

24-154

GPTA0_ID and GPTA1_ID registers are added.

24-233,

24-235

LTCA2_ID register is added.

24-125,

24-131

Section 24.2.6.3 “Check_Input()” and Section 24.2.6.6

“Manage_Mux()“ are updated.

24-253 Table 24-26 is updated.

24-263 Figure 24-91 is updated.

24-266 Attention paragraph at the bottom is updated.

25-9 Equation (25.1) is updated.

25-37 The reference voltage Section 25.1.5 is updated.

TC1796 User’s Manual

Volume 1 (of 2) System Units & Volume 2 (of 2) Peripheral Units

Revision History: V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

User’s Manual V2.0, 2007-07

Trademarks

TriCore® is a trademark of Infineon Technologies AG.

25-57, 25-58,

25-59

ADC0_ID register is added.

26-8 Equation (26.1) is updated.

26-27, 26-28,

26-29

FADC_ID register is added.

TC1796 User’s Manual

Volume 1 (of 2) System Units & Volume 2 (of 2) Peripheral Units

Revision History: V2.0, 2007-07

We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all?

Your feedback will help us to continuously improve the quality of this document.

Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

User’s Manual L-1 V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

Table of Contents

System Units (Vol. 1 of 2)

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1 [1]

1.1 About this Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1 [1]

1.1.1 Related Documentations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1 [1]

1.1.2 Text Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1 [1]

1.1.3 Reserved, Undefined, and Unimplemented Terminology . . . . . . . . 1-3 [1]

1.1.4 Register Access Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4 [1]

1.1.5 Abbreviations and Acronyms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5 [1]

1.2 System Architecture of the TC1796 . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8 [1]

1.2.1 TC1796 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9 [1]

1.2.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10 [1]

1.3 On-Chip Peripheral Units of the TC1796 . . . . . . . . . . . . . . . . . . . . . . 1-14 [1]

1.3.1 Serial Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14 [1]

1.3.1.1 Asynchronous/Synchronous Serial Interfaces . . . . . . . . . . . . . . 1-15 [1]

1.3.1.2 High-Speed Synchronous Serial Interfaces . . . . . . . . . . . . . . . . 1-17 [1]

1.3.1.3 Micro Second Channel Interfaces . . . . . . . . . . . . . . . . . . . . . . . 1-19 [1]

1.3.1.4 MultiCAN Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-21 [1]

1.3.1.5 Micro Link Serial Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . 1-24 [1]

1.3.2 General Purpose Timer Array . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-26 [1]

1.3.2.1 Functionality of GPTA0 and GPTA1 . . . . . . . . . . . . . . . . . . . . . 1-27 [1]

1.3.2.2 Functionality of LTCA2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-29 [1]

1.3.3 Analog-to-Digital Converters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-30 [1]

1.3.3.1 Analog-to-Digital Converters (ADC0 and ADC1) . . . . . . . . . . . . 1-30 [1]

1.3.3.2 Fast Analog-to-Digital Converter Unit (FADC) . . . . . . . . . . . . . . 1-32 [1]

1.4 TC1796 Pin Definitions and Functions . . . . . . . . . . . . . . . . . . . . . . . 1-34 [1]

1.4.1 TC1796 Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-35 [1]

1.4.2 Pad Driver Classes Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-57 [1]

1.4.3 Pull-Up/Pull-Down Behavior of the Pins . . . . . . . . . . . . . . . . . . . . 1-58 [1]

2 CPU Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1 [1]

2.1 TC1796 Processor Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1 [1]

2.2 Central Processing Unit Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2 [1]

2.2.1 CPU Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3 [1]

2.2.2 Instruction Fetch Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4 [1]

2.2.3 Execution Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5 [1]

Table of Contents

This “Table of Contents” section refers to page numbers in both parts of the TC1796

User’s Manual, the “System Units” (volume 1 with marking “[1]”) and the “Peripheral

Units” (volume 2 with marking “[2]”) parts.

User’s Manual L-2 V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

Table of Contents

2.2.4 General Purpose Register File . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6 [1]

2.3 Implementation-specific Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 [1]

2.3.1 Context Save Areas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 [1]

2.3.2 Fast Context Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 [1]

2.3.3 Reset System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 [1]

2.3.4 Program Counter Register - PC . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 [1]

2.3.5 Interrupt System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8 [1]

2.3.6 Trap System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8 [1]

2.4 TC1796 CPU Subsystem Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9 [1]

2.4.1 Core Special Function Registers (CSFR) . . . . . . . . . . . . . . . . . . . 2-10 [1]

2.4.1.1 Implementation-specific Core Special Function Registers . . . . 2-11 [1]

2.4.2 CPU Slave Interface (CPS) Registers . . . . . . . . . . . . . . . . . . . . . . 2-13 [1]

2.4.2.1 Implementation-specific CPU Slave Interface Registers . . . . . . 2-14 [1]

2.4.3 CPU General Purpose Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15 [1]

2.4.4 Core Debug Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17 [1]

2.4.4.1 Implementation-specific Core Debug Registers . . . . . . . . . . . . 2-18 [1]

2.4.5 Memory Protection Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20 [1]

2.4.5.1 Implementation-specific Memory Protection Registers . . . . . . . 2-23 [1]

2.5 Program Memory Interface (PMI) . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24 [1]

2.5.1 PMI Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24 [1]

2.5.2 Parity Protection for PMI Memories . . . . . . . . . . . . . . . . . . . . . . . . 2-25 [1]

2.5.3 PMI Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26 [1]

2.5.3.1 PMI Module Identification Register . . . . . . . . . . . . . . . . . . . . . . 2-27 [1]

2.5.3.2 PMI Control Register 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-28 [1]

2.5.3.3 PMI Control Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-29 [1]

2.5.3.4 PMI Control Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30 [1]

2.6 Data Memory Interface (DMI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-31 [1]

2.6.1 DMI Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-31 [1]

2.6.2 Dual-Ported Memory Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32 [1]

2.6.2.1 CPU Buffer Write Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32 [1]

2.6.3 Parity Protection for DMI Memories . . . . . . . . . . . . . . . . . . . . . . . . 2-33 [1]

2.6.4 DMI Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34 [1]

2.6.4.1 DMI Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-35 [1]

2.7 Instruction Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-40 [1]

2.7.1 Integer-Pipeline Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-41 [1]

2.7.1.1 Simple Arithmetic Instruction Timings . . . . . . . . . . . . . . . . . . . . 2-41 [1]

2.7.1.2 Multiply Instruction Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-45 [1]

2.7.1.3 MAC Instruction Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-46 [1]

2.7.1.4 Control Flow Instruction Timing . . . . . . . . . . . . . . . . . . . . . . . . . 2-47 [1]

2.7.2 Load-Store Pipeline Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . 2-48 [1]

2.7.2.1 Address Arithmetic Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-48 [1]

2.7.2.2 Control Flow Instruction Timing . . . . . . . . . . . . . . . . . . . . . . . . . 2-49 [1]

2.7.2.3 Load Instruction Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-50 [1]

User’s Manual L-3 V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

Table of Contents

2.7.2.4 Store Instruction Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-51 [1]

2.8 Floating Point Pipeline Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-52 [1]

3 Clock System and Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1 [1]

3.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1 [1]

3.2 Clock Generation Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3 [1]

3.2.1 Main Oscillator Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4 [1]

3.2.1.1 Oscillator Bypass Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5 [1]

3.2.1.2 Oscillator Run Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6 [1]

3.2.1.3 Oscillator Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7 [1]

3.2.1.4 Oscillator Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8 [1]

3.2.2 Phase Looked Loop (PLL) Circuitry . . . . . . . . . . . . . . . . . . . . . . . . 3-10 [1]

3.2.2.1 Clock Source Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10 [1]

3.2.2.2 PLL Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12 [1]

3.2.2.3 PLL Clock Control and Status Register . . . . . . . . . . . . . . . . . . . 3-16 [1]

3.2.2.4 Changing PLL Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18 [1]

3.2.2.5 Setting up the PLL after Reset . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18 [1]

3.2.2.6 Lock Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19 [1]

3.2.2.7 Loss-of-Lock Recovery . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19 [1]

3.2.3 Power-on Startup Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21 [1]

3.3 Module Power Management and Clock Gating . . . . . . . . . . . . . . . . . 3-22 [1]

3.3.1 Module Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23 [1]

3.3.2 Clock Control Register CLC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24 [1]

3.3.3 Fractional Divider Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-29 [1]

3.3.3.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-29 [1]

3.3.3.2 Fractional Divider Operating Modes . . . . . . . . . . . . . . . . . . . . . 3-32 [1]

3.3.3.3 Fractional Divider Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-35 [1]

3.3.4 Module Clock Register Implementations . . . . . . . . . . . . . . . . . . . . 3-39 [1]

3.3.5 Fractional Divider Register Implementations . . . . . . . . . . . . . . . . . 3-40 [1]

3.4 System Clock Output Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-41 [1]

3.4.1 System Clock Fractional Divider Register . . . . . . . . . . . . . . . . . . . 3-42 [1]

4 Reset and Boot Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1 [1]

4.1 Reset and Boot Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1 [1]

4.1.1 Reset Status and Control Registers . . . . . . . . . . . . . . . . . . . . . . . . 4-3 [1]

4.1.1.1 Reset Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3 [1]

4.1.1.2 Reset Request Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5 [1]

4.2 Reset Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7 [1]

4.2.1 Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7 [1]

4.2.2 External Hardware Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7 [1]

4.2.3 Software Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8 [1]

4.2.4 Watchdog Timer Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8 [1]

4.2.5 Debug System Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10 [1]

4.2.6 Module Reset Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10 [1]

User’s Manual L-4 V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

Table of Contents

4.2.7 Booting Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12 [1]

4.2.7.1 Normal Boot Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-14 [1]

4.2.7.2 Debug Boot Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15 [1]

4.3 Boot ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16 [1]

4.3.1 Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16 [1]

4.3.2 Program Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16 [1]

4.3.3 Initial State after Boot ROM Exit . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19 [1]

4.4 Bootstrap Loader (BSL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-20 [1]

4.4.1 Bootstrap Loader Mode 1 - ASC Boot via ASC0 Pins . . . . . . . . . . 4-21 [1]

4.4.2 Bootstrap Loader Mode 2 - CAN Boot via CAN Pins . . . . . . . . . . . 4-24 [1]

4.4.3 Bootstrap Loader Mode 3 - ASC Boot via CAN Pins . . . . . . . . . . . 4-28 [1]

4.4.4 Alternate Boot Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28 [1]

5 System Control Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1 [1]

5.1 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2 [1]

5.1.1 Power Management Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2 [1]

5.1.2 Power Management Control and Status Register, PMG_CSR . . . . 5-3 [1]

5.1.3 Power Management Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5 [1]

5.1.3.1 Idle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5 [1]

5.1.3.2 Sleep Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6 [1]

5.1.3.3 States of TC1796 Units in Power Management Modes . . . . . . . . 5-7 [1]

5.2 Configuration Input Sampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8 [1]

5.3 External Request Unit (ERU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9 [1]

5.3.1 Input Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10 [1]

5.3.2 Output Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12 [1]

5.3.3 External Request Unit Implementation . . . . . . . . . . . . . . . . . . . . . 5-14 [1]

5.3.4 External Request Unit Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16 [1]

5.4 Special System Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-35 [1]

5.4.1 FPU Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-35 [1]

5.4.2 Flash Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-36 [1]

5.4.3 External Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-36 [1]

5.5 SRAM Parity Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-37 [1]

5.5.1 Parity Error Trap Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-39 [1]

5.6 Pad Driver Temperature Compensation Control . . . . . . . . . . . . . . . . 5-41 [1]

5.6.1 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-41 [1]

5.6.2 Temperature Compensation Registers . . . . . . . . . . . . . . . . . . . . . 5-44 [1]

5.7 Die Temperature Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-48 [1]

5.8 GPTA1 Input IN1 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-49 [1]

5.9 Pad Test Mode Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-50 [1]

5.9.1 Pad Test Mode Enabling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-51 [1]

5.9.2 Pad Test Mode Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-51 [1]

5.10 Emergency Stop Output Control for GPTA and MSC . . . . . . . . . . . . 5-57 [1]

5.10.1 GPTA Output Emergency Control in the GPIO Ports . . . . . . . . . . 5-58 [1]

User’s Manual L-5 V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

Table of Contents

5.10.2 MSC Emergency Control Selection . . . . . . . . . . . . . . . . . . . . . . . . 5-58 [1]

5.10.3 Emergency Stop Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-59 [1]

5.11 Analog Input 7 Testmode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-60 [1]

5.12 SCU Registers and Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-61 [1]

5.13 Miscellaneous SCU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-64 [1]

5.13.1 SCU Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-64 [1]

5.13.2 SCU Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-67 [1]

5.13.3 Device Identification Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-69 [1]

6 On-Chip System Buses and Bus Bridges . . . . . . . . . . . . . . . . . . . . 6-1 [1]

6.1 Program and Data Local Memory Buses . . . . . . . . . . . . . . . . . . . . . . 6-2 [1]

6.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2 [1]

6.1.2 Transaction Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3 [1]

6.1.2.1 Single Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3 [1]

6.1.2.2 Block Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3 [1]

6.1.2.3 Atomic Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3 [1]

6.1.3 Address Alignment Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3 [1]

6.1.4 Reaction of a Busy Slave . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3 [1]

6.1.5 LMB Basic Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4 [1]

6.2 Local Memory Bus Controller Units . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5 [1]

6.2.1 Basic Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5 [1]

6.2.2 LMB Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5 [1]

6.2.2.1 LMB Bus Default Master . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6 [1]

6.2.3 LMB Bus Error Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6 [1]

6.2.4 DLMB and PLMB Bus Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7 [1]

6.3 Local Memory to FPI Bus Interface (LFI Bridge) . . . . . . . . . . . . . . . . 6-15 [1]

6.3.1 Functional Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-15 [1]

6.3.2 LFI Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-16 [1]

6.4 System and Remote Peripheral Bus . . . . . . . . . . . . . . . . . . . . . . . . . 6-19 [1]

6.4.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-19 [1]

6.4.2 Bus Transaction Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-21 [1]

6.4.3 Reaction of a Busy Slave . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-21 [1]

6.4.4 Address Alignment Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-22 [1]

6.4.5 FPI Bus Basic Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-22 [1]

6.5 FPI Bus Control Units (SBCU and RBCU) . . . . . . . . . . . . . . . . . . . . . 6-24 [1]

6.5.1 FPI Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-24 [1]

6.5.1.1 Arbitration on the System Peripheral Bus . . . . . . . . . . . . . . . . . 6-24 [1]

6.5.1.2 Arbitration on the Remote Peripheral Bus . . . . . . . . . . . . . . . . . 6-24 [1]

6.5.1.3 Starvation Prevention . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-25 [1]

6.5.2 FPI Bus Error Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-25 [1]

6.5.3 Clock Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-27 [1]

6.5.4 BCU Debug Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-28 [1]

6.5.4.1 Address Triggers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-28 [1]

User’s Manual L-6 V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

Table of Contents

6.5.4.2 Signal Status Triggers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29 [1]

6.5.4.3 Grant Triggers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29 [1]

6.5.4.4 Combination of Triggers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-30 [1]

6.5.4.5 BCU Breakpoint Generation Examples . . . . . . . . . . . . . . . . . . . 6-31 [1]

6.5.5 SBCU and RBCU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-34 [1]

6.5.5.1 BCU Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-36 [1]

6.5.5.2 BCU Error Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-38 [1]

6.5.5.3 OCDS Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-42 [1]

6.5.5.4 BCU Service Request Control Register . . . . . . . . . . . . . . . . . . . 6-58 [1]

7 Program Memory Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1 [1]

7.1 Boot ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1 [1]

7.2 Program & Data Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2 [1]

7.2.1 Program Flash Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4 [1]

7.2.2 Data Flash Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7 [1]

7.2.3 User Configuration Blocks Overview . . . . . . . . . . . . . . . . . . . . . . . . 7-9 [1]

7.2.4 Basic Flash Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11 [1]

7.2.4.1 Read Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11 [1]

7.2.4.2 Command Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12 [1]

7.2.4.3 Page Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-13 [1]

7.2.5 Command Sequence Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14 [1]

7.2.5.1 Reset-to-Read Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-15 [1]

7.2.5.2 Enter Page Mode Command . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-15 [1]

7.2.5.3 Load Page Buffer Command . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16 [1]

7.2.5.4 Write Page Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18 [1]

7.2.5.5 Write User Configuration Page Command . . . . . . . . . . . . . . . . 7-19 [1]

7.2.5.6 Erase Sector Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-20 [1]

7.2.5.7 Erase User Configuration Block Command . . . . . . . . . . . . . . . . 7-22 [1]

7.2.5.8 Disable Write Protection Command . . . . . . . . . . . . . . . . . . . . . . 7-23 [1]

7.2.5.9 Disable Read Protection Command . . . . . . . . . . . . . . . . . . . . . 7-24 [1]

7.2.5.10 Resume Protection Command . . . . . . . . . . . . . . . . . . . . . . . . . . 7-24 [1]

7.2.5.11 Clear Status Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-25 [1]

7.2.6 Data Flash and EEPROM Emulation . . . . . . . . . . . . . . . . . . . . . . . 7-26 [1]

7.2.7 Read and Write Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-27 [1]

7.2.7.1 User Configuration Block Definitions . . . . . . . . . . . . . . . . . . . . . 7-27 [1]

7.2.7.2 Write and OTP Protection for PFLASH . . . . . . . . . . . . . . . . . . . 7-30 [1]

7.2.7.3 Read Protection for PFLASH and DFLASH . . . . . . . . . . . . . . . . 7-32 [1]

7.2.7.4 Password Check Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-33 [1]

7.2.8 Error Correction and Margin Control . . . . . . . . . . . . . . . . . . . . . . . 7-34 [1]

7.2.8.1 Dynamic Error Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-34 [1]

7.2.8.2 Margin Check Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-35 [1]

7.2.9 Flash Interrupt Generation and Control . . . . . . . . . . . . . . . . . . . . . 7-36 [1]

7.2.10 Flash Power Supply, Power Saving and Reset . . . . . . . . . . . . . . . 7-38 [1]

User’s Manual L-7 V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

Table of Contents

7.2.10.1 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-38 [1]

7.2.10.2 Sleep Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-38 [1]

7.2.10.3 Shut-Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-38 [1]

7.2.10.4 Reset Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-39 [1]

7.2.11 Flash Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-40 [1]

7.2.11.1 Flash and PMU Module Identification Registers . . . . . . . . . . . . 7-41 [1]

7.2.11.2 Flash Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-43 [1]

7.2.11.3 Margin Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-51 [1]

7.2.11.4 Flash Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-53 [1]

7.2.11.5 Protection Configuration Registers . . . . . . . . . . . . . . . . . . . . . . 7-59 [1]

7.3 Emulation Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-61 [1]

8 Data Memory Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1 [1]

8.1 DLMB/PLMB Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2 [1]

8.2 SBRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2 [1]

8.3 SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2 [1]

8.4 Parity Protection for DMU Memories . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3 [1]

8.5 Data Access Overlay Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3 [1]

8.5.1 Internal Overlay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7 [1]

8.5.2 Emulation Memory Overlay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7 [1]

8.5.3 Switching between Internal and Emulation Memory Overlay . . . . . 8-7 [1]

8.5.4 Region Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7 [1]

8.5.5 Access Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7 [1]

8.6 Program Local Memory Bus Interface (LMI) . . . . . . . . . . . . . . . . . . . . 8-8 [1]

8.6.1 Data Read Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-8 [1]

8.7 DMU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-10 [1]

9 Memory Maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1 [1]

9.1 How to Read the Address Maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1 [1]

9.2 Contents of the Segments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4 [1]

9.3 Address Map of the FPI Bus System . . . . . . . . . . . . . . . . . . . . . . . . . . 9-6 [1]

9.3.1 Segments 0 to 14 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-6 [1]

9.3.2 Segment 15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-10 [1]

9.4 Address Map of the Program Local Memory Bus (PLMB) . . . . . . . . . 9-15 [1]

9.5 Address Map of the Data Local Memory Bus (DLMB) . . . . . . . . . . . . 9-19 [1]

9.6 Memory Module Access Restrictions . . . . . . . . . . . . . . . . . . . . . . . . . 9-22 [1]

10 General Purpose I/O Ports and Peripheral I/O Lines . . . . . . . . . . 10-1 [1]

10.1 Basic Port Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-2 [1]

10.2 Port Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-5 [1]

10.2.1 Port Input/Output Control Registers . . . . . . . . . . . . . . . . . . . . . . . . 10-7 [1]

10.2.2 Pad Driver Mode Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-10 [1]

10.2.3 Port Output Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-13 [1]

10.2.4 Port Output Modification Register . . . . . . . . . . . . . . . . . . . . . . . . 10-14 [1]

User’s Manual L-8 V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

Table of Contents

10.2.5 Emergency Stop Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-16 [1]

10.2.6 Port Input Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-17 [1]

10.3 Port 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-18 [1]

10.3.1 Port 0 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-18 [1]

10.3.2 Port 0 Function Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-19 [1]

10.3.3 Port 0 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-22 [1]

10.3.3.1 Port 0 Pad Driver Mode Register and Pad Classes . . . . . . . . . 10-23 [1]

10.3.3.2 Port 0 Software Configuration Selection . . . . . . . . . . . . . . . . . 10-24 [1]

10.3.3.3 Reserved SWOPT Bits of SCU_SCLIR Register . . . . . . . . . . . 10-25 [1]

10.4 Port 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-26 [1]

10.4.1 Port 1 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-26 [1]

10.4.2 Port 1 Function Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-27 [1]

10.4.3 Port 1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-30 [1]

10.4.3.1 Port 1 Pad Driver Mode Register and Pad Classes . . . . . . . . . 10-31 [1]

10.5 Port 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-32 [1]

10.5.1 Port 2 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-32 [1]

10.5.2 Port 2 Function Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-33 [1]

10.5.3 Port 2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-37 [1]

10.5.3.1 Port 2 Output Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-37 [1]

10.5.3.2 Port 2 Output Modification Register . . . . . . . . . . . . . . . . . . . . . 10-37 [1]

10.5.3.3 Port 2 Input/Output Control Register 0 . . . . . . . . . . . . . . . . . . 10-38 [1]

10.5.3.4 Port 2 Input Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-38 [1]

10.5.3.5 Port 2 Emergency Stop Register . . . . . . . . . . . . . . . . . . . . . . . 10-38 [1]

10.5.3.6 Port 2 Pad Driver Mode Register and Pad Classes . . . . . . . . . 10-39 [1]

10.6 Port 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-40 [1]

10.6.1 Port 3 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-40 [1]

10.6.2 Port 3 Function Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-41 [1]

10.6.3 Port 3 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-45 [1]

10.6.3.1 Port 3 Pad Driver Mode Register and Pad Classes . . . . . . . . . 10-46 [1]

10.7 Port 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-47 [1]

10.7.1 Port 4 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-47 [1]

10.7.2 Port 4 Function Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-48 [1]

10.7.3 Port 4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-51 [1]

10.7.3.1 Port 4 Pad Driver Mode Register and Pad Classes . . . . . . . . . 10-53 [1]

10.8 Port 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-54 [1]

10.8.1 Port 5 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-54 [1]

10.8.2 Port 5 Function Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-55 [1]

10.8.3 Port 5 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-57 [1]

10.8.3.1 Port 5 Output Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-57 [1]

10.8.3.2 Port 5 Output Modification Register . . . . . . . . . . . . . . . . . . . . . 10-57 [1]

10.8.3.3 Port 5 Input Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-57 [1]

10.8.3.4 Port 5 Pad Driver Mode Register and Pad Classes . . . . . . . . . 10-58 [1]

10.9 Port 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-59 [1]

User’s Manual L-9 V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

Table of Contents

10.9.1 Port 6 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-59 [1]

10.9.2 Port 6 Function Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-60 [1]

10.9.3 Port 6 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-63 [1]

10.9.3.1 Port 6 Output Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-63 [1]

10.9.3.2 Port 6 Output Modification Register . . . . . . . . . . . . . . . . . . . . . 10-63 [1]

10.9.3.3 Port 6 Input Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-63 [1]

10.9.3.4 Port 6 Pad Driver Mode Register and Pad Classes . . . . . . . . . 10-64 [1]

10.10 Port 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-65 [1]

10.10.1 Port 7 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-65 [1]

10.10.2 Port 7 Function Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-66 [1]

10.10.3 Port 7 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-68 [1]

10.10.3.1 Port 7 Output Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-68 [1]

10.10.3.2 Port 7 Output Modification Register . . . . . . . . . . . . . . . . . . . . . 10-68 [1]

10.10.3.3 Port 7 Input Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-68 [1]

10.10.3.4 Port 7 Pad Driver Mode Register and Pad Classes . . . . . . . . . 10-69 [1]

10.11 Port 8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-70 [1]

10.11.1 Port 8 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-70 [1]

10.11.2 Port 8 Function Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-71 [1]

10.11.3 Port 8 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-73 [1]

10.11.3.1 Port 8 Output Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-73 [1]

10.11.3.2 Port 8 Output Modification Register . . . . . . . . . . . . . . . . . . . . . 10-73 [1]

10.11.3.3 Port 8 Input Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-73 [1]

10.11.3.4 Port 8 Emergency Stop Register . . . . . . . . . . . . . . . . . . . . . . . 10-73 [1]

10.11.3.5 Port 8 Pad Driver Mode Register and Pad Classes . . . . . . . . . 10-74 [1]

10.12 Port 9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-75 [1]

10.12.1 Port 9 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-75 [1]

10.12.2 Port 9 Function Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-76 [1]

10.12.3 Port 9 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-78 [1]

10.12.3.1 Port 9 Output Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-78 [1]

10.12.3.2 Port 9 Output Modification Register . . . . . . . . . . . . . . . . . . . . . 10-78 [1]

10.12.3.3 Port 9 Input/Output Control Register 8 . . . . . . . . . . . . . . . . . . 10-79 [1]

10.12.3.4 Port 9 Input Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-79 [1]

10.12.3.5 Port 9 Emergency Stop Register . . . . . . . . . . . . . . . . . . . . . . . 10-79 [1]

10.12.3.6 Port 9 Pad Driver Mode Register and Pad Classes . . . . . . . . . 10-80 [1]

10.13 Port 10 (Hardware Select Inputs) . . . . . . . . . . . . . . . . . . . . . . . . . . 10-81 [1]

10.13.1 Port 10 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-81 [1]

10.13.2 Port 10 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-82 [1]

10.13.2.1 Port 10 Input Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-82 [1]

10.14 Dedicated Peripheral I/O Lines . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-83 [1]

10.14.1 Dedicated I/O Lines for SSC0 and SSC1 . . . . . . . . . . . . . . . . . . 10-83 [1]

10.14.2 LVDS Outputs of MSC0 and MSC1 . . . . . . . . . . . . . . . . . . . . . . . 10-85 [1]

User’s Manual L-10 V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

Table of Contents

11 Peripheral Control Processor (PCP) . . . . . . . . . . . . . . . . . . . . . . . 11-1 [1]

11.1 Peripheral Control Processor Overview . . . . . . . . . . . . . . . . . . . . . . . 11-1 [1]

11.2 PCP Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-2 [1]

11.2.1 PCP Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-3 [1]

11.2.2 PCP Code Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-4 [1]

11.2.3 PCP Parameter RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-4 [1]

11.2.4 FPI Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-4 [1]

11.2.5 PCP Interrupt Control Unit and Service Request Nodes . . . . . . . 11-5 [1]

11.3 PCP Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-6 [1]

11.3.1 General Purpose Register Set of the PCP . . . . . . . . . . . . . . . . . . 11-6 [1]

11.3.1.1 Register R0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-7 [1]

11.3.1.2 Registers R1, R2, and R3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-7 [1]

11.3.1.3 Registers R4 and R5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-7 [1]

11.3.1.4 Register R6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-8 [1]

11.3.1.5 Register R7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-9 [1]

11.3.2 Contexts and Context Models . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-11 [1]

11.3.2.1 Context Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-11 [1]

11.3.2.2 Context Save Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-14 [1]

11.3.2.3 Context Restore Operation for CR6 and CR7 . . . . . . . . . . . . . 11-17 [1]

11.3.2.4 Context Save Operation for CR6 and CR7 . . . . . . . . . . . . . . . 11-21 [1]

11.3.2.5 Initialization of the Contexts . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-24 [1]

11.3.2.6 Context Save Optimization . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-24 [1]

11.3.3 Channel Programs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-25 [1]

11.3.3.1 Channel Restart Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-25 [1]

11.3.3.2 Channel Resume Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-26 [1]

11.4 PCP Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-28 [1]

11.4.1 PCP Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-28 [1]

11.4.2 Channel Invocation and Context Restore Operation . . . . . . . . . . 11-28 [1]

11.4.3 Channel Exit and Context Save Operation . . . . . . . . . . . . . . . . . 11-29 [1]

11.4.3.1 Normal Exit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-29 [1]

11.4.3.2 Error Condition Channel Exit . . . . . . . . . . . . . . . . . . . . . . . . . . 11-30 [1]

11.4.3.3 Debug Exit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-31 [1]

11.5 PCP Interrupt Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-32 [1]

11.5.1 Issuing Service Requests to CPU or PCP . . . . . . . . . . . . . . . . . . 11-32 [1]

11.5.2 PCP Interrupt Control Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-33 [1]

11.5.3 PCP Service Request Nodes . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-33 [1]

11.5.4 Issuing PCP Service Requests . . . . . . . . . . . . . . . . . . . . . . . . . . 11-34 [1]

11.5.4.1 Service Request on EXIT Instruction . . . . . . . . . . . . . . . . . . . . 11-35 [1]

11.5.4.2 Service Request on Suspension of Interrupt . . . . . . . . . . . . . . 11-35 [1]

11.5.4.3 Service Request on Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-36 [1]

11.5.4.4 Queue Full Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-36 [1]

11.6 PCP Error Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-38 [1]

11.6.1 Enforced PRAM Partitioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-38 [1]

User’s Manual L-11 V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

Table of Contents

11.6.2 Channel Watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-39 [1]

11.6.3 Invalid Opcode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-39 [1]

11.6.4 Instruction Address Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-39 [1]

11.7 Instruction Set Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-40 [1]

11.7.1 DMA Primitives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-40 [1]

11.7.2 Load and Store . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-41 [1]

11.7.3 Arithmetic and Logical Instructions . . . . . . . . . . . . . . . . . . . . . . . 11-42 [1]

11.7.4 Bit Manipulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-44 [1]

11.7.5 Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-44 [1]

11.7.6 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-45 [1]

11.7.6.1 FPI Bus Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-45 [1]

11.7.6.2 PRAM Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-46 [1]

11.7.6.3 Bit Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-46 [1]

11.7.6.4 Flow Control Destination Addressing . . . . . . . . . . . . . . . . . . . . 11-46 [1]

11.8 Accessing PCP Resources from the FPI Bus . . . . . . . . . . . . . . . . . 11-48 [1]

11.8.1 Access to the PCP Control Registers . . . . . . . . . . . . . . . . . . . . . 11-48 [1]

11.8.2 Access to the PRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-48 [1]

11.8.3 Access to the CMEM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-49 [1]

11.9 Debugging the PCP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-50 [1]

11.10 PCP Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-52 [1]

11.10.1 Module Identification Register, PCP_ID . . . . . . . . . . . . . . . . . . . 11-54 [1]

11.10.2 PCP Clock Control Register, PCP_CLC . . . . . . . . . . . . . . . . . . . 11-55 [1]

11.10.3 PCP Control and Status Register, PCP_CS . . . . . . . . . . . . . . . . 11-56 [1]

11.10.4 PCP Error/Debug Status Register, PCP_ES . . . . . . . . . . . . . . . . 11-59 [1]

11.10.5 PCP Interrupt Control Register, PCP_ICR . . . . . . . . . . . . . . . . . 11-61 [1]

11.10.6 PCP Interrupt Threshold Register, PCP_ITR . . . . . . . . . . . . . . . 11-63 [1]

11.10.7 PCP Interrupt Configuration Register, PCP_ICON . . . . . . . . . . . 11-64 [1]

11.10.8 PCP Stall Status Register, PCP_SSR . . . . . . . . . . . . . . . . . . . . . 11-66 [1]

11.10.9 PCP Service Request Control Registers, PCP_SRC[1:0] . . . . . . 11-67 [1]

11.10.10 PCP Service Request Control Registers, PCP_SRC[3:2] . . . . . . 11-68 [1]

11.10.11 PCP Service Request Control Registers, PCP_SRC[8:4] . . . . . . 11-69 [1]

11.10.12 PCP Service Request Control Registers, PCP_SRC[11:9] . . . . . 11-70 [1]

11.11 PCP Instruction Set Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-72 [1]

11.11.1 Instruction Codes and Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-72 [1]

11.11.1.1 Conditional Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-73 [1]

11.11.1.2 Instruction Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-74 [1]

11.11.2 Counter Operation for COPY Instruction . . . . . . . . . . . . . . . . . . . 11-77 [1]

11.11.3 Counter Operation for BCOPY Instruction . . . . . . . . . . . . . . . . . . 11-78 [1]

11.11.4 Divide and Multiply Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . 11-79 [1]

11.11.5 ADD, 32-Bit Addition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-80 [1]

11.11.6 BCOPY, DMA Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-81 [1]

11.11.7 AND, 32-Bit Logical AND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-82 [1]

11.11.8 CHKB, Check Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-83 [1]

User’s Manual L-12 V2.0, 2007-07

TC1796

System and Peripheral Units (Vol. 1 and 2)

Table of Contents

11.11.9 CLR, Clear Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-83 [1]

11.11.10 COMP, 32-Bit Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-84 [1]

11.11.11 COPY, DMA Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-85 [1]

11.11.12 DEBUG, Debug Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-86 [1]

11.11.13 DINIT, Divide Initialization Instruction . . . . . . . . . . . . . . . . . . . . . 11-87 [1]

11.11.14 DSTEP, Divide Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-88 [1]

11.11.15 INB, Insert Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-88 [1]

11.11.16 EXIT, Exit Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-89 [1]

11.11.17 JC, Jump Conditionally . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-90 [1]

11.11.18 JL, Jump Long Unconditional . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-91 [1]

11.11.19 LD, Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-91 [1]

11.11.20 LDL, Load 16-bit Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-93 [1]

11.11.21 Multiply Initialization Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . 11-93 [1]

11.11.22 MOV, Move Register to Register . . . . . . . . . . . . . . . . . . . . . . . . . 11-94 [1]

11.11.23 Multiply Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-95 [1]

11.11.24 NEG, Negate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-96 [1]

11.11.25 NOP, No Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-96 [1]

11.11.26 NOT, Logical NOT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-96 [1]

11.11.27 OR, Logical OR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-97 [1]

11.11.28 PRI, Prioritize . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-98 [1]

11.11.29 PRAM Bit Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-99 [1]

11.11.30 RL, Rotate Left . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-100 [1]

11.11.31 RR, Rotate Right . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-100 [1]

11.11.32 SET, Set Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-101 [1]

11.11.33 SHL, Shift Left . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-101 [1]

11.11.34 SHR, Shift Right . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-102 [1]

11.11.35 ST, Store . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-103 [1]

11.11.36 SUB, 32-Bit Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-104 [1]

11.11.37 XCH, Exchange . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-105 [1]

11.11.38 XOR, 32-Bit Logical Exclusive OR . . . . . . . . . . . . . . . . . . . . . . . 11-106 [1]

11.11.39 Flag Updates of Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-107 [1]

11.11.40 Instruction Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-108 [1]

11.12 Programming of the PCP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-112 [1]

11.12.1 Initial PC of a channel program . . . . . . . . . . . . . . . . . . . . . . . . . 11-112 [1]

11.12.1.1 Channel Entry Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-112 [1]

11.12.1.2 Channel Resume . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-113 [1]

11.12.2 Channel Management for Small and Minimum Contexts . . . . . 11-114 [1]

11.12.3 Unused Registers as Globals or Constants . . . . . . . . . . . . . . . . 11-114 [1]

11.12.4 Dispatch of Low Priority Tasks . . . . . . . . . . . . . . . . . . . . . . . . . 11-115 [1]

11.12.5 Code Reuse Across Channels (Call and Return) . . . . . . . . . . . 11-115 [1]

11.12.6 Case-like Code Switches (Computed Go-To) . . . . . . . . . . . . . . 11-116 [1]

11.12.7 Simple DMA Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-116 [1]

11.12.7.1 COPY Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-116 [1]

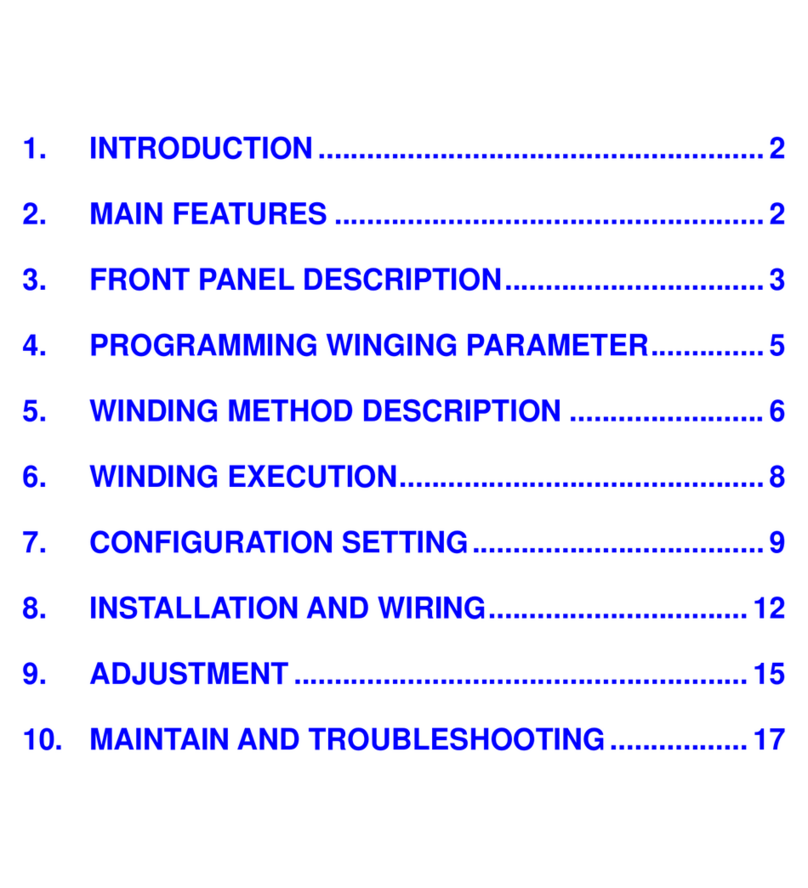

Table of contents

Other Infineon Technologies Controllers manuals

Popular Controllers manuals by other brands

TAILY AUTOMATION

TAILY AUTOMATION CNC-210A user manual

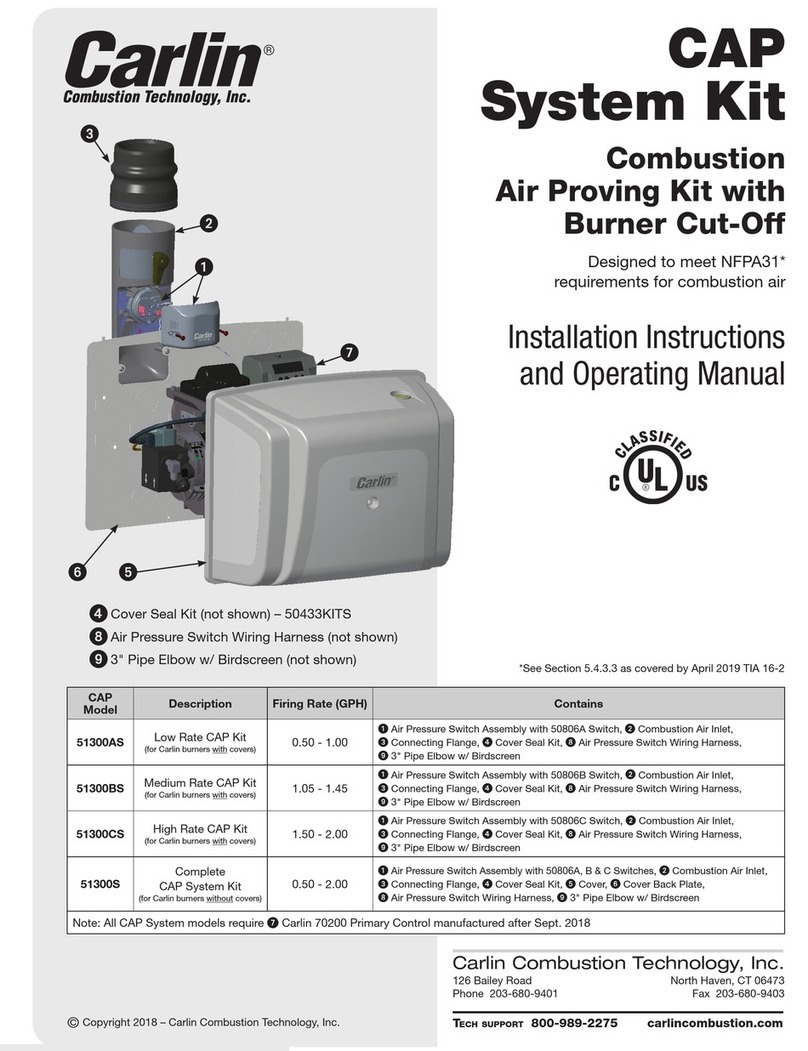

Carlin

Carlin 51300AS Installation instructions & operating manual

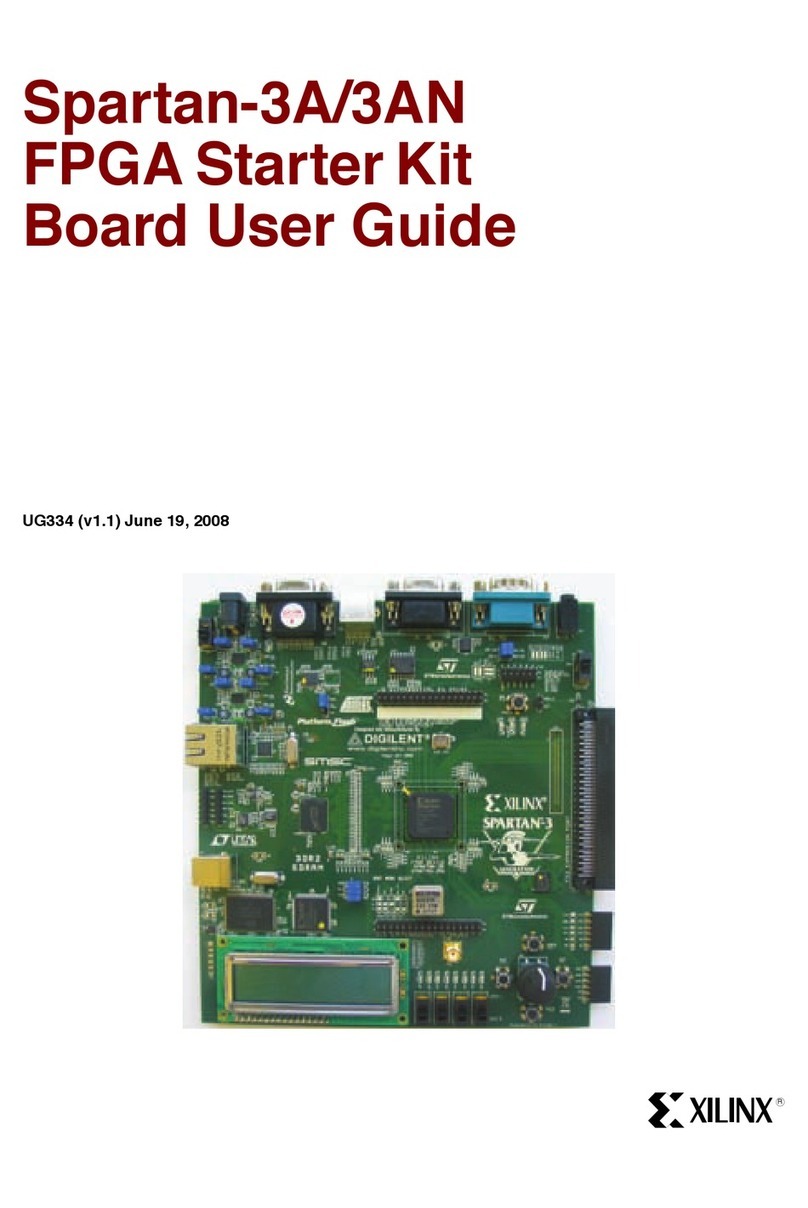

Xilinx

Xilinx Spartan-3A DSP FPGA Series user guide

Auber

Auber WS Series Operation & instruction manual

Mitsubishi Electric

Mitsubishi Electric MELSEC FX3U-232ADP-MB installation manual

NXP Semiconductors

NXP Semiconductors LPC1768 user manual