9

c. Replace ".source_export ({reconfig_rst, ISSP_sw[3:0]}), // source.export" with

".source_export ({sdi_clk_sel,reconfig_rst, ISSP_sw[3:0]}), // source.export" in the

a10_top.v

d. Add “set_location_assignment PIN_AL22 -to si516_fs” to a10_top.qsf

3. Perform full compilation with the design

4. Program the SOF file generated into the Arria 10 SoC Development Kit

5. After the programming is completed, open the Spf_sample_design_ttk.spf file and establish

connection to the device

6. Click on the Continuously Read Probe Data to start signal sampling

7. In the following discussion, we will be using the 3G SDI example to ease the discussion

8. In the Spf_sample_design_ttk.spf, set the sw[3..0] to select the 3Ga 1080p60 video pattern. The

video pattern generator will start to generate this pattern to the SDI RX

9. The SDI RX will perform auto rate change and lock to the incoming video pattern. After

successfully link up, you should now observe the rx_frame_locked and rx_trs_locked status

signals assert as shown in Figure 6

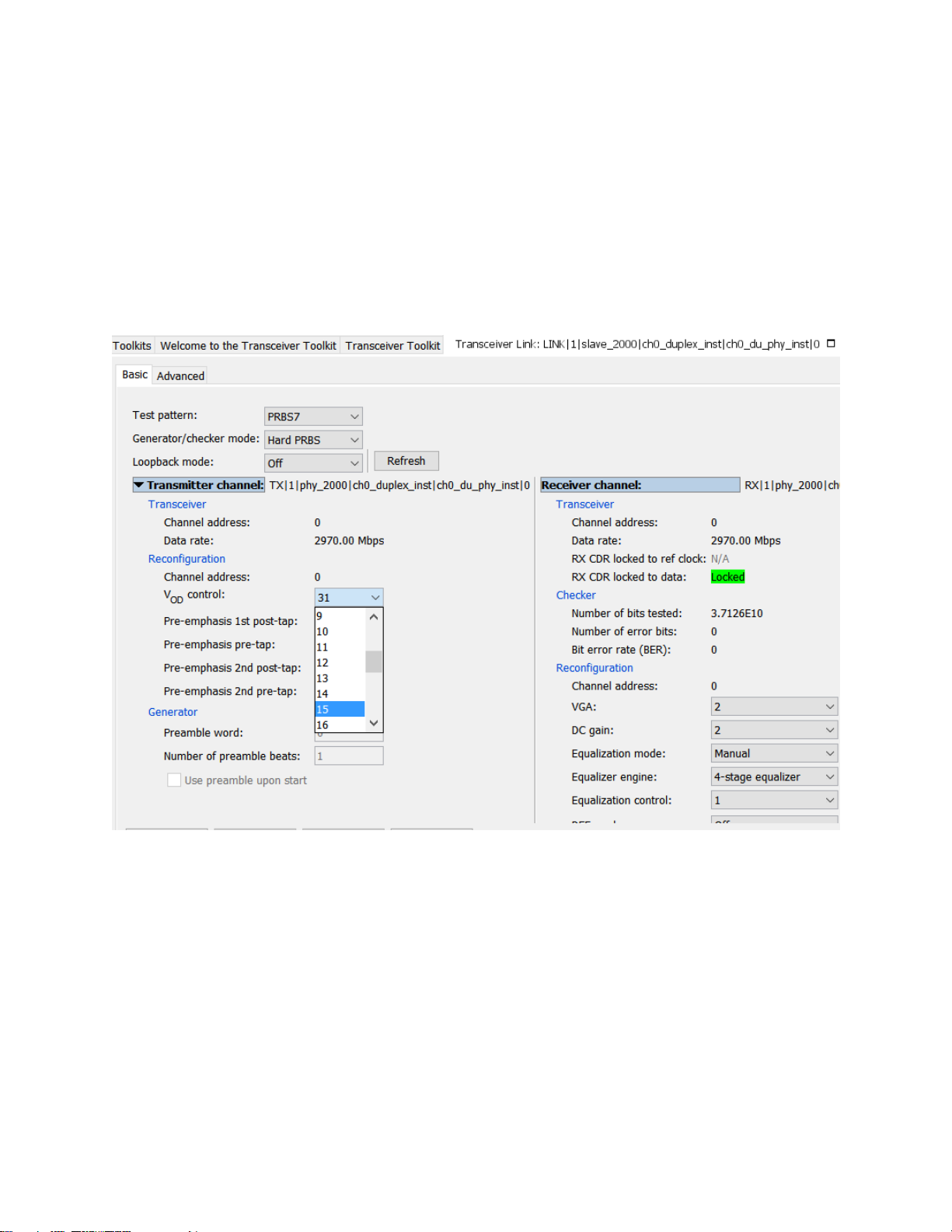

10. To perform the transceiver PMA analog settings tuning, open the transceiver toolkit at Quartus -

> Tools -> System Debugging Tools -> Transceiver Toolkit

11. Load the design SOF file in the transceiver toolkit to establish link with the transceiver at

Transceiver Toolkit -> File -> Load Design as shown in Figure 7

12. Click on the Transceiver Toolkit -> Transceiver Links -> Control Transceiver Link to establish

control over the TX and RX as shown in Figure 8

13. After the transceiver link control established, you can click on the drop-down list of the TX and

RX PMA analog settings to dynamically change the values. For example, you can change the TX

VOD settings as shown in Figure 9.

14. By using the transceiver toolkit GUI, you can dynamically change the PMA settings to fine tune

the signal integrity of the SDI link. This would be the manual way of tuning

15. Transceiver toolkit also supports the Auto-sweep feature to help finding optimal PMA analog

settings for your link

16. During the Auto-sweep process, the transceiver toolkit will be sending PRBS data pattern

through the transceiver TX. Due to the PRBS pattern, the SDI RX will lose lock and keep changing

its rate in attempt to lock to the incoming data

17. Before running Auto-sweep with Transceiver Toolkit, send a 3G TX video pattern to the RX so

that the RX is reconfigured to 3G mode

18. To allow transceiver toolkit to take full control of the transceiver and avoid the RX being reset

and reconfigured by SDI II IP, go to the Spf_sample_design_ttk.spf, set the reconfig_rst signal to

High as shown in Figure 10

19. Go to Advanced -> Auto-sweep. Set the PMA analog settings to a specific range then click Start

to start the Auto-sweep. Figure 11 shows an example of sweeping VOD values from 0 to 30

20. As the Auto-sweep run, the transceiver toolkit will record the best value found for the PMA

settings as shown in the Figure 12

21. You may then port these optimal values to your design through Assignment Editor or QSF