- 3 -

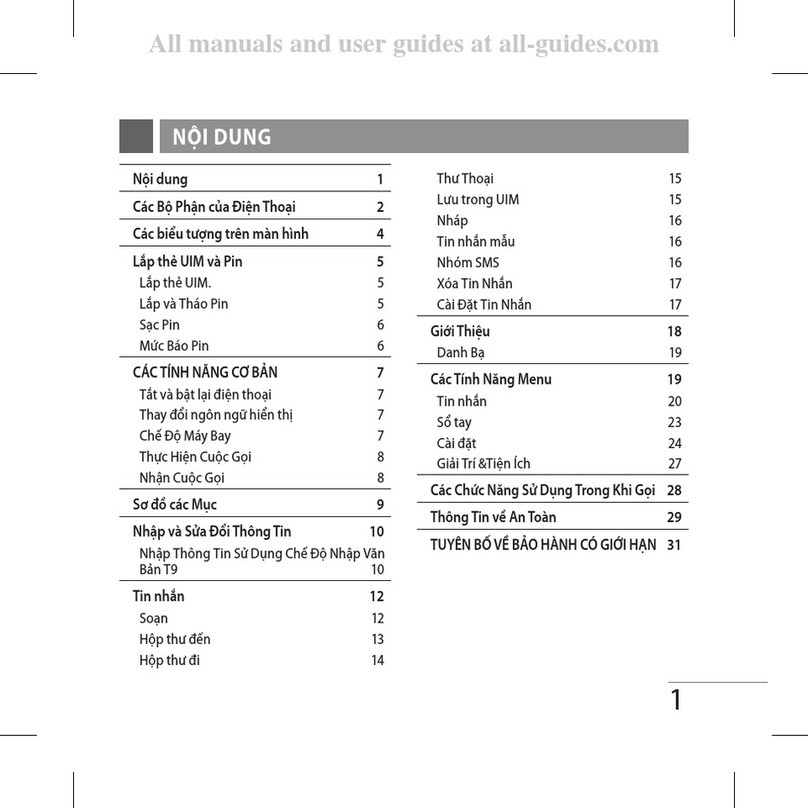

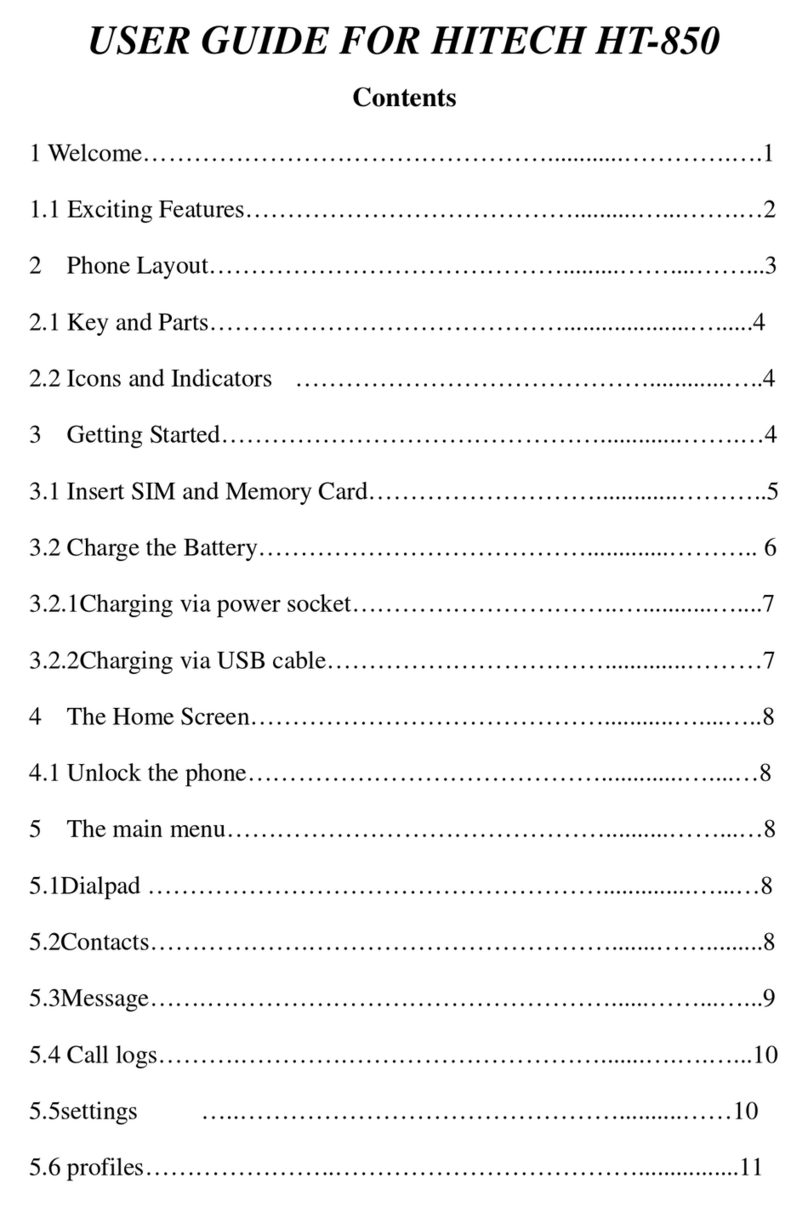

1. INTRODUCTION.................................... 5

1.1 Purpose ................................................. 5

1.2 Regulatory Information .......................... 5

A. Security ............................................. 5

B. Incidence of Harm ............................. 5

C. Changes in Service ........................... 5

D. Maintenance Limitations ................... 5

E. Notice of Radiated Emissions ............ 5

F. Pictures ............................................. 6

G. Interference and Attenuation ............ 6

H. Electrostatic Sensitive Devices ......... 6

1.3 Abbreviations ......................................... 6

2. PERFORMANCE .................................. 8

2.1 H/W Feature .......................................... 8

2.2 Technical Specification .......................... 9

3. TECHNICAL BRIEF ........................... 13

3.1 Transceiver (SI4205-BM, U402) .......... 13

3.2 Power Amplifier Module

(RF3133, U401) .................................... 17

3.3 13 MHz Clock ...................................... 18

3.4 Power Supplies for RF Circuits ............ 18

3.5 Digital Main Processor

(AD6525, U101) ................................... 19

3.6 Analog Main Processor (AD6521, U102)

.............................................................. 23

3.7 Power Management IC

(ADP3522, U202) ................................ 26

3.8 Memory (U201) .................................... 28

3.9 LCD and LCD Backlight ....................... 30

3.10 Keypad Switches and Key Backlight

Illumination ......................................... 33

3.11 Microphone ........................................ 29

3.12 Dual Mode Speaker and MIDI IC ....... 34

3.13 Headset Jack Interface ...................... 36

3.14 Compass ............................................ 37

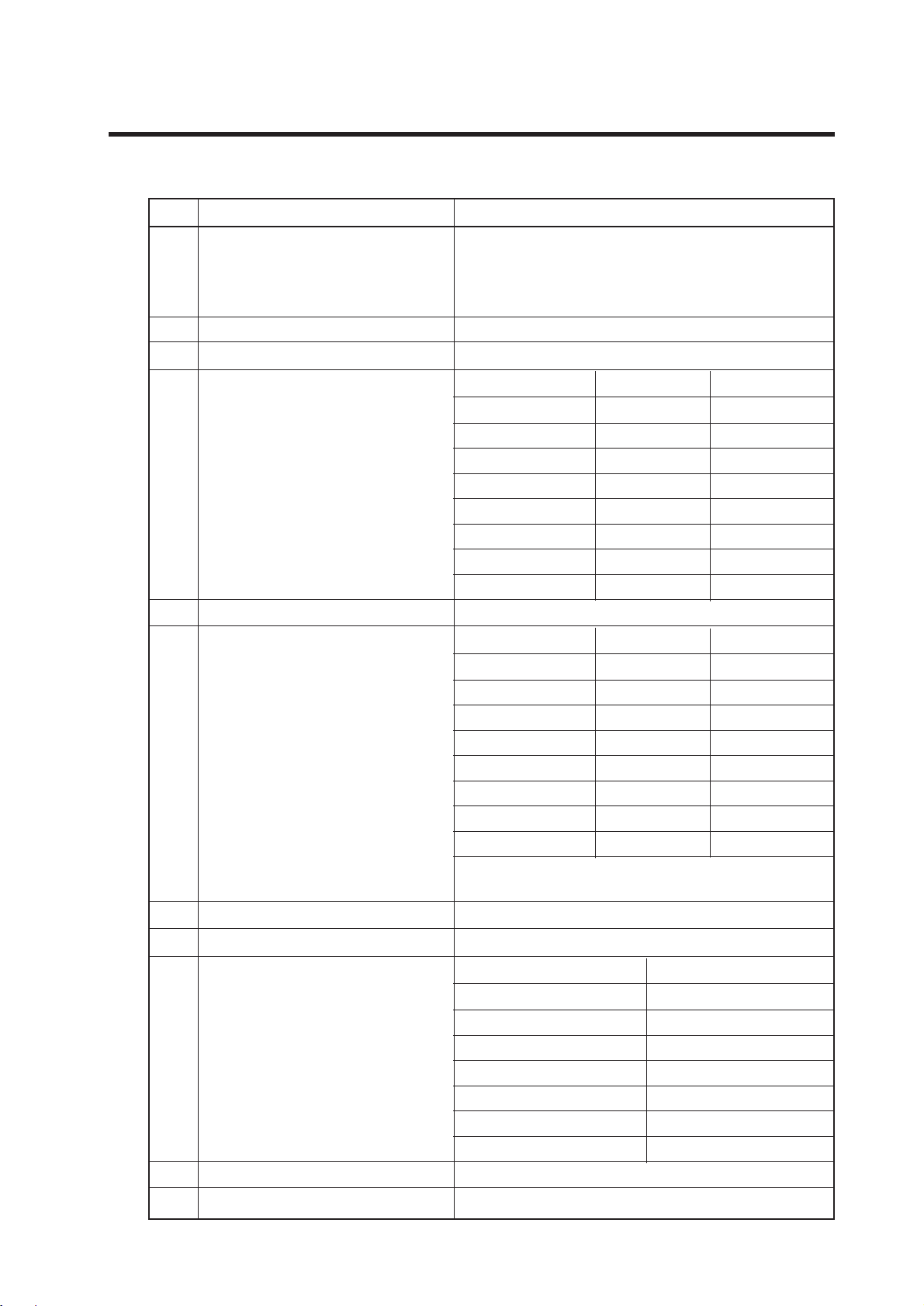

4. TROUBLE SHOOTING ..................... 38

4.1 RF Components ................................... 38

4.2 RX Trouble ........................................... 39

4.2.1 Checking Regulator Circuit ......... 40

4.2.2 Checking VCTCXO Circuit ......... 41

4.2.3 Checking Transceiver

Control Signal ............................. 42

4.2.4 Checking Antenna Switch &

Mobile Switch ............................. 43

4.2.5 Checking SAW Filter .................. 44

4.2.6 Checking RX IQ .......................... 45

4.3 TX Trouble ........................................... 46

4.3.1 Checking Regulator Circuit ......... 47

4.3.2 Checking VCTCXO Circuit ......... 48

4.3.3 Checking PLL Control Signal ...... 49

4.3.4 Checking TX IQ .......................... 50

4.3.5 Checking PAM Control Signal .....51

4.3.6 Checking Antenna Switch &

Mobile Switch ............................. 52

4.3.7 Checking Antenna Contact ......... 54

4.4 Power On Trouble ................................ 55

4.5 Charging Trouble ................................. 57

4.6 LCD Trouble ........................................ 59

4.7 Receiver Trouble ................................. 61

4.8 Speaker Trouble .................................. 63

4.9 MIC Trouble ......................................... 65

4.10 Vibrator Trouble ................................. 66

4.11 Key Backlight LED Trouble ................ 68

4.12 SIM Detect Trouble ............................ 69

4.13 Ear Jack Trouble ................................ 70

4.14 Compass Trouble .............................. 73

5. DISASSEMBLY INSTRUCTION ..... 76

5.1 Disassembly ........................................ 76

6. DOWNLOAD AND CALIBRATION

.................................................................... 80

6.1 Download ............................................. 80

A. Download Setup .............................. 80

B. Download Procedure ....................... 81

6.2 Calibration ............................................ 87

A. Equipment List ................................ 87

B. Equipment Setup ............................. 87

C. Test Jig Operation ........................... 88

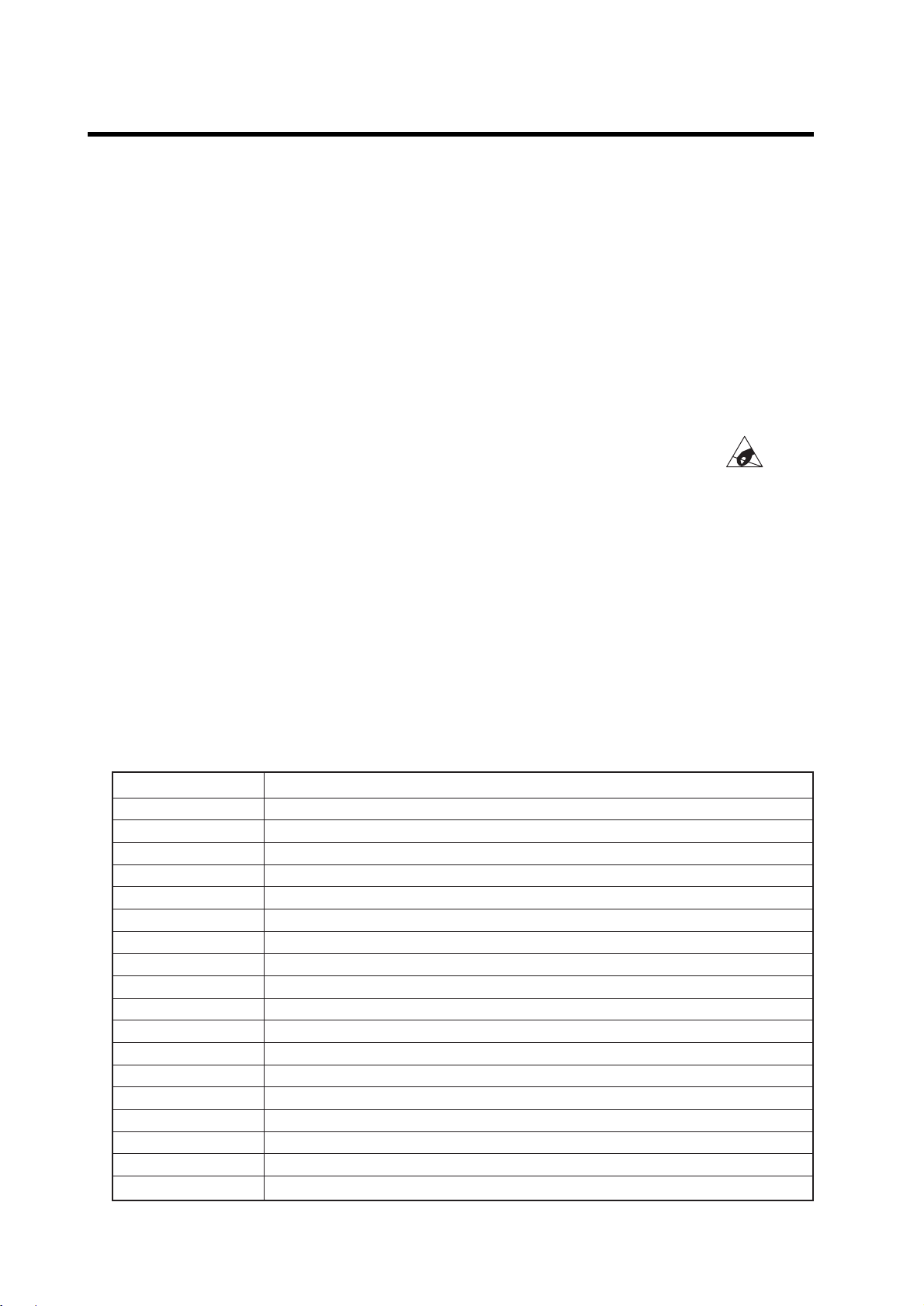

Table Of Contents