- 5 - LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

ADJUSTMENT INSTRUCTION

1. Application Range

This spec. sheet applies to PB23A chassis applied PDP TV all

models manufactured in TV factory.

2. Specification

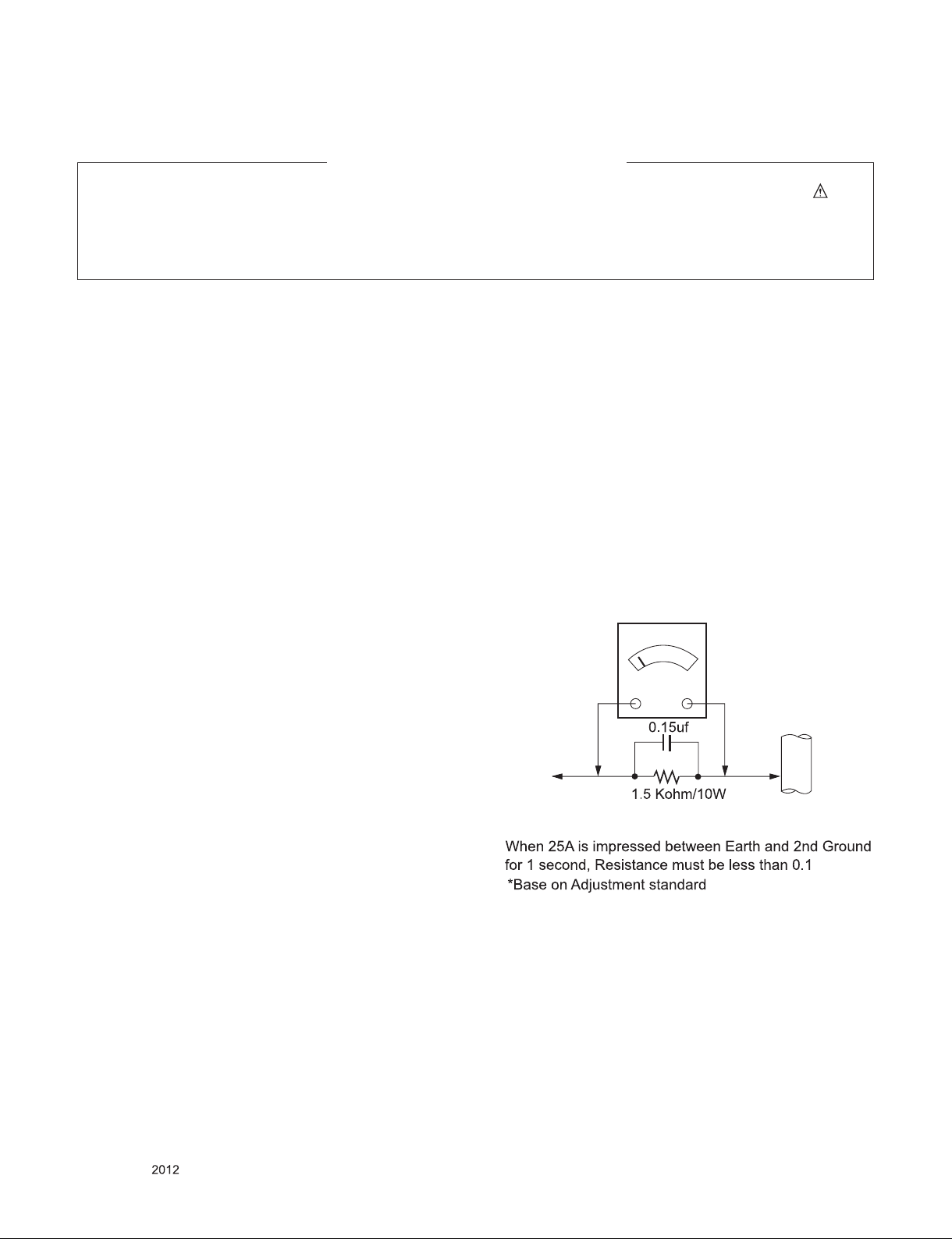

(1) Because this is not a hot chassis, it is not necessary to

use an isolation transformer. However, the use of isolation

transformer will help protect test instrument.

(2) Adjustment must be done in the correct order. But it is

flexible when its factory local problem occurs.

(3) The adjustment must be performed in the circumstance of

25 °C ± 5 °C of temperature and 65 % ± 10 % of relative

humidity if there is no specific designation.

(4) The input voltage of the receiver must keep AC 100-240

V~, 50/60 Hz.

(5) Before adjustment, execute Heat-Run for 5 minutes.

■ After Receive 100% Full white pattern (06CH) then

process Heat-run

(or “8. Test pattern” condition of Ez-Adjust status)

■How to make set white pattern

1) Press Power ON button of Service Remocon

2) Press ADJ button of Service remocon. Select “10. Test

pattern” and, after select “White” using navigation

button, and then you can see 100% Full White pattern.

* In this status you can maintain Heat-Run useless any

pattern generator

* Notice: if you maintain one picture over 20 minutes

(Especially sharp distinction black with white

pattern – 13Ch, or Cross hatch pattern – 09Ch)

then it can appear image stick near black level.

3. Adjustment items

3.1. PCB Assembly adjustment

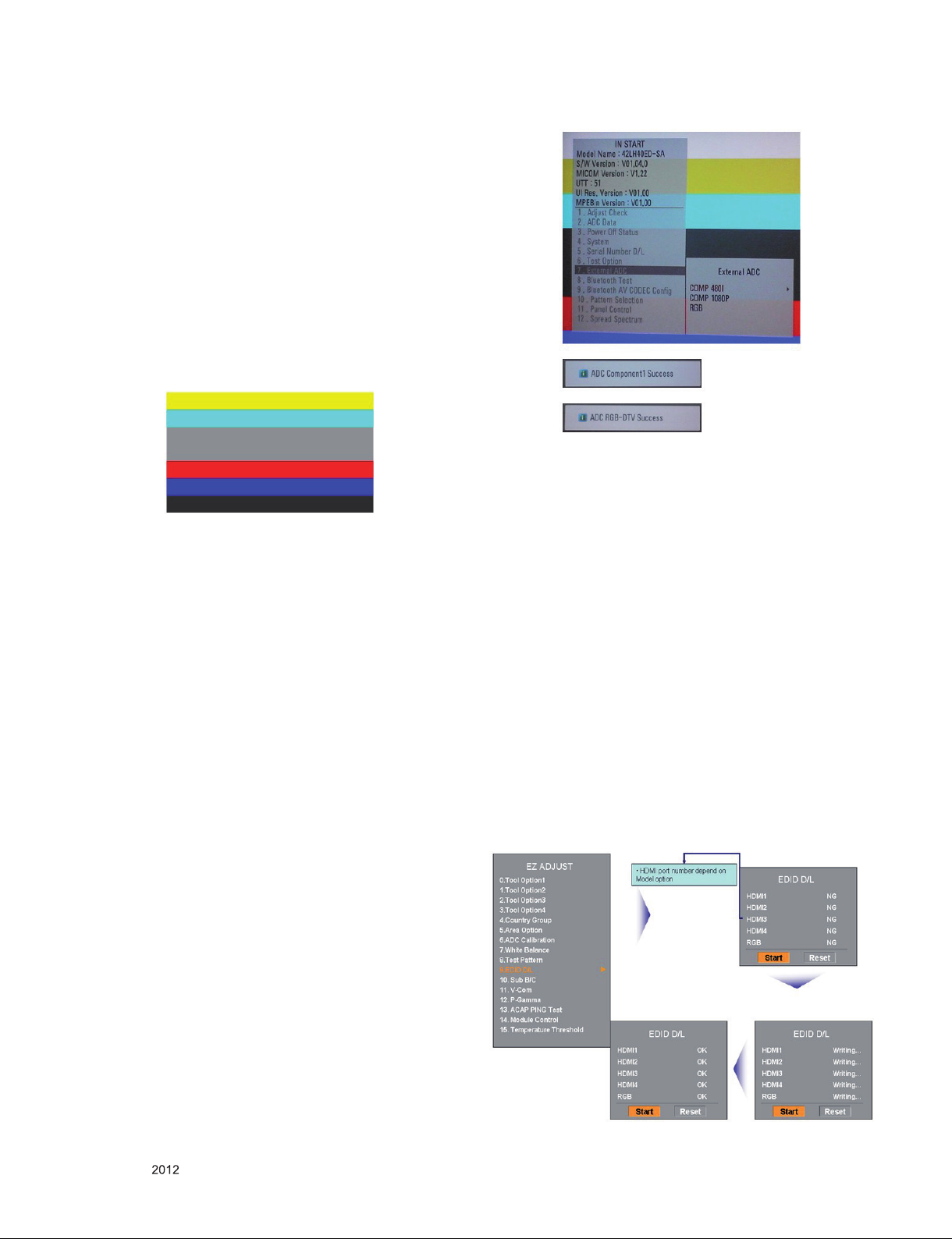

■Adjust 480i Comp1

■Adjust 1080p Comp1/RGB

●If it is necessary, it can adjustment at Manufacture Line

●You can see set adjustment status at “9. ADJUST

CHECK” of the “In-start menu”

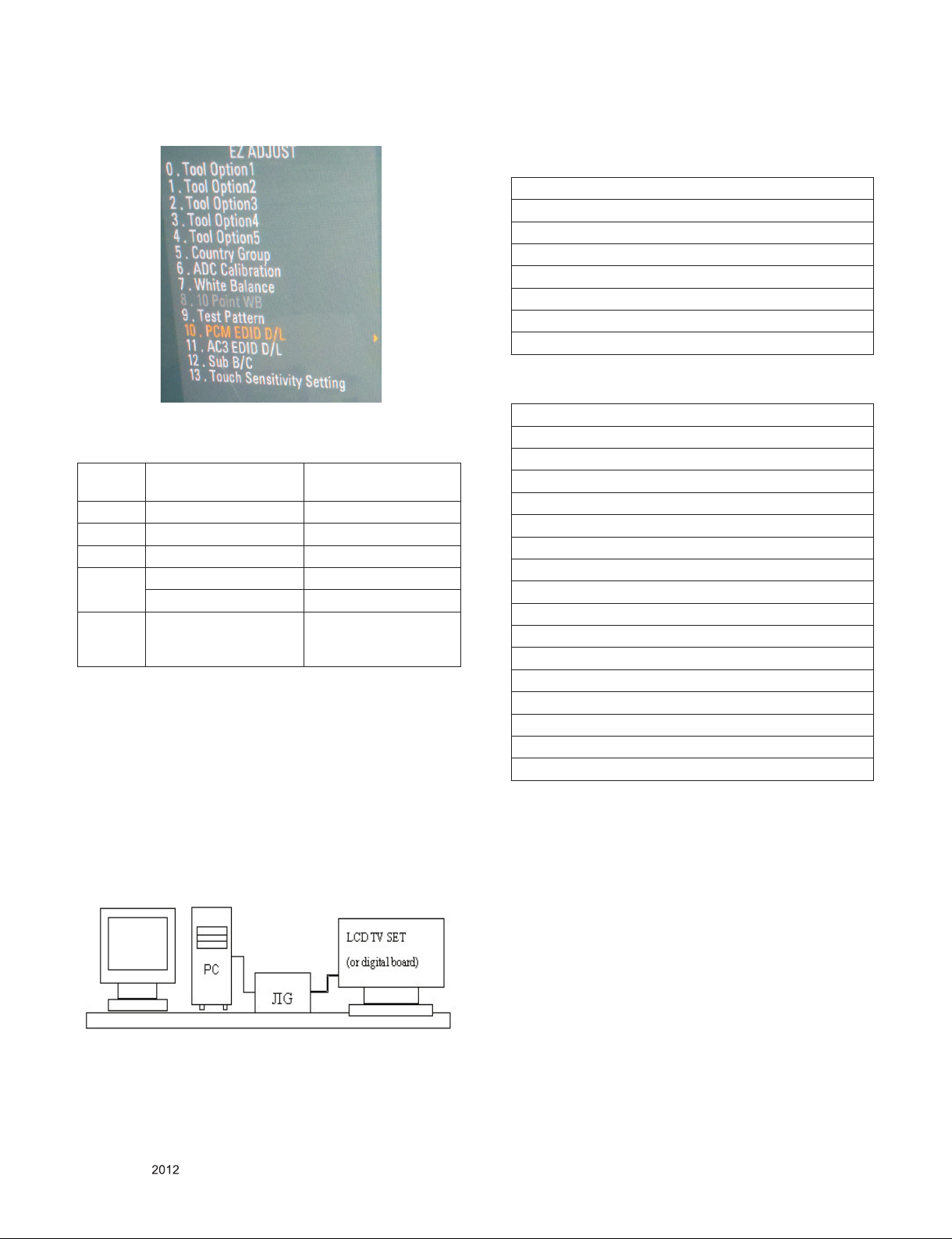

3.2. Set Assembly Adjustment

■EDID (The Extended Display Identification Data )

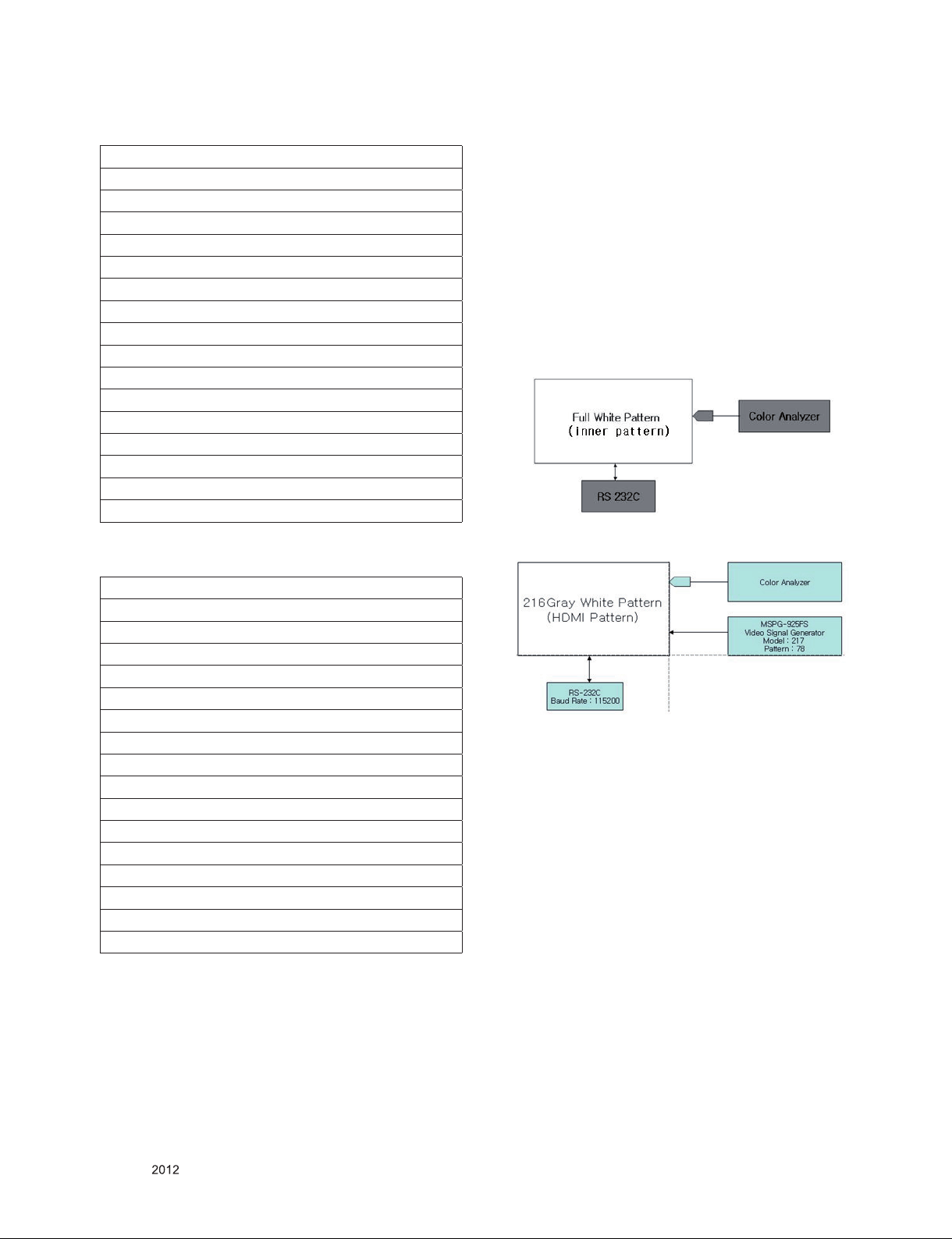

■Color Temperature (White Balance) Adjustment

■Make sure RS-232C control

■Selection Factory output option

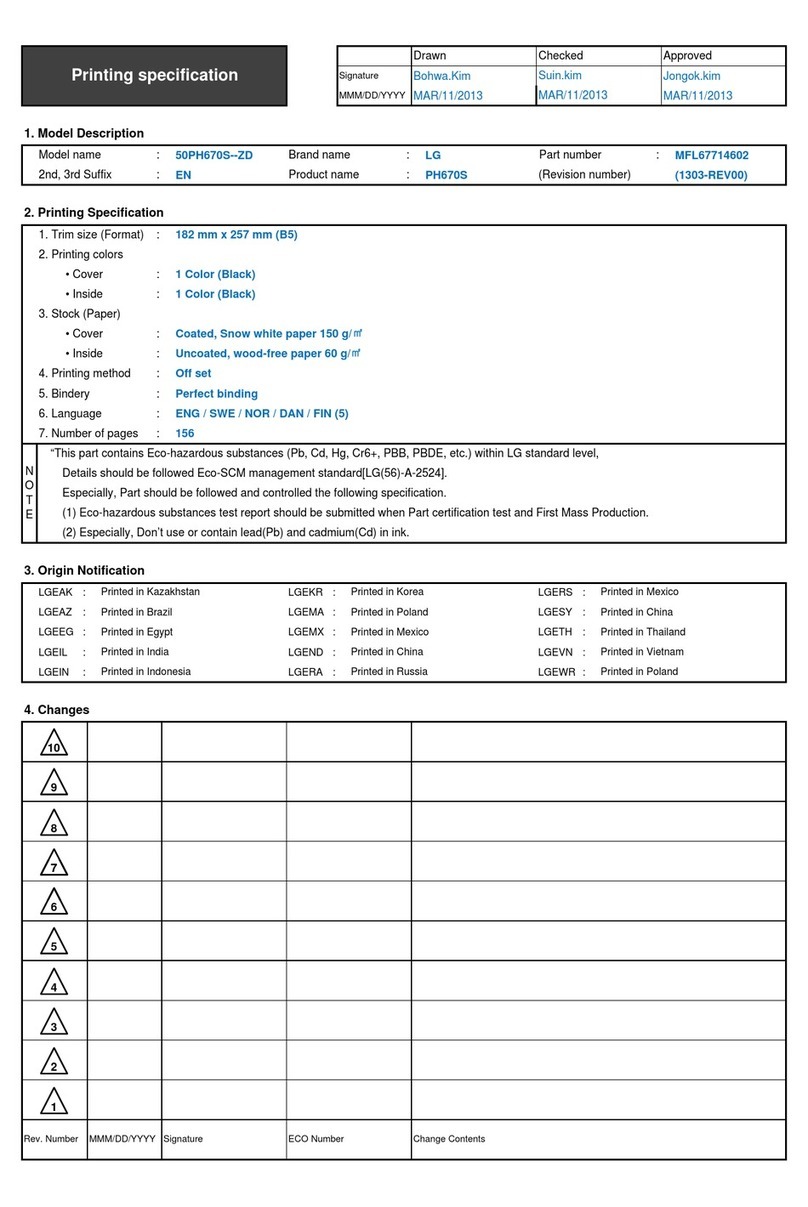

4. PCB Assembly Adjustment

4.1. Using RS-232C

- Adjust 3 items at 3.1. PCB assembly adjustments

" 4.1. ■Adjustment sequence" one after the order.

■Adjustment sequence

■Necessary items before Adjustment items

●Pattern Generator : (MSPG-925FA)

●Adjust 480i comp1

(MSPG-925FA:model :209, pattern :65) - comp1 Mode

●Adjust 1080p comp1

(MSPG-925FA:model :225 , pattern :65) - comp1 Mode

●Addjust RGB (MSPG-925FA:model :225 , pattern :65)

- RGB-Pc Mode

* If you want more information then see the below Adjustment

method (Factory Adjustment)

■Adjustment sequence

●aa 00 00: Enter the ADc Adjustment mode.

●xb 00 40: change the mode to component1 (No actions)

●ad 00 10: Adjust 480i comp

●ad 00 10: Adjust 1080p comp

●xb 00 60: change to RGB-Pc mode(No action)

●ad 00 10: Adjust 1080p RGB

●xb 00 90: Endo of Adjustmennt

< See ADC Adjustment RS232C Protocol_Ver1.0 >

Order command Set response

1. Inter the

Adjustment

mode

aa 00 00 a 00 OK00x

2. Change the

Source

XB 00 40

XB 00 60

b 00 OK40x (Adjust 480i Comp1 )

(Adjust 1080p Comp1)

b 00 OK60x (Adjust 1080p RGB)

3. Start

Adjustment

ad 00 10

4. Return the

Response

OKx ( Success condition )

NGx ( Failed condition )

5. Read

Adjustment

data

( main )

ad 00 20

( main )

ad 00 30

(main : component1 480i, RGB 1080p)

000000000000000000000000007c007b006dx

(main : component1 1080p)

000000070000000000000000007c00830077x

6. Conrm

Adjustment

ad 00 99 NG 03 00x (Failed condition)

NG 03 01x (Failed condition)

NG 03 02x (Failed condition)

OK 03 03x (Success condition)

7. End of

Adjustment

ad 00 90 d 00 OK90x