8. White Bala ce adj.

8-1. Overview

(1) W/B adj.: Objective & How-it-works

1) Objective: To reduce each Panel’s W/B deviation

2) How-it-works: When R/G/B gain in the OSD is at 192, it

means the panel is at its Full Dynamic

Range. In order to prevent saturation o

Full Dynamic range and data, one o

R/G/B is ixed at 192, and the other two is

lowered to ind the desired value.

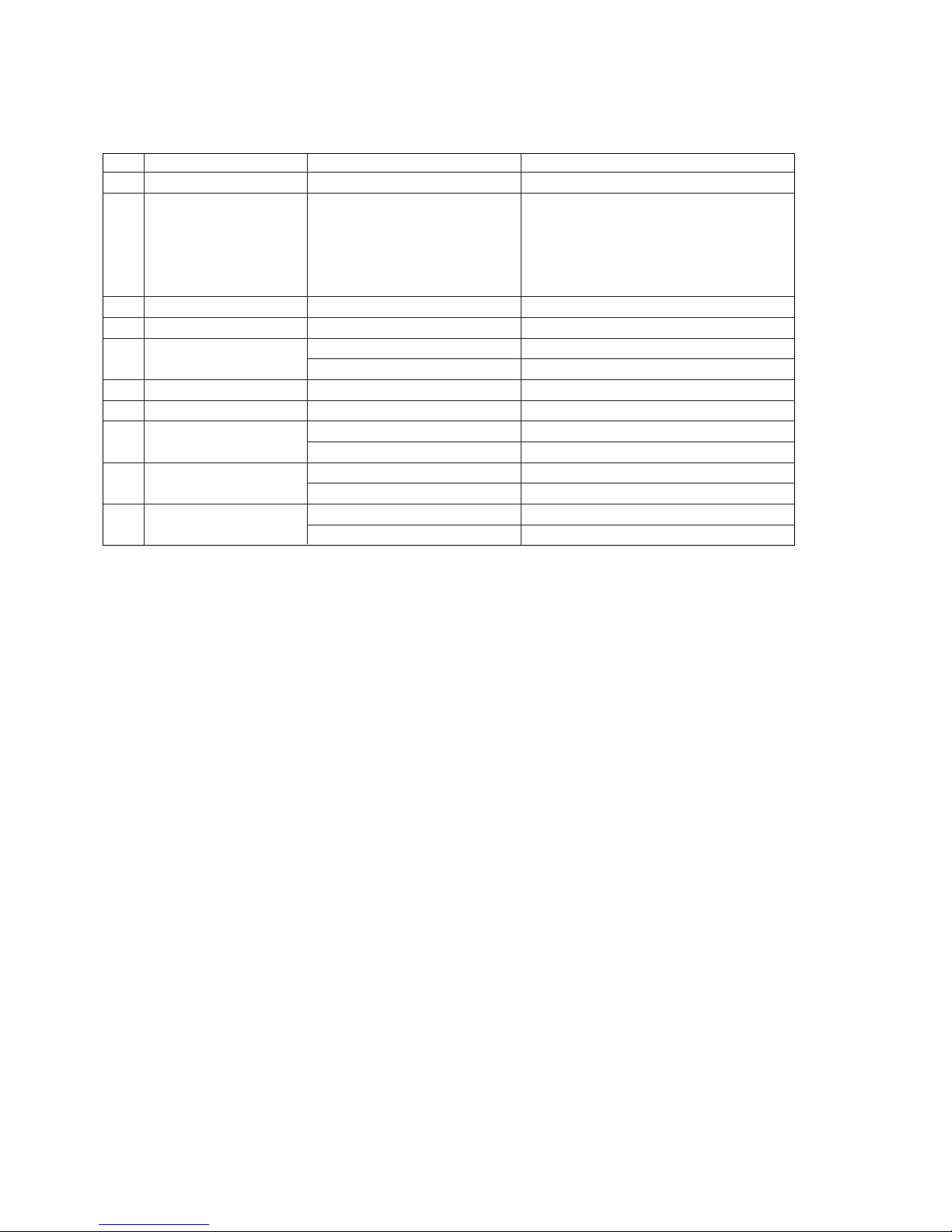

8-2. Equipme t

(1) Color Analyzer : CA-210 (NCG: CH 9 / WCG: CH12 /PDP

Module:CH10)

(2) Adj. Computer

(During auto adj., RS-232C protocol is needed)

(3) Adj. R/C

(4) Video Signal Generator MSPG-925F 720p/216Gray

(Model:217, Pattern:78)

-> Only when internal pattern is not available

- Color Analyzer Matrix should be calibrated using CS-1000

8-3. Equipme t co ectio map

8-4. Adj. Comma d (Protocol)

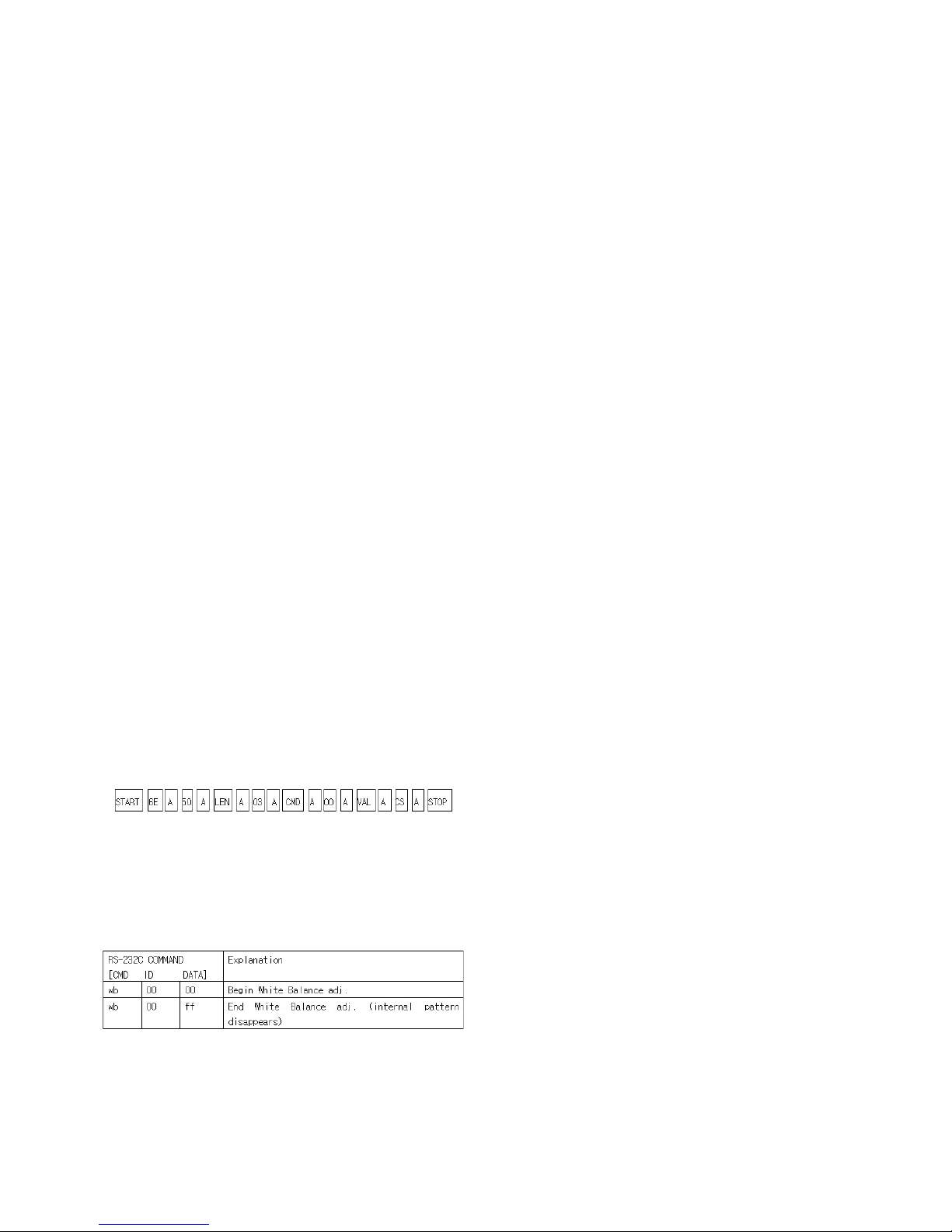

OProtocol

<Command Format>

- LEN: Number o Data Byte to be send

- CMD: Command

- VAL: FOS Data

- CS: Checksum o sent Data

- A: Acknowledge

Ex) [Send: JA_00_DD] / [Ack: A_00_okDDX]

ORS-232C Command used during auto-adj.

Ex) wb 00 00 -> Begin white balance auto-adj.

wb 00 10 -> Gain adj.

ja 00 -> Adj. data

jb 00 c0

...

...

wb 00 1 -> Gain adj. complete

*(wb 00 20(Start), wb 00 2 (End)) -> O -set adj.

wb 00 -> End white balance auto-adj.

8-5. Auto Adj. method

(1) Set TV in adj. mode using POWER On Key

(2) Zero calibrate probe then place it on the center o the

Display

(3) Connect Cable(RS-232C)

(4) Select mode in adj. Program and begin adj.

(5) When adj. is complete (OK Sign), check adj. status per

mode

(Warm, Medium, Cool)

(6) Remove probe and RS-232C cable to complete adj.

- Adj. must begin w/ command “wb 00 00”, and end “wb 00

” and adj. o set i needed.

- O set adjust limit value.

O set Min = 34 (Decimal)

O set Max = 94 (Decimal)

8-6. Ma ual adj. method

Dynamic contrast : o

Dynamic color : o

OPC : O

Energy saving mode : O

(1) Set TV Picture Mode to Standard and in Advanced

Control, set Dynamic Contrast and Color ‘ O ’ .

(2) Set TV in adj. mode using POWER On Key

(3) Press ADJ key -> EZ adjust using adj. R/C

(4) Using CH + / - KEY, select 10.TEST PATTERN then press

Enter to place in HEAT RUN mode and wait or 30

minutes.

(4) Zero calibrate the probe o Color Analyzer, then place it on

the center o LCD module within 10 cm o the sur ace.

(5) Press ADJ key -> 7. White-Balance then press the cursor

to the right (KEY G)

(When Gis pressed Full White internal pattern will be

displayed)

(6) One o R Gain / G Gain / B Gain should be ixed at 192,

and the rest will be lowered to meet the desired value.

(7) Adj. is per ormed in COOL, MEDIUM, WARM 3 modes o

color temperature

(8) O set Adjust in MEDIUM, WARM 2 modes o color

temperature ( Only THX Model )

V I internal pattern is not available, use HDMI input. In EZ

Adj. menu 7.White Balance, you can select one o 3

options: None, Inner, HDMI. De ault is inner. By selecting

HDMI, you can adjust using HDMI signal.

- 9 - LGE Internal Use OnlyCopyright ©2011 LG Electronics Inc. All rights reserved.

Only or training and service purposes