General Description

The MAX12557 is a dual 3.3V, 14-bit analog-to-digital

converter (ADC) featuring fully differential wideband

track-and-hold (T/H) inputs, driving internal quantizers.

The MAX12557 is optimized for low power, small size,

and high dynamic performance in intermediate frequen-

cy (IF) and baseband sampling applications. This dual

ADC operates from a single 3.3V supply, consuming

only 610mW while delivering a typical 72.5dB signal-to-

noise ratio (SNR) performance at a 175MHz input fre-

quency. The T/H input stages accept single-ended or

differential inputs up to 400MHz. In addition to low oper-

ating power, the MAX12557 features a 166µW power-

down mode to conserve power during idle periods.

A flexible reference structure allows the MAX12557 to

use the internal 2.048V bandgap reference or accept

an externally applied reference and allows the refer-

ence to be shared between the two ADCs. The refer-

ence structure allows the full-scale analog input range

to be adjusted from ±0.35V to ±1.15V. The MAX12557

provides a common-mode reference to simplify design

and reduce external component count in differential

analog input circuits.

The MAX12557 supports either a single-ended or differ-

ential input clock. User-selectable divide-by-two (DIV2)

and divide-by-four (DIV4) modes allow for design flexibil-

ity and help eliminate the negative effects of clock jitter.

Wide variations in the clock duty cycle are compensated

with the ADC’s internal duty-cycle equalizer (DCE).

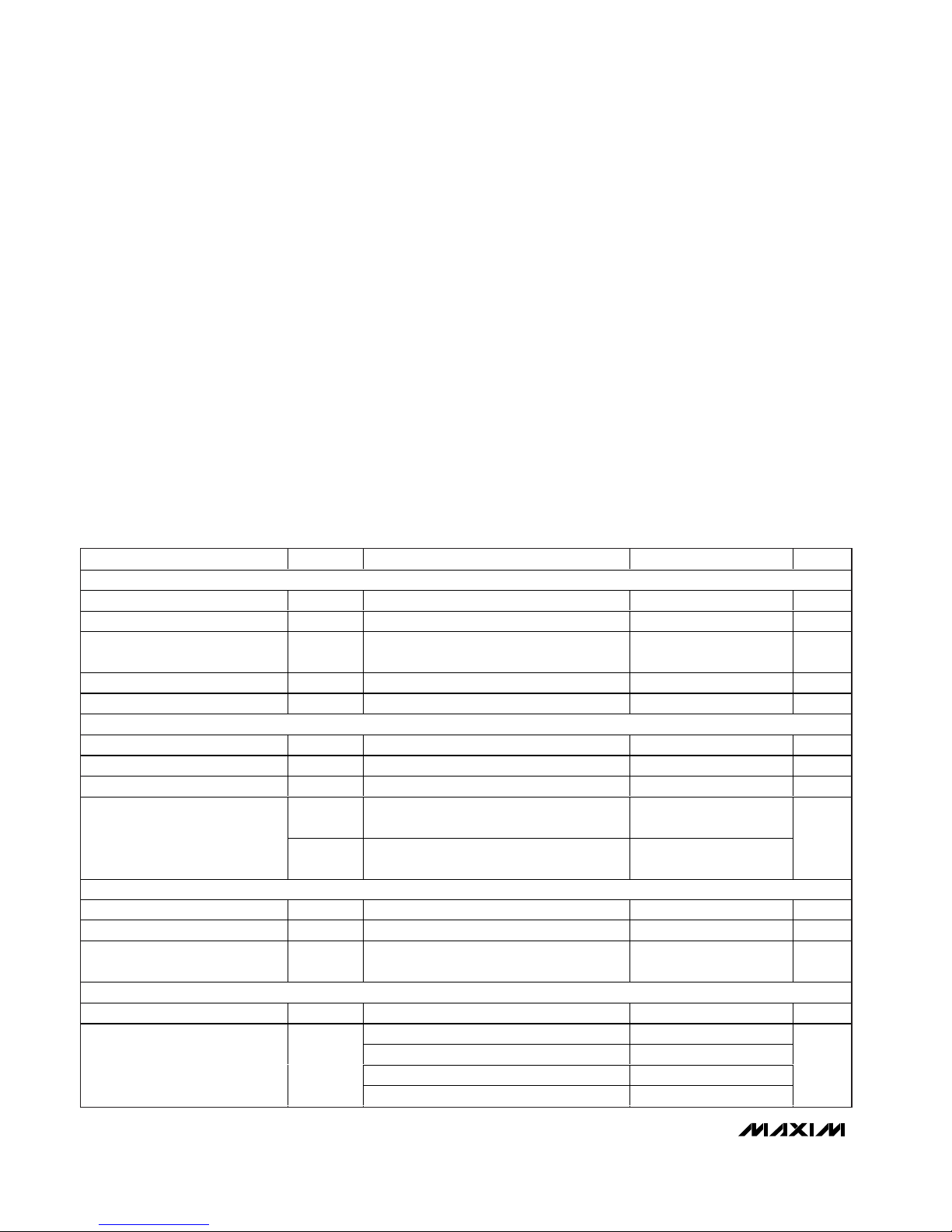

The MAX12557 features two parallel, 14-bit-wide,

CMOS-compatible outputs. The digital output format is

pin-selectable to be either two’s complement or Gray

code. A separate power-supply input for the digital out-

puts accepts a 1.7V to 3.6V voltage for flexible interfac-

ing with various logic levels. The MAX12557 is available

in a 10mm x 10mm x 0.8mm, 68-pin thin QFN package

with exposed paddle (EP), and is specified for the

extended (-40°C to +85°C) temperature range.

For a 12-bit, pin-compatible version of this ADC, refer to

the MAX12527 data sheet.

Applications

IF and Baseband Communication Receivers

Cellular, LMDS, Point-to-Point Microwave,

MMDS, HFC, WLAN

I/Q Receivers

Ultrasound and Medical Imaging

Portable Instrumentation

Digital Set-Top Boxes

Low-Power Data Acquisition

Features

♦Direct IF Sampling Up to 400MHz

♦Excellent Dynamic Performance

74.1dB/72.5dB SNR at fIN = 70MHz/175MHz

83.4dBc/79.5dBc SFDR at fIN = 70MHz/175MHz

♦3.3V Low-Power Operation

637mW (Differential Clock Mode)

610mW (Single-Ended Clock Mode)

♦Fully Differential or Single-Ended Analog Input

♦Adjustable Differential Analog Input Voltage

♦750MHz Input Bandwidth

♦Adjustable, Internal or External, Shared Reference

♦Differential or Single-Ended Clock

♦Accepts 25% to 75% Clock Duty Cycle

♦User-Selectable DIV2 and DIV4 Clock Modes

♦Power-Down Mode

♦CMOS Outputs in Two’s Complement or Gray

Code

♦Out-of-Range and Data-Valid Indicators

♦Small, 68-Pin Thin QFN Package

♦12-Bit Compatible Version Available (MAX12527)

♦Evaluation Kit Available (Order MAX12557 EV Kit)

MAX12557

Dual, 65Msps, 14-Bit, IF/Baseband ADC

________________________________________________________________ Maxim Integrated Products 1

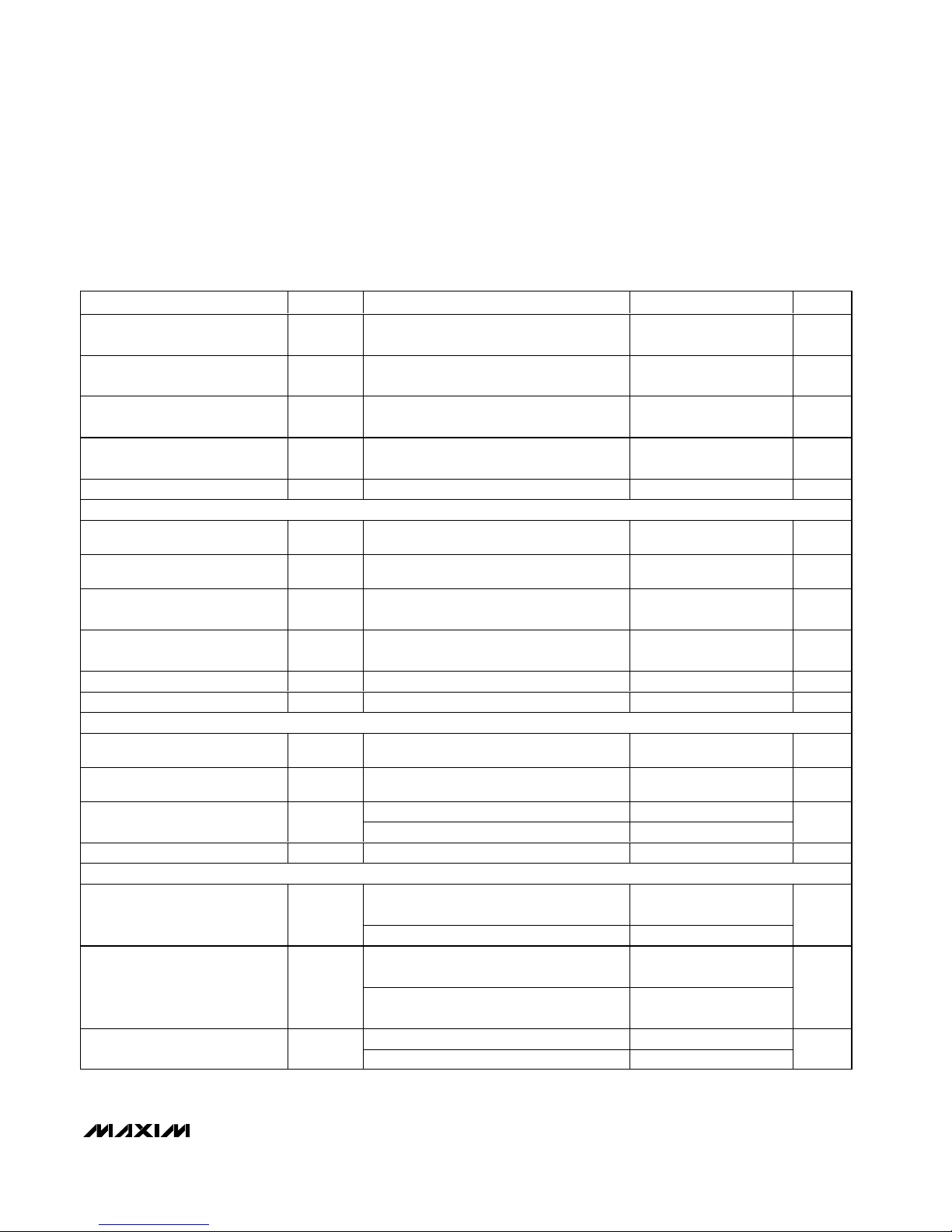

Ordering Information

19-3544; Rev 0; 2/05

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

EVALUATION KIT

AVAILABLE