1 Introduction

This application note describes the usage of the DC-DC Switching Mode

Power Supply (SMPS) converter for the MKW4xZ/3xZ/3xA/2xZ families. This

document covers operating voltages, types of circuit operation, hardware

design guidelines, software configuration, and power capabilities.

2 MKW DC-DC converter

This application note is based on the MKW41Z technical data. For other part numbers, see the part-specific documentation as

operating conditions, features, specifications, and requirements may vary. For example, some parts do not support boost mode

(MKW36, MKW35, MKW37, MKW38).

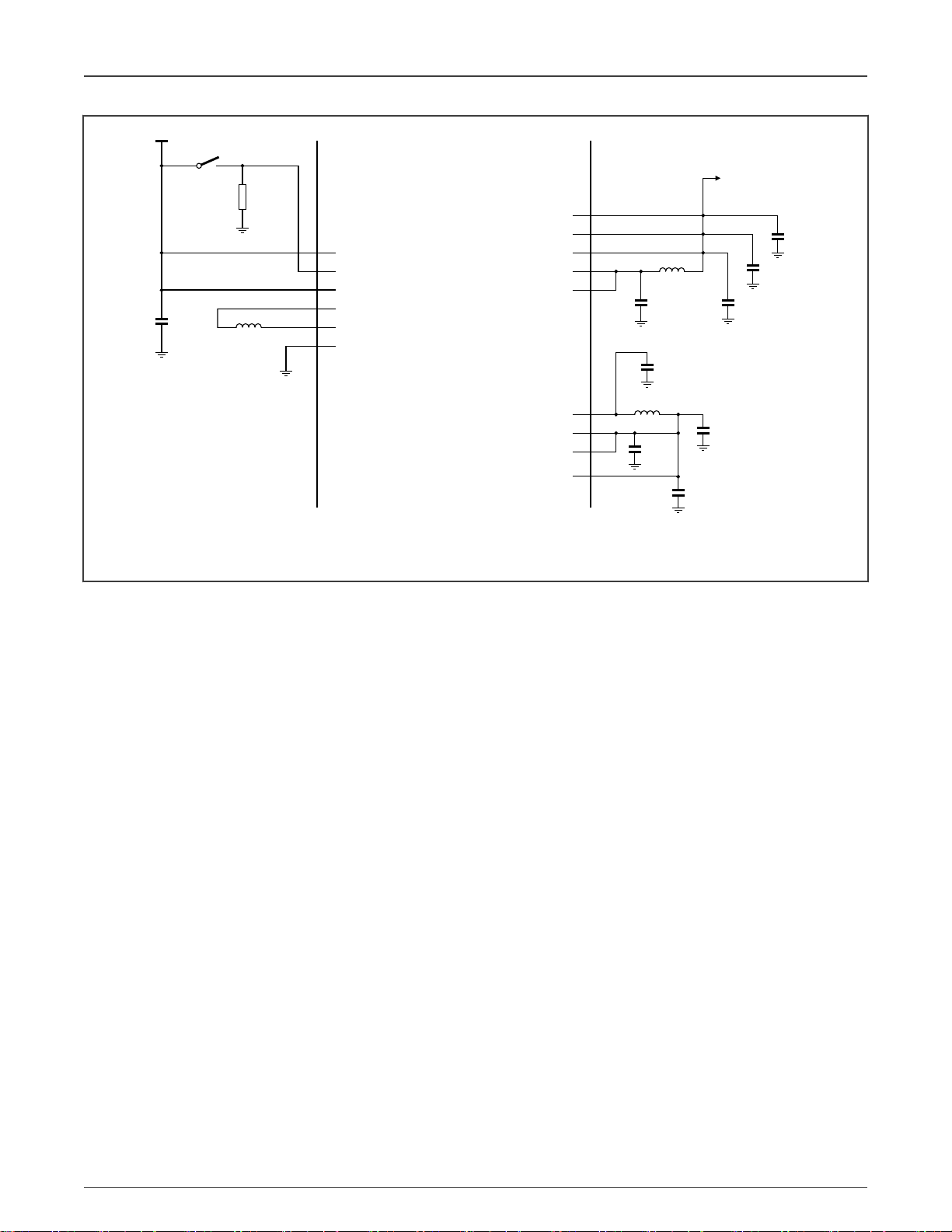

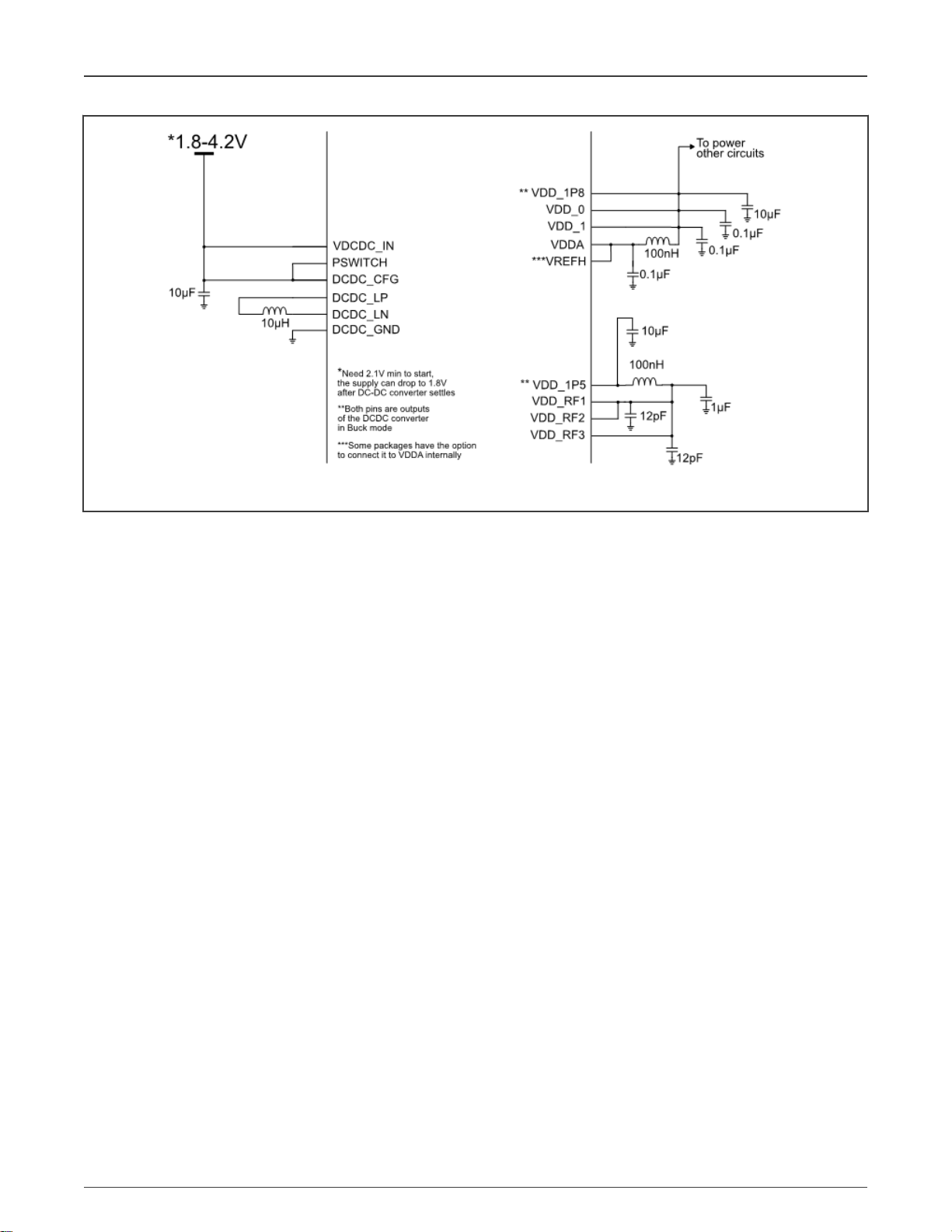

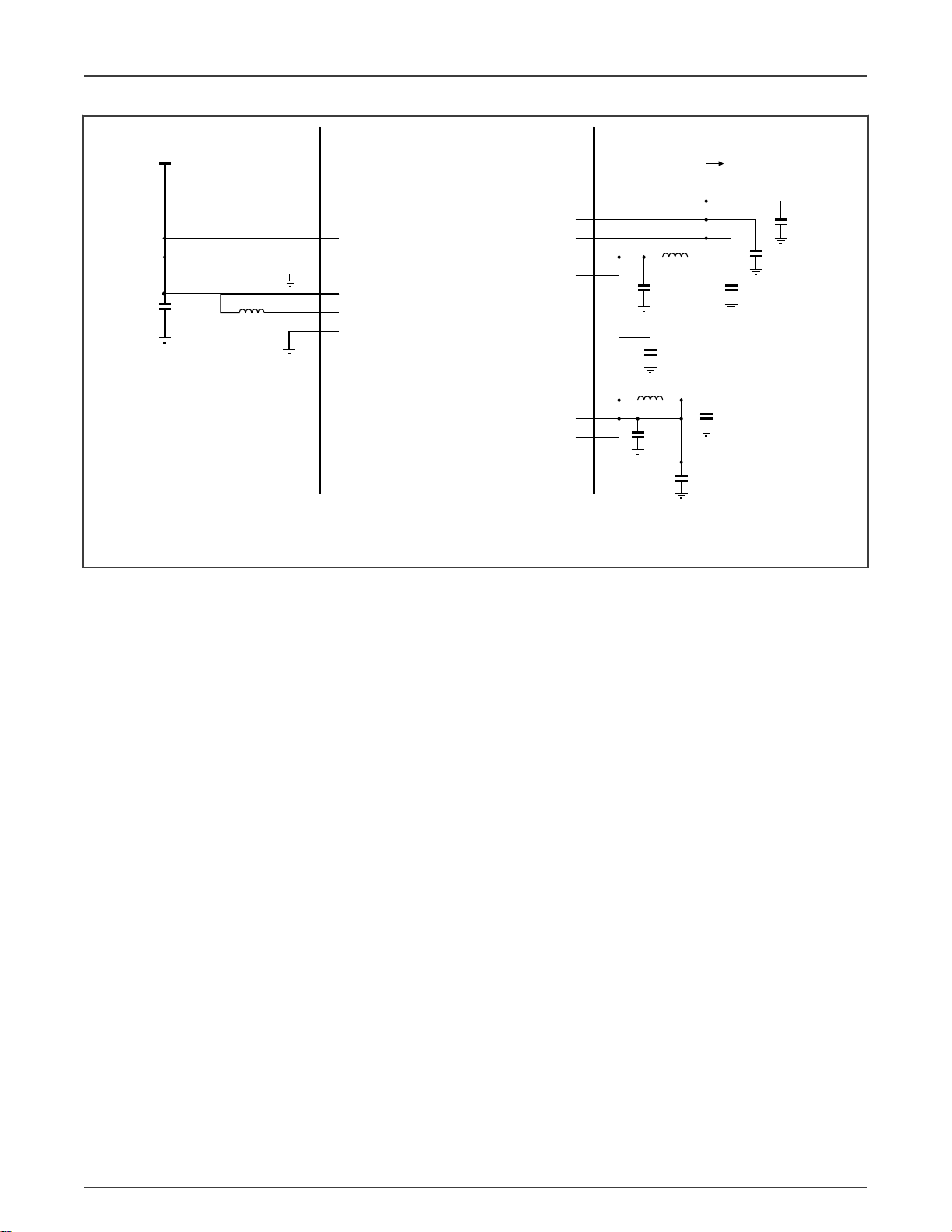

The DC-DC converter for MKW41Z is a dual output converter that supports three operating modes; Bypass, Buck, and Boost. In

Bypass mode, the DC-DC converter is disabled and the supply pins of the microcontroller must be supplied externally. In Buck

mode, the DC-DC converter is enabled and requires a DC supply in the range of 1.8 V to 4.2 V (during startup, the minimum supply

required is 2.1 V). In Boost mode, the DC-DC converter requires a DC supply in the range of 0.9 V to 1.795 V (during startup, the

minimum supply required is 1.1 V).

Startup and operating modes are configured with hardware selection through the DCDC_CFG and PSWITCH pins.

When the DC-DC converter is powered on, two outputs assume default voltage settings. By software, it is possible to change the

output voltages within the ranges shown in the table below, provided that, in Buck mode, for all input ranges the outputs are lower

than input voltage by 50 mV, or higher than input voltage by 50 mV when operating in Boost mode.

WARNING

VDD_1P8 must always be greater or equal to VDD_1P5. Otherwise, the internal protection diodes are forward biased, and may

cause electrical overstress, damaging the part.

Mode VDD1P8 VDD1P5

Default

Value

Range Default Value Range

Buck 1.8 V 1.71 V ≤ VDD_1P8 ≤ 3.50 V 1.5 V 1.425 V ≤ VDD_1P5 ≤ 1.65 V

Boost 1.8 V 1.71 V ≤ VDD_1P8 ≤ 3.50 V 1.8 V 1.425 V ≤ VDD_1P5 ≤ 2.0 V

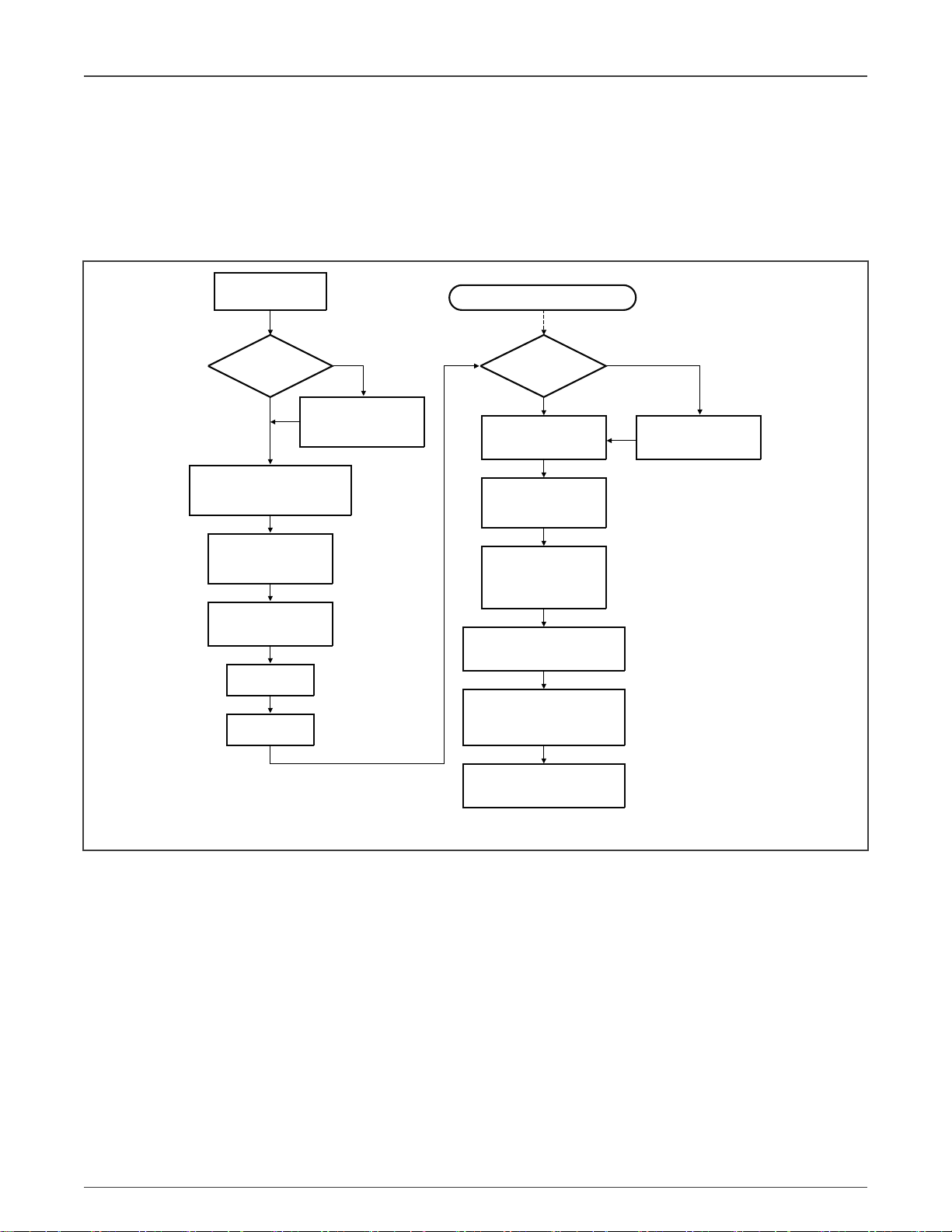

The DC-DC operates in two different modes; Continuous and Pulsed mode. When operating in continuous mode, the internal

digital controls are constantly on and the operating frequency is 1/16th of the DC-DC reference frequency. In most applications,

the RF oscillator (or main oscillator) is used as the DC-DC reference frequency and this is a 32 MHz clock. This results in a 2 MHz

operating frequency. Some applications may use a 26 MHz crystal. This would result in a 1.625 MHz operating frequency. The

DC-DC also has an internal RC oscillator that can be used as a reference when the RF oscillator is not being used. The frequency

of this oscillator is 26 MHz.

Contents

1 Introduction......................................1

2 MKW DC-DC converter...................1

3 DC-DC Power modes......................2

4 DC-DC converter software setup.... 6

5 Hardware design Guidelines......... 16

6 Current estimation and efficiency

report.............................................21

7 Revision history.............................27

AN5025

MKW4xZ/3xZ/3xA/2xZ DC-DC Power Management

Rev. 3 — 04 June 2021 Application Note