PEX 8624-AA RDK Hardware Reference Manual – Version 1.1

Copyright © 2010 by PLX Technology, Inc. All rights reserved ii

CONTENTS

NOTICE ......................................................................................................................................................... i

ABOUT THIS MANUAL .................................................................................................................................. i

REVISION HISTORY ...................................................................................................................................i

1.General Information.............................................................................................................................1

1.1PEX 8624 Features....................................................................................................................... 2

1.2PEX 8624-AA RDK Features...................................................................................................... 3

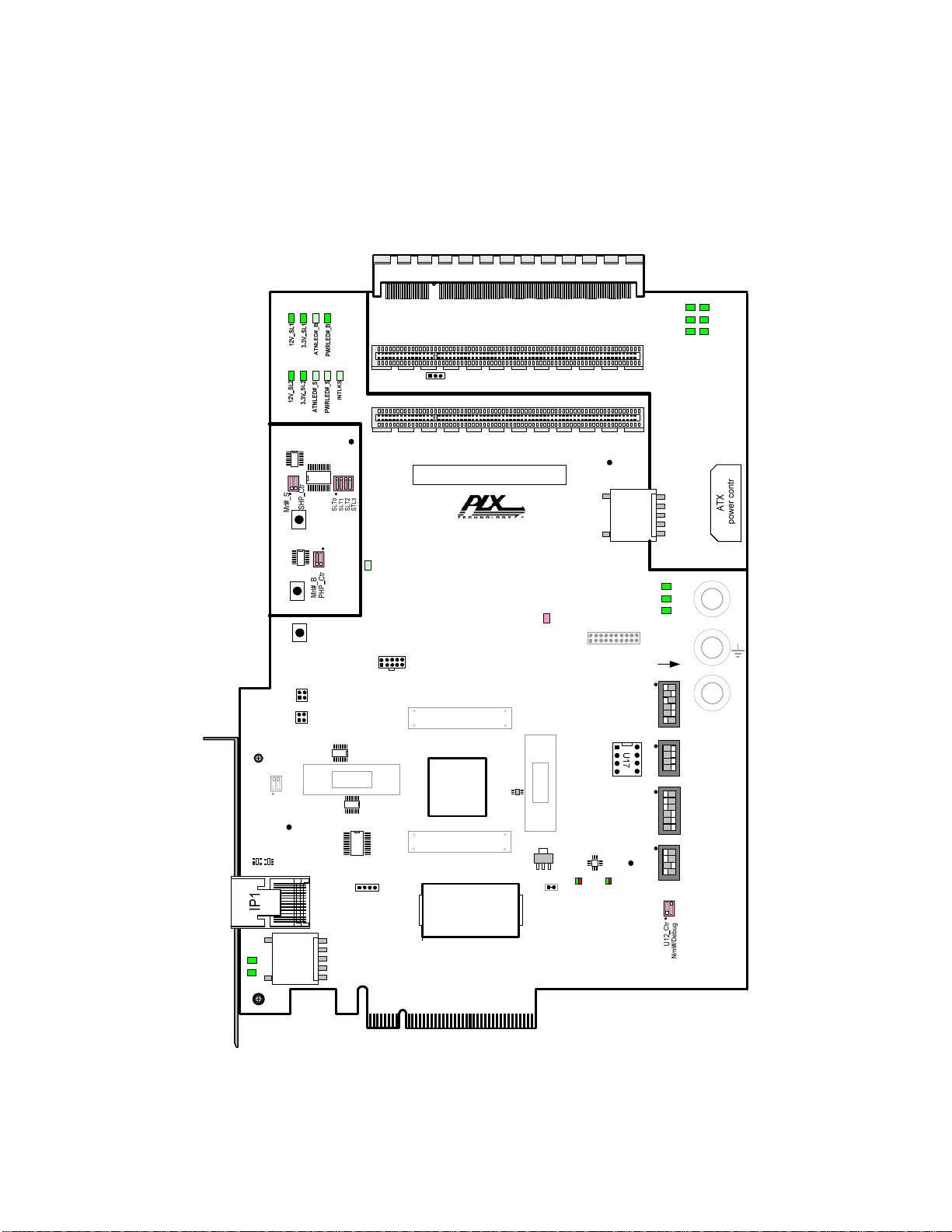

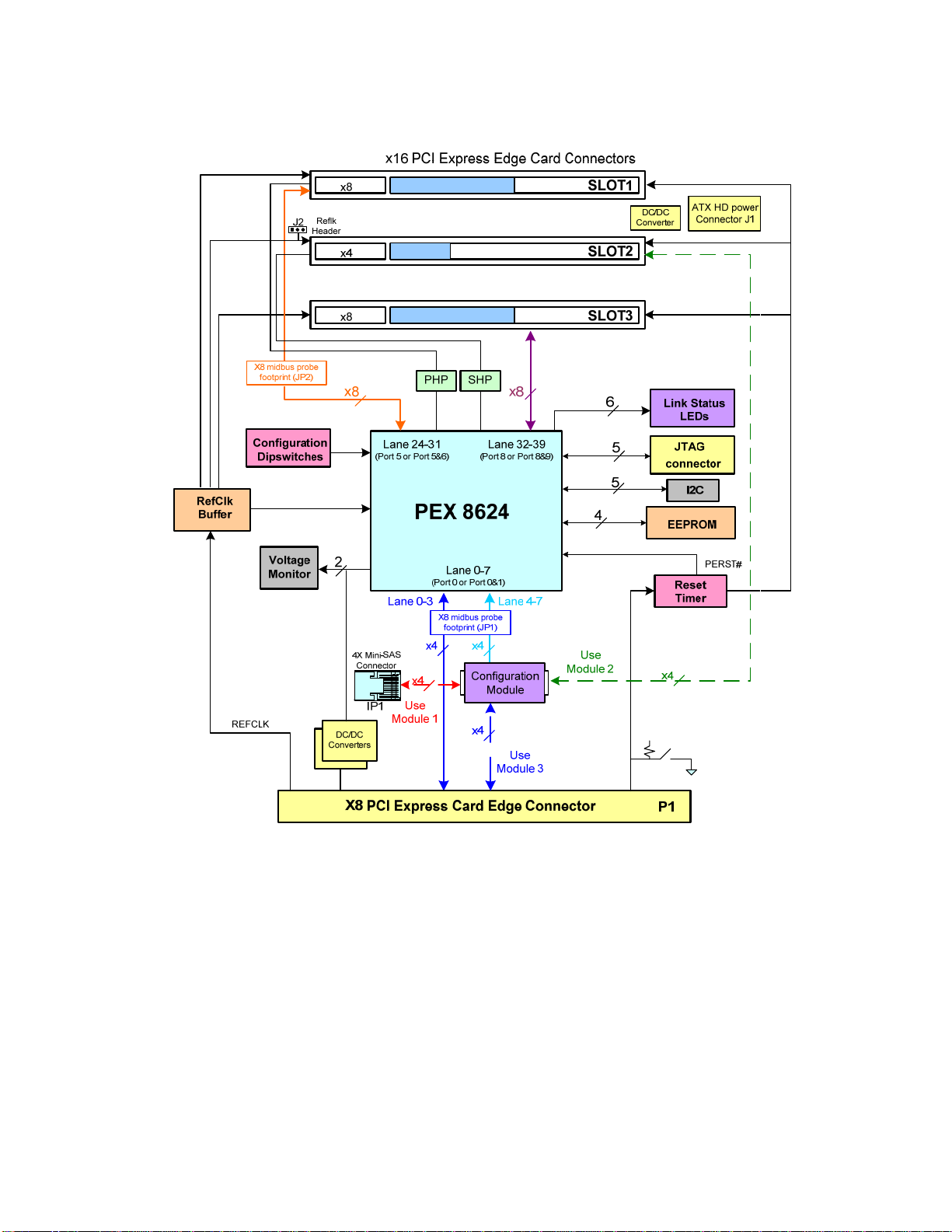

2.PEX 8624-AA RDK Hardware Architecture.......................................................................................4

2.1.1PEX 8624 PCI Express Gen 2 Switch .................................................................................. 4

2.2PEX 8624-AA RDK PCI Express Interfaces............................................................................... 4

2.2.1Configuration Modules and Receptacle CM1....................................................................... 5

2.2.2PCI Express Card Edge Connector P1.................................................................................. 6

2.2.3PCI Express Edge Card Connector SLOT 1......................................................................... 6

2.2.4PCI Express Edge Card Connector SLOT 2......................................................................... 6

2.2.5PCI Express Edge Card Connector SLOT 3......................................................................... 6

2.2.64X Mini-SAS Connector IP1................................................................................................ 6

2.3Reference Clock Circuitry............................................................................................................ 7

2.4Reset Circuitry.............................................................................................................................. 8

2.5Hot-Plug Circuits.......................................................................................................................... 8

2.5.1Parallel Hot-Plug Controller Circuit..................................................................................... 8

2.5.2Serial Hot-Plug Controller Circuits ...................................................................................... 9

2.6Serial EEPROM ......................................................................................................................... 10

2.7I2C Interface ............................................................................................................................... 10

2.8Power Distribution ..................................................................................................................... 11

2.9LED Indicators........................................................................................................................... 11

2.9.1Port Link Status Indication (D17 – D22)............................................................................ 12

2.9.2Fatal Error Indication (D24) ............................................................................................... 12

2.9.3PEX_INTA Interrupt Indication (D23)............................................................................... 12

2.9.4PEX 8624 Voltage Level Monitoring (D10 – D11)............................................................ 13

2.10GPIO Pins............................................................................................................................... 13

2.11Reserved Pins ......................................................................................................................... 13

3.On-Board Connectors, Switches, and Jumpers..................................................................................14

3.1DIP Switches.............................................................................................................................. 14

3.1.1Slot ID Selection (SW1) ..................................................................................................... 14

3.1.2Serial Hot-Plug Signal and Control (SW2)......................................................................... 14

3.1.3Parallel Hot-Plug Signal and Control (SW3)...................................................................... 15

3.1.4DC/DC Converter and Mode Controls (SW4).................................................................... 15

3.1.5Upstream Port Select (SW5)............................................................................................... 16

3.1.6Port Configuration and NT Upstream Port Select (SW6)................................................... 16

3.1.7Test Mode Select (SW7)..................................................................................................... 17

3.1.8I2C Address and Other Mode Select (SW8) ....................................................................... 18

3.2Push-Button Switches ................................................................................................................ 19

3.2.1Manual Reset# (S1)............................................................................................................. 19

3.2.2Serial Hot-Plug Controller Attention Button (S2).............................................................. 19

3.2.3Parallel Hot-Plug Controller Attention Button (S3) ........................................................... 19

3.3Midbus probe footprints (JP1 – JP2).......................................................................................... 19

3.42.5V Header (JP3)...................................................................................................................... 21

3.5JTAG Header (JP4).................................................................................................................... 21