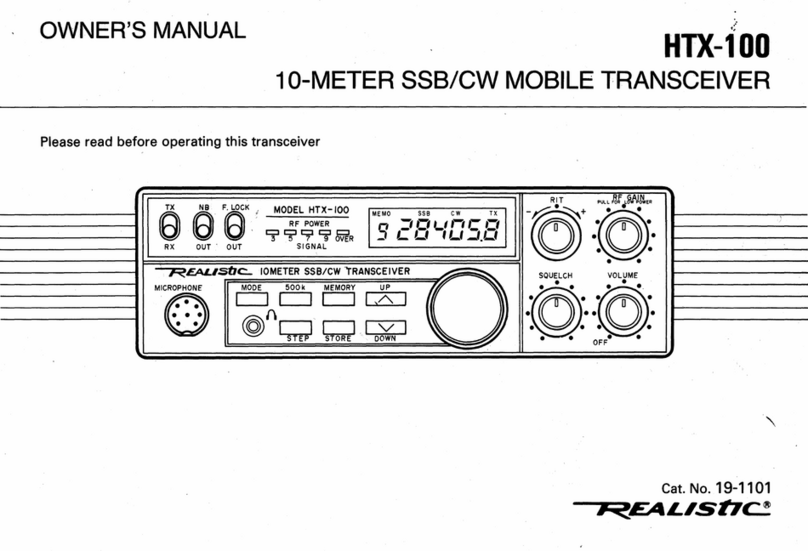

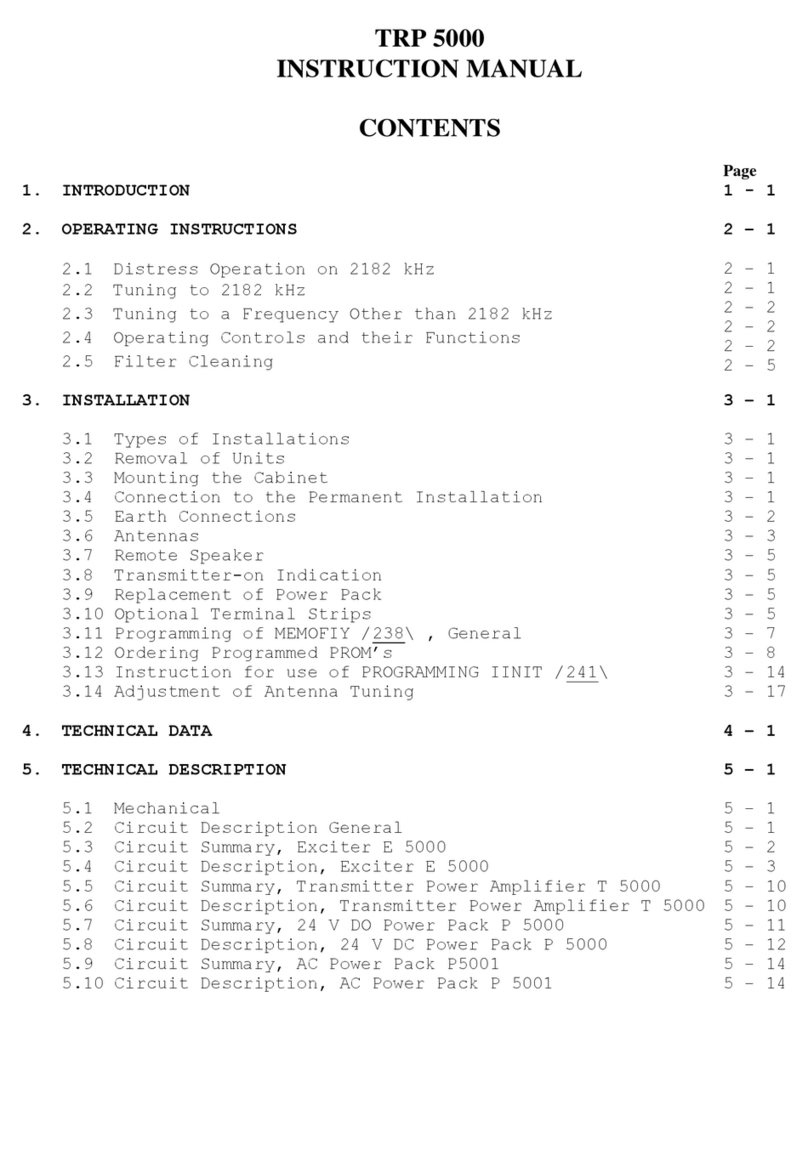

PLL

(Phase

Lock

Loop)

CIRCUIT

DESCRIPTION

The

PLL

(Phase

Lock Loop)

circuit

used

in

the

TRC-457 consists

of

6 major components; Voltage

Controlled Oscillator (VCO), 1/N Divider, Refer-

Fvco

34.7625 MHz

I

35.2075 MHz

IC 5

V.C.O.

I[]

- -

--

--

'oom'

•. •

_---

--

0

--

--

-- - -

200mv

'''

1 /

f

'''L

~

1.9VC"lC~

FET 4

Mixer 0.91 MHz

I

1.35 MHz

33.

8575

MHz

I

33.8525 MHz

ence Oscillator, 111024 Divider,

Phase

Detector

and

Low

Pass

Filter.

AMP

---

••

--

-.

-

--

--

- l lV

mTI

----

-

--------1."

--- -- -

----

-- --- -0"'

le7

TR

31

Buffer Amp.

IAI1I1

"'

1

1__U

___

U..}o

.5v

-- -

-·

-

-----

---

··

ov

70

.

91

~

1.35 MHz

r-------------------------,

X'tal3

a TR 34

OSC

11

.

2858MHzT

1....-----'

TR

35

Filter

TR

40

I Filter PHASE

Oetector

10 kHz

1/1024 I

Divider

r--_-.lf10

kHz •

I 10.24 MHz I

Programmable Divider REF.

OSC

I

X'tal4

r---

Cl

TR

38

OSC

Tripier

l /N (91-135) l

f---

i

~

L-----------e-------

_____

J

11.2842 MHz T

X'tal6

r---

C

11.2850 MHz T TR 39

OSC

I[J

Channel Selector

X'tal5

The VCO

is

an

oscillator which

controls

oscilla-

·

tion

frequency in accordance

with

input

voltage

changes.

The VCO

output

is

mixed

with

a signal in

the transmitter

or

receiver

circuitry.

A

portion

of

the VCO frequency

is

fed

to

FET4

and

mixed

with

a 33.8525 -33.8575 MHz frequency

from

X3,

X4

or

X6

and

then

goes

through

TR30

Amplifier

and

TR31

Buffer

Amp

and

then

added

to

the

1/N

Divider. This

is

applied

to

one

input

of

the

Phase

Detector.

"N"

for

the 1/N Divider

is

determined

by the Channel Selector Switch

(by

BCD)

and

varies

from

91

to

135.

On the other hand, a 10.24 MHz frequency

from

the Reference Oscillator

is

divided

to

10kHz

by

1/1024

Divider

and

applied

to

another

input

of

the

Phase

Detector. The

Phase

Detector detects the

difference

of

these

two

input

signals

and

produces

a voltage which controls the VCO frequency. The

Low

Pass

Filter

integrates the

outpuf

voltage

of

the

Phase

Detector which controls the VCO

frequency

and

the 1/N Divider produces a

10kHz

frequency.

Thus the

Phase

Detector receives

two

input

signals

(both 10 kHz).

It

compares the

phase

difference

of

the

two,

generating

an

error voltage, which acts on

the VCO

to

bring the

two

frequencies exactly in-

phase.

When this

condition

occurs, the

PLL

circuit

is

"Iocked".

Switch 10.

24

MHz

WAVE FORM O,F

le7

IC7

Pin No.

Wave

Form

IC7

?inNo.

WiNe

Form

H -

UN

L

OCKED

L =

LOCKED

where

H = 3.5 -

6V

L = 0 - 1.

0V

a

2&3

5&6

7 &

12

\0

1illl

5V

NJ

5V

lli10

5V m5V

\ -

T\

-

-,.(

2V

_

__V _V_

15V

--

- - -

-0------

-0

--

-

--0

-

--

- 0

-------0

Note:

Pin

No.

13

through 18, 20 &

21

are

as

in frequency

chart.

Pin

No. 19, 22 & 23

are

fixed

to

Low level.

By varying the constant N, the

output

frequency

from

the VCO

can

be

locked and varied one

10kHz

step at a time. The constant N

is

controlled

by

the Channel Selector Switch. A frequency

shift

of

2.5 kHz (required

for

AM

RX, USB and

AM

TX

and

LSB

RX/TX)

is

obtained

by

switching

to

X3,

X4

or

X6

as

shown in Frequency Chart.

For

a more detailed description

of

how

this

circuit

functions, refer

to

Abbreviated Block Diagram

as

well

as

the

full

Block

Diagram and Schematic.

-10

-