Singmai Electronics SM08 User manual

SM08 User Manual Revision 0.1 Page 1 of 22

SM08

Advanced Composite Video Interface:

aCVi Receiver module

User Manual

Revision 0.1

6th March 2020

SM08 User Manual Revision 0.1 Page 2 of 22

Revision History

Date

Revisions

Version

06-03-2020

First Draft.

0.1

SM08 User Manual Revision 0.1 Page 3 of 22

Contents

Revision History........................................................................................................................................2

Contents ...................................................................................................................................................3

Figures ......................................................................................................................................................3

1. Introduction ....................................................................................................................................4

2. aCVi Overview.................................................................................................................................5

3. Connecting up the module .............................................................................................................7

4. Circuit description...........................................................................................................................8

5. Specification..................................................................................................................................19

Appendix A: Power supply specification ................................................................................................20

Figures

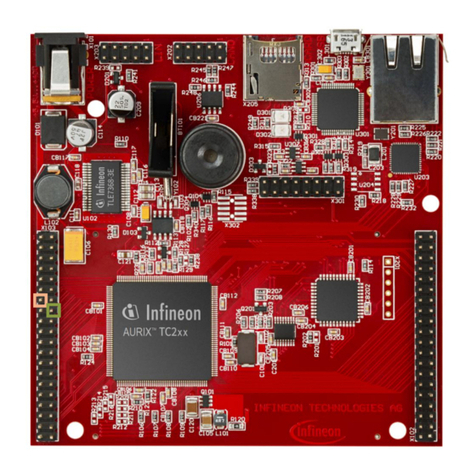

Figure 1 SM08 module..............................................................................................................................4

Figure 2 Bayer colour filter. ......................................................................................................................5

Figure 3 Left: Original full resolution image. Right: Image after Bayer demosaicing. ..............................6

Figure 4 aCVi® Modules............................................................................................................................6

Figure 5 SM08 Interconnections...............................................................................................................7

Figure 6 SM08 Schematics - Sheet 1.......................................................................................................10

Figure 7 SM08 Schematics - Sheet 2.......................................................................................................11

Figure 8 SM08 Schematics - Sheet 3.......................................................................................................12

Figure 9 SM08 Schematics - Sheet 4.......................................................................................................13

Figure 10 SM08 Schematics - Sheet 5.....................................................................................................14

Figure 11 SM08 Schematics - Sheet 6.....................................................................................................15

Figure 12 SM08 Schematics - Sheet 7.....................................................................................................16

Figure 13 SM08 Schematics - Sheet 8.....................................................................................................17

Figure 14 SM08 Schematics - Sheet 9.....................................................................................................18

Figure 15 Power supply specification - page 1. ......................................................................................20

Figure 16 Power supply specification - page 2. ......................................................................................21

Figure 17 Power supply specification - page 3. ......................................................................................22

SM08 User Manual Revision 0.1 Page 4 of 22

1. Introduction

aCVi® is a proprietary interface for transmitting high definition video over long distances of coaxial or

twisted-pair cable.

SM08 is a receiver module compatible with the aCVi® Advanced Composite Video Interface format.

SM08 accepts analogue aCVi® encoded video from both twisted pair and low-cost coaxial cable which

it converts to HD-SDI format video.

SM08 supports the following HD standards: 720p-25/30/50/59.94/60Hz and 1080p-

24/25/29.97/30Hz. Switching between standards is automatic.

Figure 1 SM08 module.

The compatible aCVi® transmitter for the SM08 receiver is the SM06 (HD-SDI input).

Other aCVi® modules/boards include:

PT56 aCVi encoder IP core.

PT52 aCVi decoder IP core.

SM02 aCVi video test pattern generator.

For the latest list of available modules follow this link.

SM08 User Manual Revision 0.1 Page 5 of 22

2. aCVi Overview

The following is a brief overview of the aCVi® revision 2 interface (abbreviated to aCVi® in this

document).

aCVi® is a proprietary format, developed by SingMai Electronics, to transmit high definition video over

long distances of coaxial or twisted pair cable. aCVi® is an update to the previous version, specifically

designed to interface directly to image sensors, although it may also be used to transmit conventional

video sources.

A single chip image sensor, as found in almost all non-broadcast cameras, uses a colour filter to

‘assign’ each sensor pixel one of red, green or blue sensitivities. Because green is where the human

eye is most sensitive, there are twice as many green pixels as red and blue (see Figure 2). This means

that if your sensor has a horizontal array of 1920 pixels, only 960 of them are green, red or blue pixels,

and for the red and blue pixels, each horizontal line is either red or blue. The actual resolution of the

sensor to each colour is for green, 960 x 1080 pixels, and for red and blue, 960 x 540 pixels. (A

broadcast camera will use three optically aligned sensors, each offering 1920 x 1080 pixels for the

three colours). If we refer to the full resolution (e.g. a broadcast camera) as 4:4:4 sampled, a single

image sensor actually produces a 2:2:0 output.

Figure 2 Bayer colour filter.

To conform with video standards (e.g. 1920 x 1080) the additional pixels are interpolated (a technique

known as Bayer de-mosaicing) and this function is usually performed in the camera ISP (Image Signal

Processor). However this process can produce artifacts into the image (for example see the colour

artifacts on the white fence in Figure 3), and also, because it generates more than double the amount

of original pixels, more than doubles the bandwidth of the output signal, which exacerbates the

problem if the video is required to transmitted long distances.

aCVi® interfaces directly to the single chip image sensor and transmits the RAW 2:2:0 resolution

image directly, thereby reducing by more than half the bandwidth of the transmitted signal and

achieving higher resolution, lower noise and greater distances.

SM08 User Manual Revision 0.1 Page 6 of 22

Figure 3 Left: Original full resolution image. Right: Image after Bayer demosaicing.

The available aCVi® modules are shown in Figure 4. The SM06 provides an aCVi® transmitter for HD-

SDI or DVI video sources (e.g. a video camera) and simultaneously drives both coaxial and twisted-pair

cable.

The receiver module is the SM08. This module accepts either twisted-pair or coaxial cable and

converts the aCVi® video to an HD-SDI output for a TV monitor or video recorder.

Figure 4 aCVi® Modules.

SM08 User Manual Revision 0.1 Page 7 of 22

3. Connecting up the module

The SM08 module is powered by a universal input (90-260VAC) AC-DC adaptor (see Appendix A for

the power supply specification). The 5VDC, 12W output of this adaptor should be connected to the

jack input, ‘+5V IN’, of the SM08. Once connected, the yellow LED, ‘FPGA OK’ should light, indicating

the FPGA has been correctly configured and the module is running.

Figure 5 shows the interconnections for SM08.

Figure 5 SM08 Interconnections.

The video input is connected to either the coaxial BNC connector or the RJ-45 style twisted pair

connector. Do not connect both cable type inputs at the same time. aCVi®assumes the UTP cable

connections are ‘straight’ so both the transmitter and receiver use pin 1 for the ‘VIDEO+’ (non-

inverted) signal, and pin 2 ‘VIDEO-‘ (inverted) signal.

If the aCVi®input is valid and can be locked to, the yellow ‘Lock’ LED will light –the SM08

automatically detects the input video standard. Once the aCVi®decoder has locked and is

decoding the yellow ‘SDI lock LED’ should light, indicating the HD-SDI output is valid. The HD-SDI

video can then be connected to video monitor or video recorder.

SM08 User Manual Revision 0.1 Page 8 of 22

4. Circuit description

Figures 6-14 show the schematics for the SM08. Below is a brief technical description of the module.

Sheet 1.

J3 is the 5VDC power input connector to the SM08 module. The 5VDC is protected from over-voltage

and reverse polarity inputs by D1, D2 and resettable fuse, F1. The input is then filtered by L1 and C2 to

provide the ‘clean’ 5VDC for the analogue input stage and also linear regulated by U1 and U8 to

provide the 3.3VDC and 2.5VDC supply voltages. U7 provides a power on reset for the FPGA.

Sheet 2.

U2 provides the 1.2VDC for the internal voltage of the FPGA. U3 provides the 2.5VDC for the analogue

PLL circuity of the FPGA and L2 and C25 filter the VCCINT for the FPGA PLL digital blocks.

Sheet 3.

Sheet 3 is the analogue front end (AFE). The aCVi® analogue video inputs may be either coaxial or

twisted pair.

If twisted pair, they are terminated in 100Ω (R26) and converted from differential to single ended

outputs by U9. If coaxial inputs they are treated as a pseudo-differential input, with the ground screen

of the BNC input connector connected to ground via R25 and C61, which affords some hum rejection

for long cable runs. U15 converts this pseudo-differential input to a singled ended output. The two

amplifier outputs are AC coupled and joined together; for this reason only one cable type input should

be connected at one time.

U10 is a voltage-controlled amplifier. The aCVi® decoder measures the amplitude of the synchronizing

signals and compares them to an internal reference: this amplifier compensates for the signal loss in

the cable. The PWM Gain signal from the FPGA is low pass filtered and used to control the gain of

U10.

The output of U10 is AC coupled into U11A, which is a high input impedance, low input bias current

op-amp –U11B is not used for aCVi®. The AC coupled video is set the mid-point of the ADC operating

range (1.5VDC - the ADC requires a 0.5V to 2.5V (2V pk-pk) input signal).

Sheet 4.

U19 is a dual 10 bit, 80MHz ADC. The ADC is used in single-ended mode. The clamped video from

U11A is applied to the VIN+ input of both ADCs, and VIN- input is biased to mid rail (1.5V). U14

provides the ‘clean’ 3.0V supply for the ADC. The output of the ADC, ADC[9:0] is the 2’s complement,

digital composite video which is applied directly to the aCVi decoder. The two ADCs are clocked out of

phase and the outputs multiplexed in the aCVi® decoder. This effectively produces a twice sample

rate output (i.e. 74.25MHz clock produces a 148.5MHz data rate).

Sheet 5.

U4 is the FPGA. The FPGA is an Altera EP4CE15 device in a 144 pin 0.5mm TQFP package. The FPGA

contains the PT52 aCVi® decoder, a SingMai PT13 control microprocessor and the HD-SDI output

encoder.

Sheet 6.

The FPGA is a volatile device and needs configuring at switch on, which it does using U5, a 4Mb

EEPROM. The device is automatically configured on switch on, and successful configuration is

indicated by LED, ‘FPGA OK’. The EEPROM may also be reprogrammed via J4, which is compatible with

the Altera ‘USB-Blaster’ and the Quartus Programmer.

Sheet 7.

The PT52 aCVi decoder requires a line locked clock. This is achieved using a voltage-controlled crystal

oscillator, with the frequency of the oscillator controlled using a PWM output from the PT52 IP core.

This output, VCO_PWM, is filtered by R14 and C31 to provide an analogue voltage which is buffered

by U6. The resulting 0-3.3V control voltage adjusts the frequency of the crystal voltage-controlled

SM08 User Manual Revision 0.1 Page 9 of 22

oscillator (VCXO), X1. The adjustment range is approximately ±150ppm. The centre frequency

(1.65VDC control voltage) is 27.0MHz.

The output of the VCXO is then multiplied to 74.25MHz or 74.18MHz (to provide support for

29.97/59.94Hz formats) –selection is performed via the FREQ_SEL.

The ‘LOCK’ LED is driven from a port of the FPGA. It is lit when the aCVi® decoder status indicates that

horizontal lock has been achieved and the input is a valid standard supported by the decoder.

U17 is an RS232 level translator. The RS232 data interface is not enabled at this time.

Sheet 8.

This sheet is not currently fitted.

Sheet 9.

The Y, Cb and Cr video and the Hout, Vout and Fout synchronizing signals from the aCVi decoder are

formatted into an HD-SDI signal inside the FPGA. The synchronizing signals are modified to be

compatible with the HD-SDI Flag requirements and the line count is derived. The video and the timing

signals (TRS) are combined and scrambled according to the HD-SDI specification and cyclic

redundancy check (CRC) is added.

The scrambled signal is then multiplexed into 5 data streams at 148.5MHz which are driven as LVDS

outputs, together with an LVDS clock, to the HD-SDI serialiser IC, U18, which converts these five data

signals into one 1.485GHz, HD-SDI compatible, output (J9).

SM08 User Manual Revision 0.1 Page 10 of 22

Figure 6 SM08 Schematics - Sheet 1.

SM08 User Manual Revision 0.1 Page 11 of 22

Figure 7 SM08 Schematics - Sheet 2.

SM08 User Manual Revision 0.1 Page 12 of 22

Figure 8 SM08 Schematics - Sheet 3.

SM08 User Manual Revision 0.1 Page 13 of 22

Figure 9 SM08 Schematics - Sheet 4.

SM08 User Manual Revision 0.1 Page 14 of 22

Figure 10 SM08 Schematics - Sheet 5.

SM08 User Manual Revision 0.1 Page 15 of 22

Figure 11 SM08 Schematics - Sheet 6.

SM08 User Manual Revision 0.1 Page 16 of 22

Figure 12 SM08 Schematics - Sheet 7.

SM08 User Manual Revision 0.1 Page 17 of 22

Figure 13 SM08 Schematics - Sheet 8.

SM08 User Manual Revision 0.1 Page 18 of 22

Figure 14 SM08 Schematics - Sheet 9.

SM08 User Manual Revision 0.1 Page 19 of 22

5. Specification

Power: +5VDC ± 5% @ ~620mA.

Dimensions: 120mm x 78mm x 27mm.

HD-SDI output: SMPTE-292M, 20 bit 4:2:2 YCbCr format.

Video standards: 720p/25Hz,720p/30Hz, 720p/50Hz, 720p/59.94Hz, 720p/60Hz

1080p/25Hz, 1080p/29.97Hz, 1080p/30Hz.

Luma bandwidth: 14MHz ± 1dB. >-50dB @ 17.6MHz.

Chroma bandwidth: 14MHz ± 1dB. >-40dB @ 17.6MHz.

Transmission distance: >300m of RG-59 coaxial cable. >500m RG-59 cable

with reduced luma bandwidth.

Latency: <100µs (transmitter HD-SDI input to receiver HD-SDI output).

Operating temperature: -10° to +45°degC.

SM08 User Manual Revision 0.1 Page 20 of 22

Appendix A: Power supply specification

The AC-DC converter supplied with the SM06 is a model TE10A0503F01 from SL Power Electronics. It

accepts all AC inputs from 90-264VAC and provides a 5V, 2A DC output for the SM06. The detailed

specification is shown below.

Figure 15 Power supply specification - page 1.

Other manuals for SM08

1

Table of contents

Popular Control Unit manuals by other brands

NI

NI PXI-6682 user manual

powersoft

powersoft DigiMod IS integration kit Technical note

GEM

GEM 534 Installation, Operating and Maintenance Instruction

Dormakaba

Dormakaba MFC installation instructions

Honeywell

Honeywell DirectLine DL421 user manual

PDi

PDi PD196-244R12 Installation and operating instructions