STMicroelectronics STP1612PW05 User manual

Preliminary data

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to

change without notice.

December 2009 Doc ID 15819 Rev 4 1/35

35

STP1612PW05

16-channel LED driver with 16-bit PWM,

8-bit gain and full LED error detection

Features

■16 constant current output channels

■Supply voltage: 3.3 V or 5 V

■Two PWM selectable counters 12/16-bit of

grayscale

■Selectable enhanced PWM for ghost effect

reduction

■Open and short LED detection

■8-bit current gain control by means of 256

steps in two selectable ranges

■Single resistor to set the current from 3 mA to

60 mA

■Programmable progressive output delay

■Thermal protection and thermal flag

■UVLO

■Schmitt trigger input

■Selectable 16-bit or 256-bit serial data-in

format

■Max clock frequency: 30 MHz

■ESD protection 2.5 kV HBM, 200 V MM

■Drop-in compatible with STP16CP\S\DP05

series

■Available in high thermal efficiency TSSOP

exposed pad

Applications

■Video display LED panels

■RGB backlighting

■Special lighting

Description

The STP1612PW05 is a 16-channel constant

current sink LED driver. The maximum output

current value for all the 16 channels is set by a

single resistor from 3 mA to 60 mA. The device

features 8-bit gain (256 steps) for global LED

brightness adjustment with two selectable ranges.

This function is accessible via a serial interface.

The device has an individual adjustable PWM

brightness control for each output channel. The

PWM counters are selectable via a serial

interface with 4096 or 65536 steps (12 or 16 bit).

The STP1612PW05 also provides enhanced

pulse-width modulation counting algorithms called

e-PWM to reduce flickering effects (ghost visual

effects) improving the overall image quality. The

device has a dual size 16-bit or 256-bit shift

register. All the control and the shift register read

back data are accessible via serial interface. The

STP1612PW05 has the capability to detect open

and short LED failure and overtemperature,

reporting the status through SPI line. The device

guarantees a 20 V output driving capability,

allowing the user to connect more LEDs in series.

SO-24

TSSOP24 TSSOP24

exposed pad

QFN-24

Table 1. Device summary

Order code Package Packaging

STP1612PW05QTR QFN-24 4000 parts per reel

STP1612PW05MTR SO-24 1000 parts per reel

STP1612PW05TTR TSSOP24 2500 parts per reel

STP1612PW05XTTR TSSOP24 exposed pad 2500 parts per reel

www.st.com

Contents STP1612PW05

2/35 Doc ID 15819 Rev 4

Contents

1 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2 Summary description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.1 Pin connection and description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3 Electrical ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.1 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.2 Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.3 Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

5 Timing waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

6 Principle of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

7 Definition of configuration register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

8 Grey scales data loading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

9 Setting the PWM gray scale counter . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

9.1 PWM data synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

9.2 Synchronization for PWM counting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

10 Error detection conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

11 Setting output current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

12 Current gain adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

13 Delay time of staggered output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

14 Thermal protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

15 Time-out alert of GCLK disconnection . . . . . . . . . . . . . . . . . . . . . . . . . 24

Block diagram STP1612PW05

4/35 Doc ID 15819 Rev 4

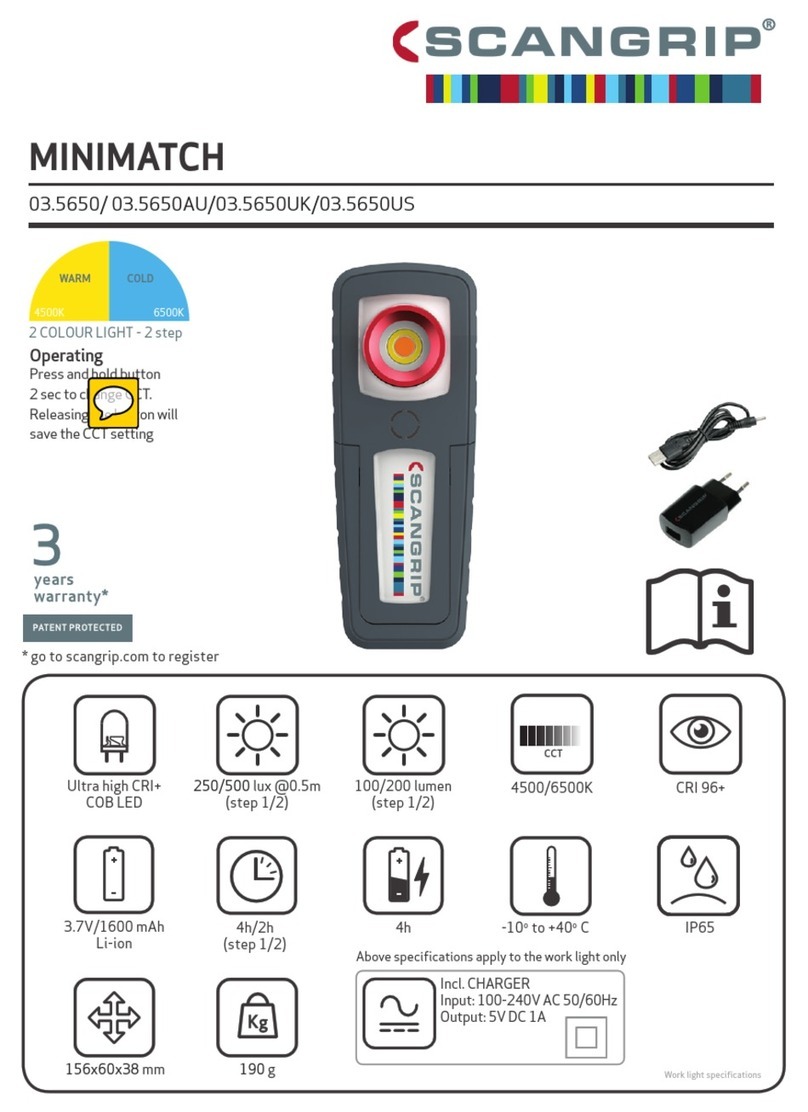

1 Block diagram

Figure 1. Block diagram

PWM and e-PWM

12/16 bit counter

and SYNC control

Serial interface

UVLO & POR

VDD

GND

SDI

CLK

LE

SDO

Constant current output channels

1----------16

TSD

16-bit

Configuration

Register

Shift register

dual size mode

(16 or 256 bit)

PWCLK

Dual range gain

7-bit DAC

PWM databuffer

(16x16 bit)

Gradual outputs

delay

CTRL command

and

CTRL logic

Open/short

error detection

R-EXT

STP1612PW05 Summary description

Doc ID 15819 Rev 4 5/35

2 Summary description

Table 2. Typical current accuracy at 5 V

Output voltage

Current accuracy

Output current VDD temp.

Between bits Between ICs

≥1.0 ± 1.5% ± 6% 15 to 60 5 V 25 °C

≥0,2 ± 1.5% ± 6% 3 to 15

Table 3. Typical current accuracy at 3.3 V

Output voltage

Current accuracy

Output current VDD temp.

Between bits Between ICs

≥1.0 ± 1.5% ± 6% 15 to 60 3.3 V 25 °C

≥0,3 ± 1.5% ± 6% 3 to 15

Summary description STP1612PW05

6/35 Doc ID 15819 Rev 4

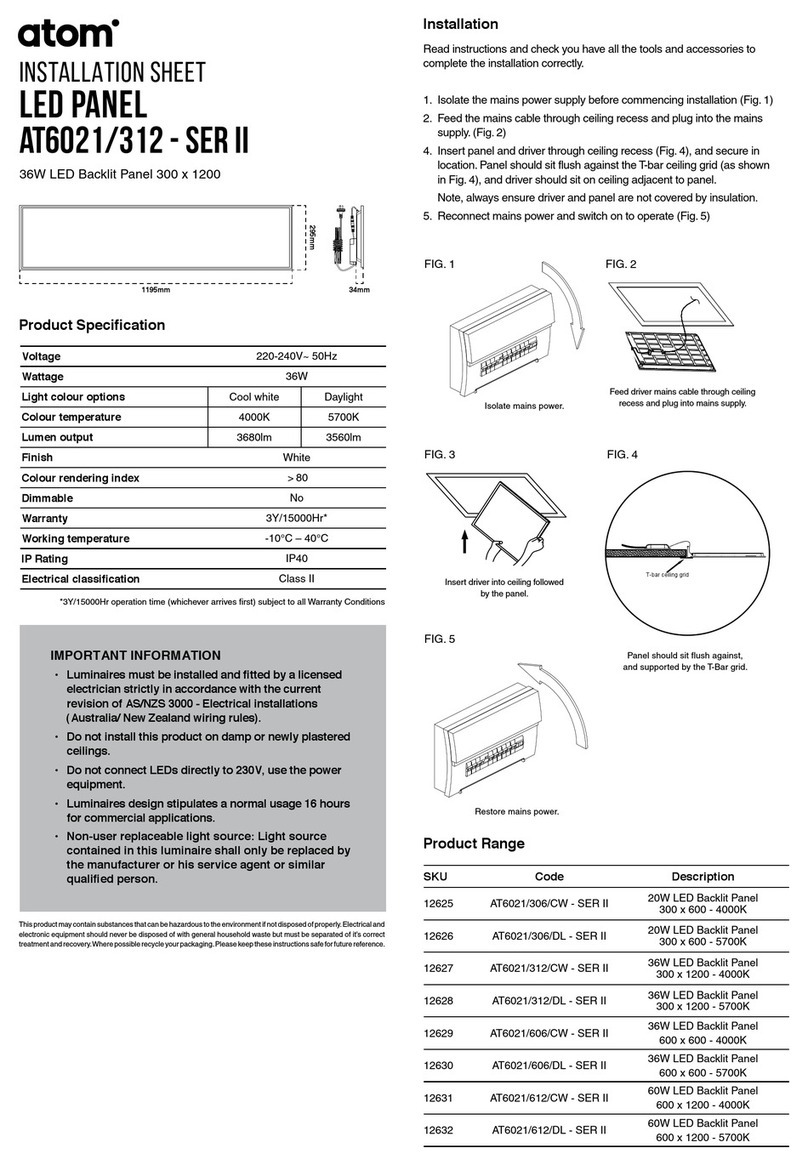

2.1 Pin connection and description

Figure 2. Pin connection

Note: The exposed pad should be electrically connected to a metal land electrically isolated or

connected to ground

14

13

15

16

17

18

5

6

4

3

2

1

8

79101112

23

24 22 21 20 19

CLK

SDI

VDD

R-EXT

SDO

OUT7

OUT4

OUT6

OUT3

OUT2

OUT1

OUT0

LE

OUT8

OUT13

OUT12

OUT11

OUT10

OUT9

OUT5

OUT14

OUT15

PWCLK

GND

Table 4. Pin description

Pin n° Symbol Name and function

1 GND Ground terminal

2 SDI Serial data input terminal

3CLK

Clock input terminal used to shift data on rising edge and carries

command information when LE is asserted.

4 LE Data strobe terminal and controlling command with CLK

5-20 OUT 0-15 Output terminals

21 PWCLK Gray scale clock terminal.

Reference clock for grey scale PWM counter.

22 SDO Serial data out terminal

23 R-EXT Input terminal of an external resistor for constant current programing

24 VDD Supply voltage terminal

STP1612PW05 Electrical ratings

Doc ID 15819 Rev 4 7/35

3 Electrical ratings

3.1 Absolute maximum ratings

Stressing the device above the rating listed in the Ta bl e 5 may cause permanent damage to

the device. These are stress ratings only and operation of the device at these or any other

conditions above those indicated in the operating sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect device

reliability.

3.2 Thermal data

Table 5. Absolute maximum ratings

Symbol Parameter Value Unit

VDD Supply voltage 0 to 7 V

VOOutput voltage -0.5 to 20 V

IOOutput current 60 mA

VIInput voltage -0.4 to VDD V

IGND GND terminal current 1300 mA

fCLK Clock frequency 50 MHz

TJJunction temperature range (1)

1. Such absolute value is based on the thermal shutdown protection.

-40 to + 170 °C

Table 6. Thermal data

Symbol Parameter Value Unit

TAOperating free-air temperature range -40 to +125 °C

TJ-OPR Operating thermal junction temperature range -40 to +150 °C

TSTG Storage temperature range -55 to +150 °C

RthJA

Thermal resistance junction-

ambient (1)

1. According to Jedec standard 51-7B

SO-24 42.7 °C/W

TSSOP24 55 °C/W

TSSOP24(2)

Exposed pad

2. The exposed pad should be soldered directly to the PCB to realize the thermal benefits.

37.5 °C/W

QFN-24 55 °C/W

Electrical ratings STP1612PW05

8/35 Doc ID 15819 Rev 4

3.3 Recommended operating conditions

Table 7. Recommended operating conditions at 25 °C, VDD = 5 V

Symbol Parameter Test conditions Min. Typ. Max. Unit

VDD Supply voltage 3.0 - 5.5 V

VOOutput voltage - 20 V

IOOutput current OUTn 3 - 60 mA

IOH Output current SERIAL-OUT - +1 mA

IOL Output current SERIAL-OUT - -1 mA

VIH Input voltage 0.7 VDD -V

DD V

VIL Input voltage GND - 0.3 VDD V

twLAT LE pulse width

VDD = 3.3 V to 5.0 V

20 - ns

twCLK CLK pulse width 10 - ns

twEN PWCLK pulse width 20 - ns

tSETUP(D) Setup time for DATA 5 - ns

tHOLD(D) Hold time for DATA 5 - ns

tSETUP(L) Setup time for LATCH 5 - ns

fCLK Clock frequency Cascade operation (1)

1. If the device is connected in cascade, it may not be possible achieve the maximum data transfer. Please

considered the timings carefully.

-30MHz

STP1612PW05 Electrical characteristics

Doc ID 15819 Rev 4 9/35

4 Electrical characteristics

TA= 25 °C (Unless otherwise specified)

Table 8. Electrical characteristics (VDD = 5.0 V)

Symbol Characteristics Test conditions Min. Typ. Max. Unit

VDD Supply voltage 4.5 5.0 5.5 V

VOMaximum output

voltage OUT0 ~ OUT15 20 V

IOUT

Output current

VO= 1.2V 5 60 mA

IOH SDO, TA= - 40 ~ 125 °C -8 mA

IOL SDO, TA= - 40 ~ 125 °C 8 mA

VIH

Input voltage

“H” level TA= - 40 ~ 125 °C 0.7 *

VDD VDD V

VIL

Input voltage

“L” level TA= - 40 ~ 125 °C GND 0.3 *

VDD

V

IOH

Output leakage

current VO= 20 V 10 μA

VOL Output voltage

SDO

IOL = + 1.0 mA,

TA= - 40 ~ 125 °C 0.4 V

VOH

IOH = -1.0 mA

TA= - 40 ~ 125 °C

VDD -

0.4 V

dIOUT1

Current skew

(Channel)

IOUT = 10 mA

VO= 1.0 V, Rext = 69 kΩ± 1.5 ± 3.0 %

dIOUT2 Current skew (IC) IOUT = 10 mA

VO= 1.0 V, Rext = 69 kΩ± 3.0 ± 6.0 %

%/dVO

Output current vs.

output voltage

regulation

VO within 1.0 V and 3.0 V,

Rext = 34.7 kΩ @ 20 mA ± 0.1 ± 0.5 % / V

%/dVDD

Output current vs.

supply voltage

regulation

VDD within 4.5 V and 5.5 V ± 1.0 ± 5.0 % / V

VO,TH 0.15 0.20 V

RIN(down) Pull-down resistor LE 150 200 250 kΩ

IDD(off) 1

Supply current

“Off”

Rext = Open,

OUT0 ~ OUT15 = Off 71013

mA

IDD(off) 2

IO = 20 mA,

OUT0 ~ OUT15 = Off 6.6 9.5 12

IDD(off) 3 IO= 60 mA,

OUT0 ~ OUT15 = Off 9 12.7 16.5

IDD(on) 1 Supply current

“On”

IO= 20 mA,

OUT0 ~ OUT15 = On 6.6 9.4 12.2

IDD(on) 2 IO= 60 mA,

OUT0 ~ OUT15 = On 8 11.5 14.9

Electrical characteristics STP1612PW05

10/35 Doc ID 15819 Rev 4

Table 9. Electrical characteristics (VDD = 3.3 V)

Symbol Characteristics Test conditions Min. Typ. Max. Unit

VDD Supply voltage 3.0 3.3 3.6 V

VO

Sustaining voltage at

OUT Ports OUT0 ~ OUT15 20 V

IOUT

Output current

VO= 1.2 V 5 60 mA

IOH SDO, TA= -40 ~ 125 °C-1.0 mA

IOL SDO TA= -40 ~ 125 °C1.0 mA

VIH Input voltage “H” level TA= - 40 ~ 125 °C 0.7 *

VDD

VDD V

VIL Input voltage “L” level TA= - 40 ~ 125 °C GND 0.3 *

VDD

V

IOH Output leakage current VO= 17.0 V 0.5 μA

VOL

Output voltage SDO

IOL = +1.0 mA,

TA= -40 ~ 125 °C 0.4 V

VOH

IOH = -1.0 mA

TA= -40 ~ 125 °C 2.9 V

dIOUT1 Current skew (channel)

IOUT = 10.5 mA,

VO= 1.0 V,

Rext = 69 kΩ at 10 mA

± 1.5 ± 3.0 %

dIOUT2 Current skew (IC)

IOUT = 10.8 mA,

VO = 1.0 V,

Rext = 69 kΩat 10 mA

± 3.0 ± 6.0 %

%/dVO

Output current vs.

output voltage regulation

VOwithin 1.0 V and 3.0 V,

Rext = 34.7 kΩat 20 mA ± 0.1 ± 0.5 % / V

%/dVDD

Output current vs.

supply voltage

regulation

VDD within 3.0 V

and 3.6 V ± 1.0 ± 5.0 % / V

RIN(down) Pull-down resistor LE 150 200 250 kΩ

IDD(off) 1

Supply current “OFF”

Rext = Open,

OUT0 ~ OUT15 = Off 7.2 9.3

mA

IDD(off) 2 IO= 20 mA,

OUT0 ~ OUT15 = Off 8.6 11

IDD(off) 3 IO= 60 mA,

OUT0 ~ OUT15 = Off 11.7 15.2

IDD(on) 1

Supply current “ON”

IO= 20 mA,

OUT0 ~ OUT15 = On 29 37.7

IDD(on) 2

IO= 60 mA,

OUT0 ~ OUT15 = On 31.2 40

STP1612PW05 Electrical characteristics

Doc ID 15819 Rev 4 11/35

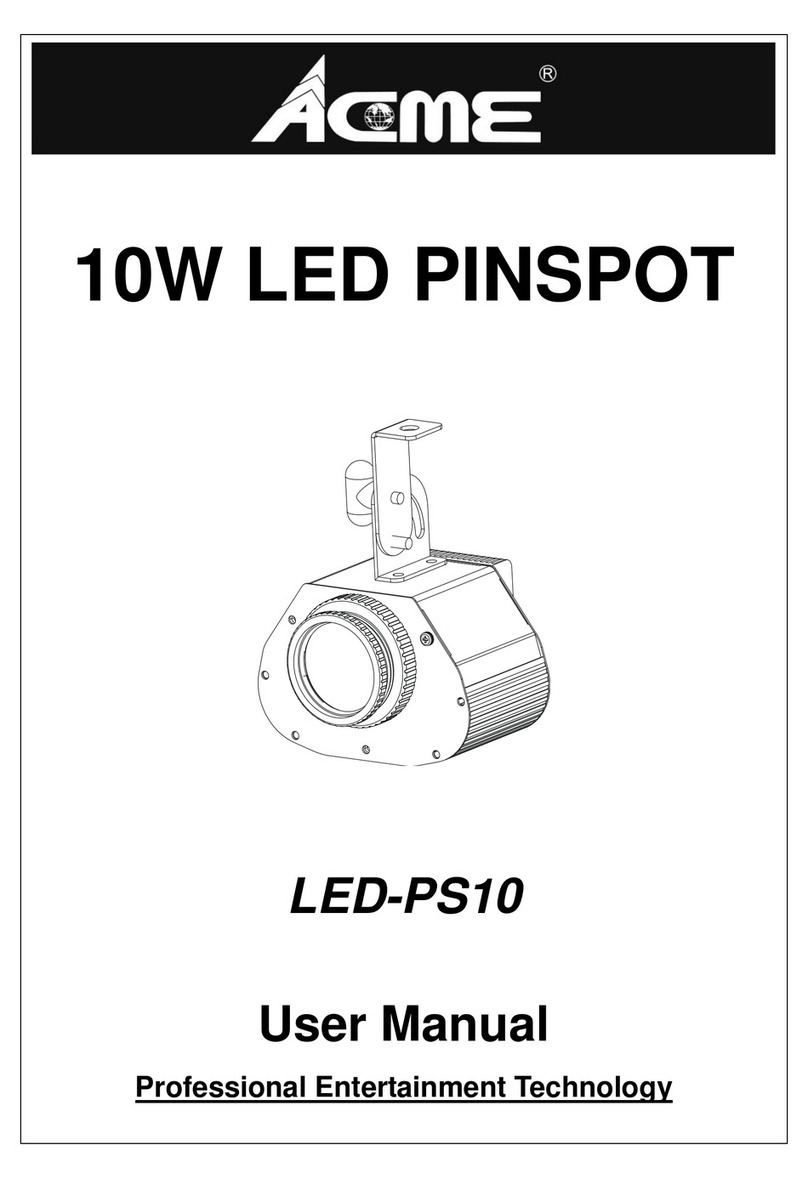

Figure 3. Test circuit for electrical characteristics

Table 10. Switching characteristics (VDD = 5.0 V) TA= -40 ~ 125 °C

Symbol Characteristics Conditions Min. Typ. Max. Unit

tSU0

Setup time

SDI - CLK ↑

VDD = 5.0 V

VIH = VDD

VIL = GND

Rext = 460 Ω

VLED = 4.5 V

RL= 152 Ω

CL = 10 pF

C1 = 100 nF

C2 = 10 μF

IO= 20 mA

1 ns

tSU1 LE ↑– DCLK ↑1 ns

tSU2 LE ↓– DCLK ↑5 ns

tH0 Hold time CLK ↑- SDI 3 ns

tH1 CLK ↑- LE ↓7 ns

tPD0

Propagation

delay time

CLK - SDO 30 40 ns

tPD1 PWCLK-OUTn4 (1)

1. Refer to the timing waveform, where n = 0, 1, 2, 3.

100 ns

tPD2 LE – SDO(2)

2. In timing of “read configuration” and “read error status code”, the next CLK rising edge should be tPD2 after

the falling edge of LE.

30 40 ns

tDL1

Stagger delay

time

OUTn4 + 1 (1) 40 ns

tDL2 OUTn4 + 2 (1) 80 ns

tDL3 OUTn4 +3 (1) 120 ns

tw(L)

Pulse width

LE 5 ns

tw( CLK) CLK 20 ns

tw(PWCLK) PWCLK 20 ns

tON Output rise time of output ports 10 ns

tOFF Output fall time of output ports 6 ns

tEDD Error detection minimum duration (3)

3. Refer to Figure 5 on page 13.

1µs

PWCLK

CLK

LE

DDV

EXT-R GND SDO

OUT0

.

.

.

Generator

Function

DDI

VIH

=VDD

VIL

=GND

waveform

inputLogic

SDI

OUT15

OUTI

VIH,VIL

VDD

Rext

IOL

IOH

Electrical characteristics STP1612PW05

12/35 Doc ID 15819 Rev 4

Figure 4. Test circuit for switching characteristics

Table 11. Switching characteristics (VDD = 3.3 V)

Symbol Characteristics Conditions Min. Typ. Max. Unit

tSU0

Setup time

SDI - DCLK ↑

VDD = 3.3 V

VIH = VDD

VIL = GND

Rext = 460 Ω

VLED = 4.5 V

RL= 152 Ω

CL = 10 pF

C1 = 100 nF

C2 = 10 μF

1 ns

tSU1 LE ↑– DCLK ↑1 ns

tSU2 LE ↓– DCLK ↑5 ns

tH0 Hold time CLK ↑- SDI 3 ns

tH1 CLK ↑- LE ↓7 ns

tPD0

Propagation delay

time

CLK - SDO 45 40 ns

tPD1 PWCLK-OUTn4(1)

1. Refer to the timing waveform Figure 4, where n = 0, 1, 2, 3.

120 ns

tPD2 LE – SDO(2)

2. In timing of “read configuration” and “read error status code”, the next CLK rising edge should be tPD2 after

the falling edge of LE.

45 40 ns

tDL1

Stagger delay

time

OUTn4 + 1 (1) 40 ns

tDL2 OUTn4 + 2 (1) 80 ns

tDL3 OUTn4 +3 (1) 120 ns

tw(L)

Pulse width

LE 5 ns

tw(CLK) CLK 20 ns

tw(PWCLK) PWCLK 20 ns

tON Output rise time of output ports 11.6 ns

tOFF Output fall time of output ports 7 ns

tDEC Error detection duration 0.5 1 μs

PWCLK

CLK

LE

DDV

EXT-R GND SDO

OUT0

.

.

.

Generator

Function

DDI

OUT

I

C

L

V

LEDwaveform

inputLogic

SDI

OUT15

1

C

2

C

VIH,VIL

VIH=VDD

VIL=GND

Rext

R

L

R

L

C

L

C

L

VDD

STP1612PW05 Timing waveform

Doc ID 15819 Rev 4 13/35

5 Timing waveform

Figure 5. Timing waveform

PWCLK

PWCLK

PWCLK

Principle of operation STP1612PW05

14/35 Doc ID 15819 Rev 4

6 Principle of operation

Table 12. Control command

Signals combination Description

Command name LE

Number of CLK

rising edge when

LE is asserted

The action after a falling edge of LE

Data latch High 1 Serial data are transferred to the buffers

Global latch High 2 or 3 Buffer data are transferred to the comparators

Read configuration High 4 or 5 Move out “configuration register” to the shift

register

Enable “error

detection” High 6 or 7 Detect the status of each output’s LED

Read “error status

code” High 8 or 9

Move out “error status code” of 16 outputs to

the shift registers

Write configuration High 10 or 11 Serial data are transferred to the

“configuration register”

Reset to 16-bit shift

register length High 12 or 13 Set to 16-bit the shift register length

STP1612PW05 Principle of operation

Doc ID 15819 Rev 4 15/35

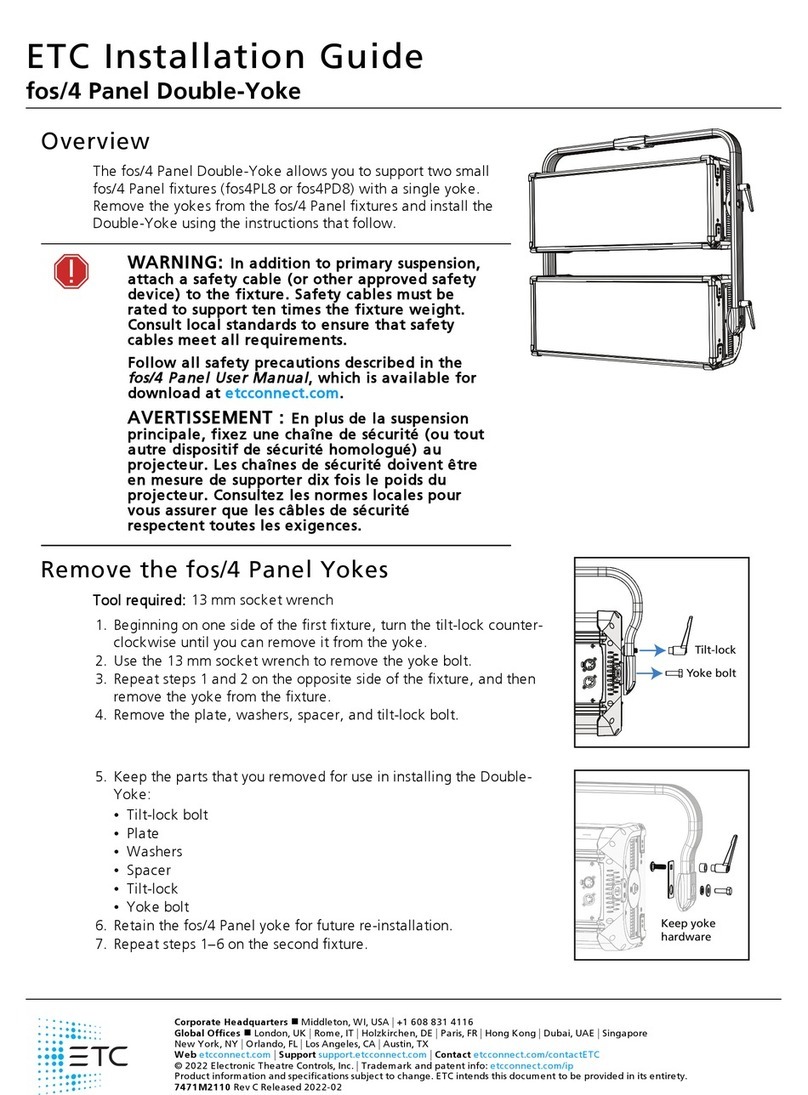

Figure 6. Timing diagram

$ATA,ATCH

'LOBAL,ATCH

2EAD#ONFIGURATION

7RITE#ONFIGURATION

,%

3$/

#,+

3$)

0REVIOUS$ATA

...

$

$$ .EXT$ATA

$ $ $ $ $ $ $ $ $ $ $ $ $

-3"

$ $ $

,%

#,+

3$)

3$/

...

0REVIOUS$ATA $ $ $

$

$$ .EXT$ATA

$ $ $ $ $ $ $ $ $ $ $ $ $

-3"

,%

#,+

3$/ 0REVIOUS$ATA

... .... ..

&% $ # " !

,%

3$/

#,+

3$)

0REVIOUS$ATA

..

.

.EXT$ATA

& % $ # " !

& % $

Definition of configuration register STP1612PW05

16/35 Doc ID 15819 Rev 4

7 Definition of configuration register

Configuration register

Default value

MSB LSB

FEDCBA9876543210

MSB LSB

FEDCBA9876543210

X 0 1 11 1 8’b10101011 0 0

Table 13. Configuration register

Bit Attribute Definition Value Function

F Read/Write Shift register

length 0 (default) Shift register length 0 = 16-bit,1 = 256-bit

E Read Thermal error

flag

0 (default) Safe (OK)

1 Over temperature (>150 °C typ.)

D Read/Write

PWM counter:

16-bit or 12-bit 0 (default) To set the gray scale mode (PWM):

0 = 12-bit 1 = 16-bit

C

Read/Write PWM counting

mode selection

00 64 times of MSB(1) 6-bit PWM counting plus once

of LSB(1) 6-bit PWM counting

1. Please refer to “setting the PWM counting mode” section.

01 16 times of MSB 6-bit PWM counting by 1/4

PWCLK plus once of LSB 6-bit PWM counting

B 10 4 times of MSB 6-bit PWM counting by 1/16

PWCLK plus once of LSB 6-bit PWM counting

11 (default) PWM counting

A Read/Write

PWM data

synchronization

mode

0 Auto-synchronization

1 (default) Manual synchronization

9~2 Read/Write Current gain

adjustment

00000000

~

11111111

8’b10101011 (default)

1 Read/Write TSD thermal

shutdown

0 (default) Disable

1 Enable (2) the output channel turn OFF

if TTF > 150 °C

2. Please refer to “TSD” thermal error flag and thermal shutdown “section.

0 Read/Write

Time-out alert of

PWCLK

disconnection

0 (default) Enable (3)

3. Please refer to “time-out alert of PWCLK disconnection” section.

1 Disable

STP1612PW05 Grey scales data loading

Doc ID 15819 Rev 4 17/35

8 Grey scales data loading

The STP1612PW05 is able to manage a gray-scale depth of 12 or 16 bits for each output,

exploiting an e-PWM algorithm.

The bit D of the configuration register is used to select the grey-scale loading. Its value can

be set to “0” for 12 bits or “1” for 16 bits. By default, D is set to “0”.

Loading of the data is performed through the serial input on a dedicated buffer and two

different methods can be used.

With both methods, the first incoming data packet is relative to the output 15; the following

packet is relative to the output 14 and so on up to the output 0.

If F=”0”, when a data packet has been loaded, the latch signal (LE) must become active for

one CLK cycle (data latch). When the last data packet, relative to the output 0, has been

loaded, the latch signal must be active for two CLK cycles (global latch) and all the data will

be transferred to the e-PWM registers starting from the MSB.

If F=”1” all data packets (12 or 16 bits x16) are loaded and then the global latch signal must

be active and all the data will be transferred to the e-PWM registers starting from the MSB.

Figure 7. Full timing for data loading

Setting the PWM gray scale counter STP1612PW05

18/35 Doc ID 15819 Rev 4

9 Setting the PWM gray scale counter

STP1612PW05 provides a 12-bit or 16-bit PWM color depth. Each serial data input will be

implemented according to the e-PWM algorithm.

9.1 PWM data synchronization

STP1612PW05 defines the different counting algorithms that support e-PWM, technology,

(scrambled PWM). With e-PWM, the total PWM cycles can be broken down into MSB (most

significant bits) and LSB (least significant bits) of gray scale cycles, and the MSB

information can be dithered across many refresh cycles to achieve overall same high bit

resolution. STP1612PW05 also allows changing different counting algorithms and provides

the best output linearity when there are fewer transitions of output.

Figure 8. 12-bit e-PWM operation example

PWCLK

PWCLK

PWCLK

PWCLK

PWCLK

STP1612PW05 Setting the PWM gray scale counter

Doc ID 15819 Rev 4 19/35

9.2 Synchronization for PWM counting

The data synchronization between the incoming data flow and the output channels is

managed through the bit A within the configuration register.

If the bit A is set to “0” the device performs itself the data synchronization: when all the new

data are loaded with a “global latch”, the device wait until all the PWM counter completes

the counting cycle before updating them with the new data, at the next CLK rising edge.

Conversely, if bit A is set to “1” (default), the data synchronization is not performed by the

device and is managed by the microcontroller, which has to take care of the data and

signals. If this is not done, there might be artefacts on the output image.

Figure 9. Synchronization for PWM counting

Figure 10. Without synchronization for PWM counting

CLK

PWCLK

CLK

PWCLK

Error detection conditions STP1612PW05

20/35 Doc ID 15819 Rev 4

10 Error detection conditions

The STP1612PW05 can detect open channels (OD) and LED short-circuits (SD).

The detection circuitry performs open- and short-circuit detection simultaneously and the

image quality will not be impacted since the test duration is short (0.5 µs typ).

To perform the open-circuit, short-circuit error detection a channel must be on, the

command “enable error detection” starts the detection. After 0.5 µs (typ) the command “read

error status code” allows to get the status from the serial output (SDO).

Note: Where: IO = the output current programmed by the REXT

, IODEC = the detected output

current in detection mode

Figure 11. Detection circuit

Table 14. Detection conditions (VDD = 3.3 to 5 V temp. range -40 to 125 °C)

SW-1 or

SW-3b

Open line or output short to GND

detected ==> IODEC ≤0.5 x IO

SW-2 or

SW-3a

Short on LED or short to V-LED

detected ==> VO≥2.3 V

16

STP1612PW05

This manual suits for next models

4

Table of contents

Other STMicroelectronics Lighting Equipment manuals