Struck SIS3800 User manual

Artisan Technology Group is your source for quality

new and certied-used/pre-owned equipment

• FAST SHIPPING AND

DELIVERY

• TENS OF THOUSANDS OF

IN-STOCK ITEMS

• EQUIPMENT DEMOS

• HUNDREDS OF

MANUFACTURERS

SUPPORTED

• LEASING/MONTHLY

RENTALS

• ITAR CERTIFIED

SECURE ASSET SOLUTIONS

SERVICE CENTER REPAIRS

Experienced engineers and technicians on staff

at our full-service, in-house repair center

WE BUY USED EQUIPMENT

Sell your excess, underutilized, and idle used equipment

We also offer credit for buy-backs and trade-ins

www.artisantg.com/WeBuyEquipment

REMOTE INSPECTION

Remotely inspect equipment before purchasing with

our interactive website at www.instraview.com

LOOKING FOR MORE INFORMATION?

Visit us on the web at www.artisantg.com for more

information on price quotations, drivers, technical

specications, manuals, and documentation

Contact us: (888) 88-SOURCE | sales@artisantg.com | www.artisantg.com

SM

View

Instra

SIS Documentation SIS3800

Scaler/Counter

Page 1 of 39

SIS3800

VME Scaler/Counter

User Manual

SIS GmbH

Harksheider Str.102A

22399 Hamburg

Germany

Phone: ++49 (0) 40 60 87 305 0

Fax: ++49 (0) 40 60 87 305 20

email: [email protected]

http://www.struck.de

Version: 1.21 as of 20.01.04

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

SIS Documentation SIS3800

Scaler/Counter

Page 2 of 39

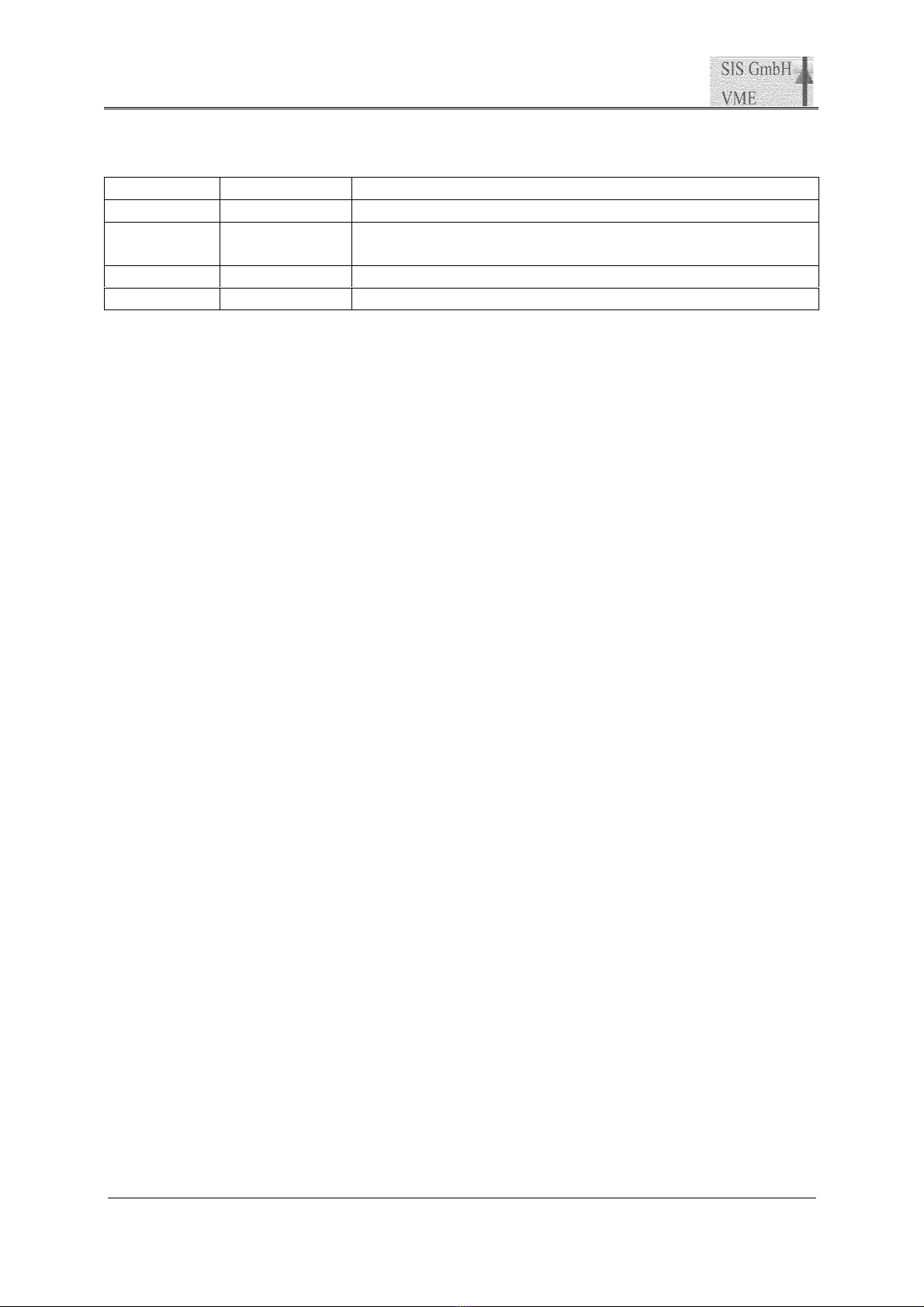

Revision Table:

Revision Date Modification

1.1 18.09.98 Generation

1.13 29.01.99 introduction of revision table

LEMO control/flat cable counter front panel included

1.20 10.11.99 Firmware Version 3.0

1.21 20.01.04 Firmware Version 5.0 bug fix BLT readout

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

SIS Documentation SIS3800

Scaler/Counter

Page 3 of 39

1 Table of contents

1 Table of contents .............................................................................................................................................3

2 Introduction.....................................................................................................................................................5

3 Technical Properties/Features..........................................................................................................................6

3.1 Board Layout...........................................................................................................................................6

3.2 Counter Design and Modus Operandi .....................................................................................................7

3.3 Count Enable Logic.................................................................................................................................8

3.4 Clear Logic..............................................................................................................................................8

4 Getting Started.................................................................................................................................................9

4.1 Factory Default Settings..........................................................................................................................9

4.1.1 Adressing.........................................................................................................................................9

4.1.2 System Reset Behaviour..................................................................................................................9

5 Firmware Selection..........................................................................................................................................9

5.1 Examples ...............................................................................................................................................10

6 Front Panel LEDs ..........................................................................................................................................11

7 VME addressing............................................................................................................................................12

7.1 Address Space .......................................................................................................................................12

7.2 Base Address.........................................................................................................................................12

7.2.1 VME..............................................................................................................................................12

7.2.2 VIPA/VME64x..............................................................................................................................12

7.3 Address Map..........................................................................................................................................13

8 Register Description......................................................................................................................................14

8.1 Status Register (0x0) .............................................................................................................................14

8.2 Control Register (0x0)...........................................................................................................................15

8.3 Module Identification and IRQ control register (0x4)...........................................................................16

8.4 Count disable register 0xC.....................................................................................................................17

8.5 Overflow registers 0x380, 0x3A0, 0x3C0, 0x 3E0................................................................................17

8.6 Broadcast Addressing............................................................................................................................17

9 VME Interrupts..............................................................................................................................................19

10 Data Format...............................................................................................................................................20

10.1 D16........................................................................................................................................................20

10.2 D32........................................................................................................................................................20

11 Readout Schemes.......................................................................................................................................20

11.1 Read Shadow Register...........................................................................................................................20

11.2 Read and Clear all Counters..................................................................................................................20

11.3 Read Counter.........................................................................................................................................20

11.4 Special behaviour of Firmware Version 3.............................................................................................20

12 Input Configuration ...................................................................................................................................21

12.1 ECL .......................................................................................................................................................21

12.2 NIM.......................................................................................................................................................22

12.3 TTL........................................................................................................................................................23

12.3.1 TTL/LEMO ...................................................................................................................................23

12.3.2 TTL/Flat Cable..............................................................................................................................23

13 Connector Specification ............................................................................................................................23

14 Control Input Modes..................................................................................................................................24

14.1 Version 1 ...............................................................................................................................................24

14.2 Version 2 and 3......................................................................................................................................24

15 Signal Specification...................................................................................................................................25

15.1 Control Signals......................................................................................................................................25

15.2 Inputs.....................................................................................................................................................25

16 Operating Conditions.................................................................................................................................25

16.1 Power Consumption/Voltage requirement.............................................................................................25

16.2 Cooling..................................................................................................................................................25

16.3 Insertion/Removal .................................................................................................................................25

17 Test............................................................................................................................................................26

17.1 LED (selftest) ........................................................................................................................................26

17.2 Internal pulser tests................................................................................................................................26

17.2.1 Single Pulse ...................................................................................................................................26

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

SIS Documentation SIS3800

Scaler/Counter

Page 4 of 39

17.2.2 25 MHz Pulser...............................................................................................................................26

17.3 Reference pulser channel 1....................................................................................................................26

17.4 Signal-Input Priority..............................................................................................................................26

18 Software Support.......................................................................................................................................27

18.1 Contents of the included Floppy............................................................................................................27

19 Appendix...................................................................................................................................................28

19.1 Address Modifier Overview..................................................................................................................28

19.2 Front Panel Layout ................................................................................................................................29

19.3 Flat cable Input/Output Pin Assignments..............................................................................................30

19.3.1 ECL................................................................................................................................................30

19.3.2 TTL................................................................................................................................................31

19.4 List of Jumpers......................................................................................................................................32

19.5 Jumper and rotary switch locations .......................................................................................................32

19.5.1 Addressing mode and base address selection ................................................................................32

19.5.2 J500 (Bootfile Selection) and J520 (SYSRESET Behaviour) .......................................................33

19.6 Board Layout.........................................................................................................................................34

19.7 FLASHPROM Versions........................................................................................................................35

19.8 Row d and z Pin Assignments...............................................................................................................36

19.9 Geographical Address Pin Assignments................................................................................................37

19.10 Additional Information on VME .......................................................................................................37

20 Index..........................................................................................................................................................38

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Table of contents

Other Struck Media Converter manuals

Popular Media Converter manuals by other brands

H&B

H&B TX-100 Installation and instruction manual

Bolin Technology

Bolin Technology D Series user manual

IFM Electronic

IFM Electronic Efector 400 RN30 Series Device manual

GRASS VALLEY

GRASS VALLEY KUDOSPRO ULC2000 user manual

Linear Technology

Linear Technology DC1523A Demo Manual

Lika

Lika ROTAPULS I28 Series quick start guide

Weidmuller

Weidmuller IE-MC-VL Series Hardware installation guide

Optical Systems Design

Optical Systems Design OSD2139 Series Operator's manual

Tema Telecomunicazioni

Tema Telecomunicazioni AD615/S product manual

KTI Networks

KTI Networks KGC-352 Series installation guide

Gira

Gira 0588 Series operating instructions

Lika

Lika SFA-5000-FD user guide