TCC720 INTRODUCTION

32-bit RISC Microprocessor for Digital Media Player

Dec. 16. 2002 Preliminary Spec 0.51

1 - 4

1.2 Pin Description

JTAG Interface

Signal Name NUM Type Description

TDI 99 I JTAG serial data input for ARM940T

TMS 100 I JTAG Test mode select for ARM940T

TCK 101 I JTAG test clock for ARM940T

TDO 102 O JTAG serial data output for ARM940T

nTRST 103 I Reset signal for boundary scan logic. Active low.

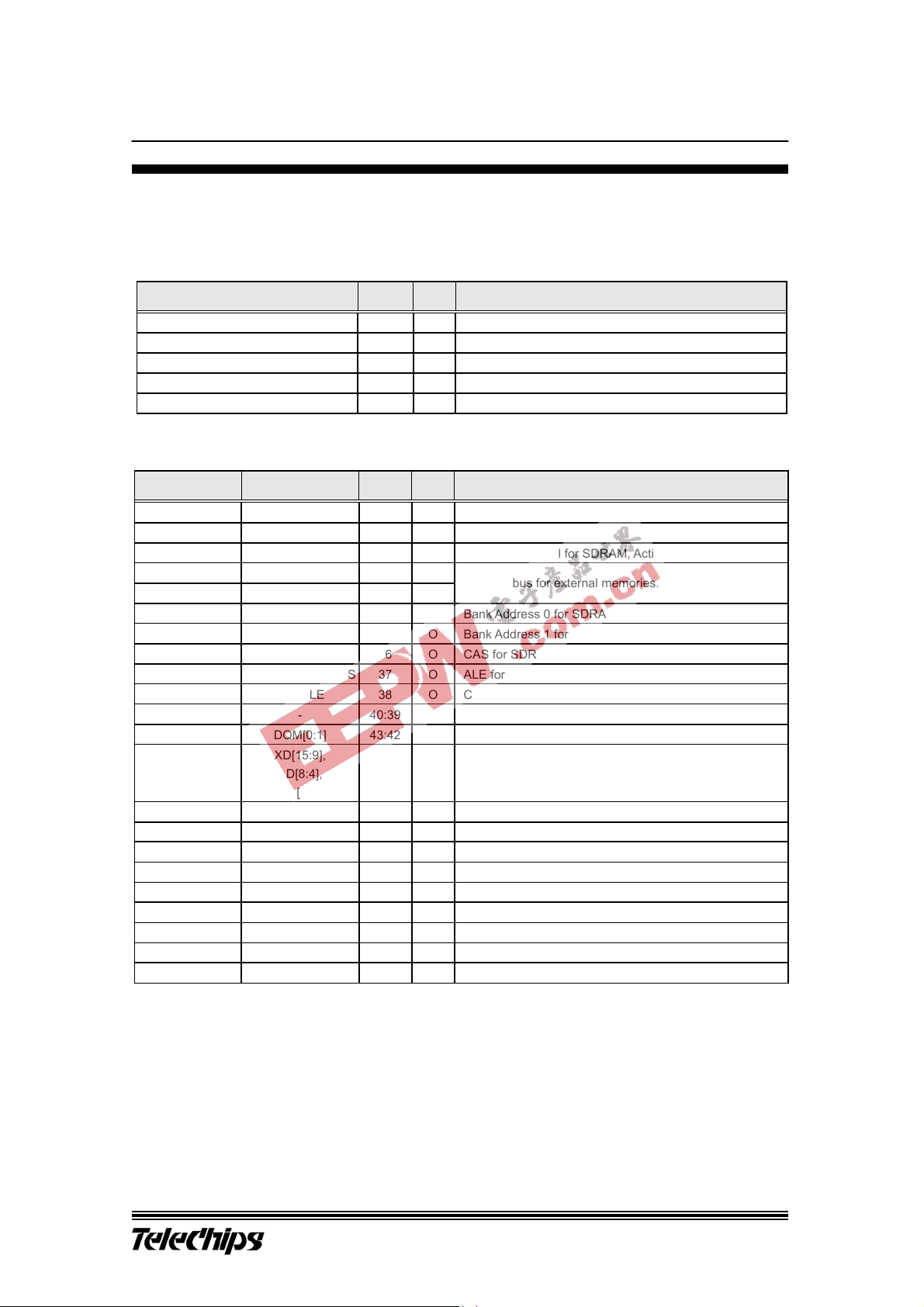

External Memory Interface

Signal Shared Signal NUM Type Description

SD_CKE GPIO_B0 56 O Clock enable signal for SDRAM, Active high. / GPIO_B1

SD_CLK GPO 44 O SDRAM clock

SD_nCS GPIO_B1 46 O Chip select signal for SDRAM, Active low. / GPIO_B0

XA[6:0] - 23:17 O

XA[12:7] - 31:26 O

Address bus for external memories.

XA[13] SD_BA0 34 O Bank Address 0 for SDRAM / XA[13]

XA[14] SD_BA1 35 O Bank Address 1 for SDRAM / XA[14]

XA[15] SD_nCAS 36 O CAS for SDRAM / XA[15]

XA[16] ND_ALE, SD_nRAS 37 O ALE for NAND flash / RAS for SDRAM / XA[16]

XA[17] ND_CLE 38 O CLE for NAND flash / XA[17]

XA[19:18] - 40:39 O XA[19:18] for static memory / Bus Width configuration

XA[21:20] DQM[0:1] 43:42 O XA[21:20] / Data I/O mask

XD[15:9],

XD[8:4],

XD[3:0]

XD[15:9],

XD[8:4],

XD[3:0]

15:9,

6:2,

128:125

I/O Data bus for external memory

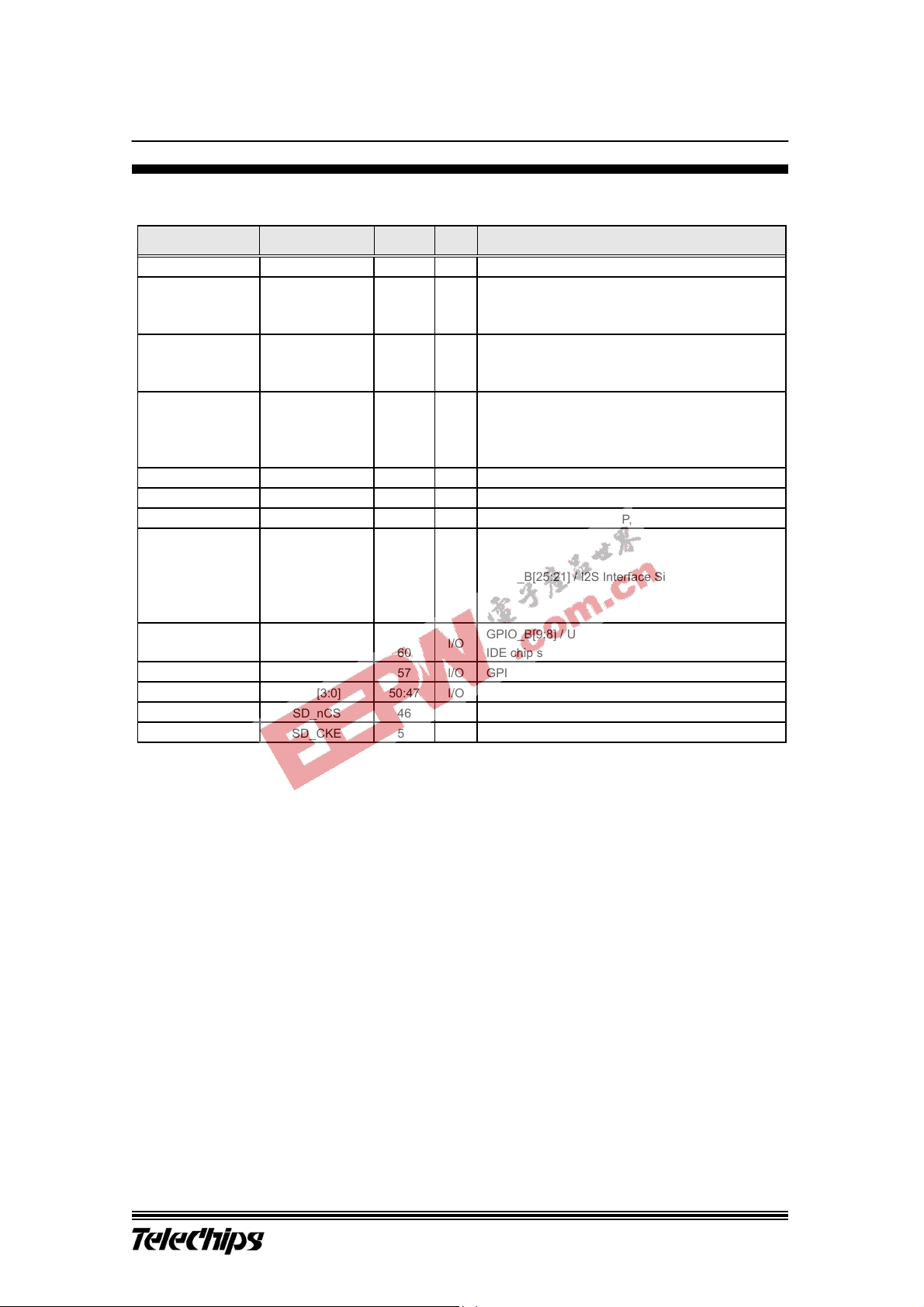

nCS0 / ND_nOE0 GPIO_B2 47 O External chip select 0 / NAND flash 0 OE / GPIO_B2

nCS1 / ND_nOE1 GPIO_B3 48 O External chip select 1 / NAND flash 1 OE / GPIO_B3

nCS2 / ND_nOE2 GPIO_B4 49 O External chip select 2 / NAND flash 2 OE / GPIO_B4

nCS3 / ND_nOE3 GPIO_B5 50 O External chip select 3 / NAND flash 3 OE / GPIO_B5

IDE_nCS1 GPIO_B9 / UT_RX 61 O IDE chip select 1. Active low. / GPIO_B9 / UART RX

ND_nWE GPIO_B7 57 O NAND flash WE. Active low. / GPIO_B7

nWE nWE 58 O Static memory write enable signal. Active low.

nOE nOE 59 O Static memory output enable signal. Active low.

READY - 73 I Ready information from external device.

*) XA[21:0] is used as system address bus for external memories such as SRAM, ROM.

XA[12:0] can be also used as RAS and CAS signals for SDRAM.

XD[15:0] is used as system data bus for all types of external memories contained.

SD_CLK is also used as general purpose output port by setting clock control flag. Refer to the

chapter of memory controller for detail.