5 References............................................................................................................................................................................ 55

6 Revision History................................................................................................................................................................... 55

List of Figures

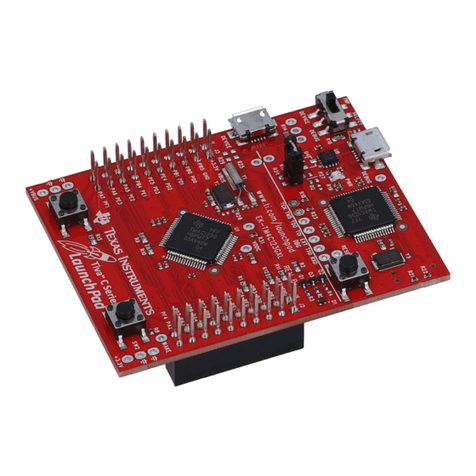

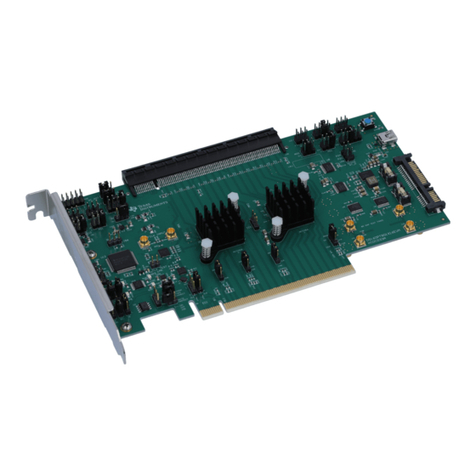

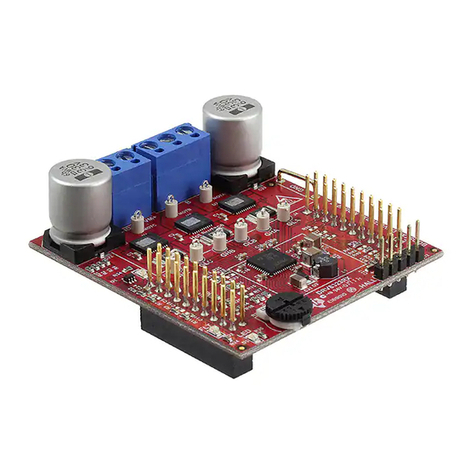

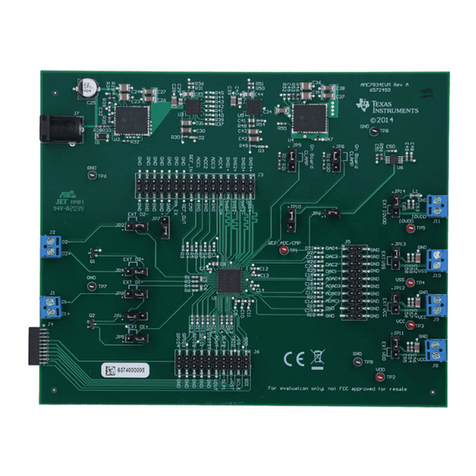

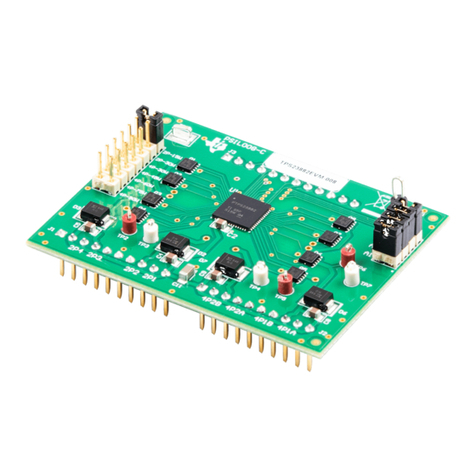

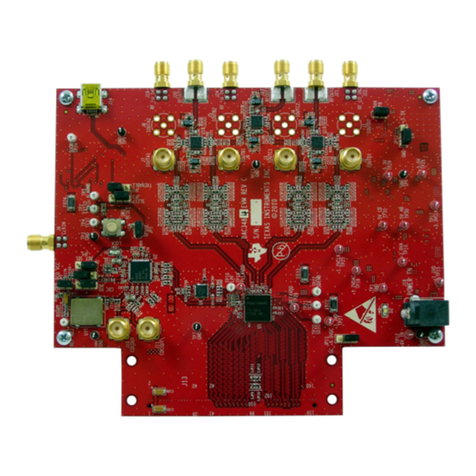

Figure 3-1. Top View of General Processor Board...................................................................................................................... 4

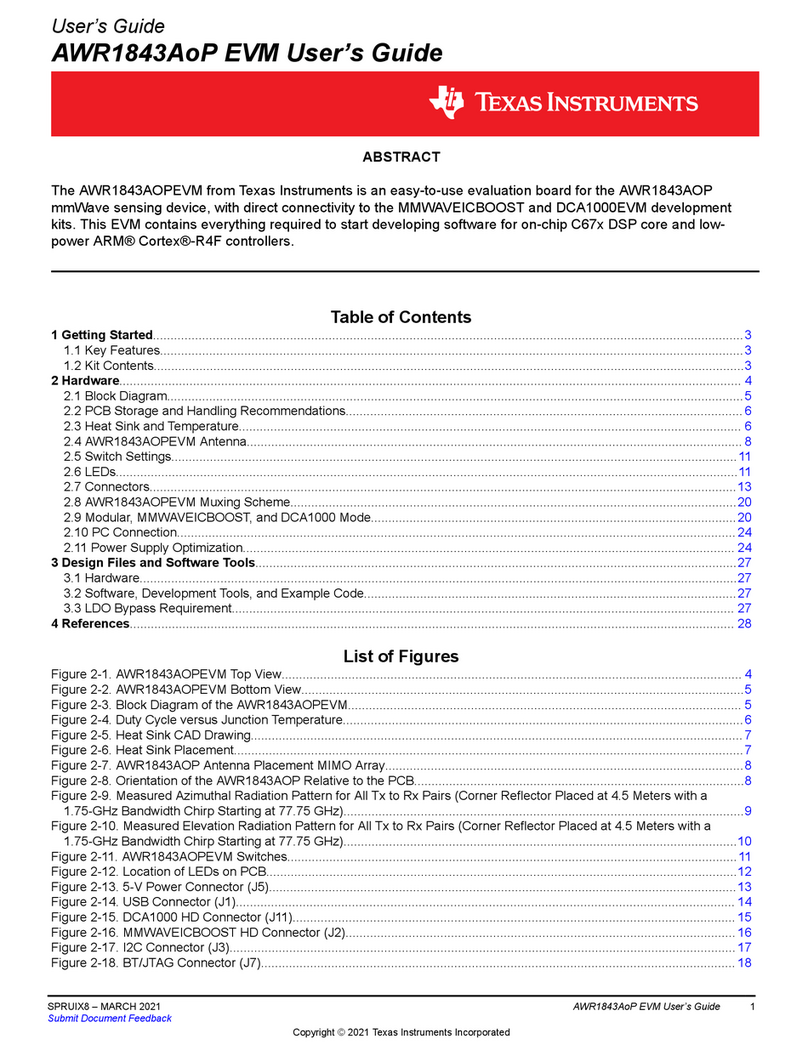

Figure 3-2. Bottom View of General Processor Board.................................................................................................................5

Figure 3-3. General Processor Board Functional Block Diagram................................................................................................7

Figure 3-4. AM64x GP EVM Clock Tree....................................................................................................................................10

Figure 3-5. Overall Reset Architecture of the AM64x EVM........................................................................................................11

Figure 3-6. Power Good LEDs...................................................................................................................................................14

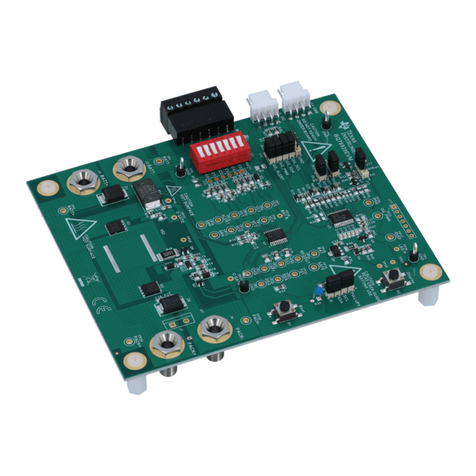

Figure 3-7. Power ON and OFF Sequencing.............................................................................................................................15

Figure 3-8. Core Supply and Array Core Supply Options..........................................................................................................16

Figure 3-9. AM64x GP EVM Schematic Excerpt, Boot Mode Selection Switches (SW2, SW3)................................................18

Figure 3-10. AM64x GP EVP PCB, Boot Mode Selection Switches (SW2, SW3).....................................................................18

Figure 3-11. JTAG Interface.......................................................................................................................................................22

Figure 3-12. Test Automation Header........................................................................................................................................24

Figure 3-13. UART Interface......................................................................................................................................................26

Figure 3-14. DDR4 Interface......................................................................................................................................................27

Figure 3-15. Micro SD Interface.................................................................................................................................................28

Figure 3-16. eMMC Interface.....................................................................................................................................................29

Figure 3-17. OSPI Interface.......................................................................................................................................................30

Figure 3-18. Ethernet Interface - CPSW Domain...................................................................................................................... 31

Figure 3-19. Ethernet Interface - ICSSG Domain...................................................................................................................... 32

Figure 3-20. Ethernet Interface - CPSW Ethernet Strap Settings..............................................................................................36

Figure 3-21. Ethernet Interface - ICSSG1 Ethernet Strap Settings........................................................................................... 37

Figure 3-22. Ethernet Interface - ICSSG2 Ethernet Strap Settings........................................................................................... 38

Figure 3-23. GP Board Ethernet Interface - LEDs..................................................................................................................... 39

Figure 3-24. USB 2.0 Host Interface..........................................................................................................................................41

Figure 3-25. PCIe Interface....................................................................................................................................................... 42

Figure 3-26. High Speed Expansion Connector........................................................................................................................ 45

Figure 3-27. High Speed Expansion Connector Part 1..............................................................................................................46

Figure 3-28. High Speed Expansion Connector Part 2..............................................................................................................47

Figure 3-29. CAN Interface........................................................................................................................................................48

Figure 3-30. I2C Interfaces and Address Assignment to its Peripherals................................................................................... 51

Figure 3-31. FSI Interface..........................................................................................................................................................52

Figure 4-1. AM64x GP EVM Modification Label Location..........................................................................................................53

Figure 4-2. XDS110 CCS Connection Error Dialog................................................................................................................... 54

Figure 4-3. : XDS110 debug reset utility command-line function...............................................................................................54

List of Tables

Table 3-1. Source Clock Selection for the Clock Buffer............................................................................................................. 10

Table 3-2. VMAIN LED...............................................................................................................................................................12

Table 3-3. INA Devices I2C Slave Address............................................................................................................................... 12

Table 3-4. Power Test Points..................................................................................................................................................... 13

Table 3-5. Power LEDs.............................................................................................................................................................. 14

Table 3-6. SoC Power Supply....................................................................................................................................................16

Table 3-7. BOOTMODE Bits...................................................................................................................................................... 19

Table 3-8. PLL Reference Clock Selection BOOTMODE[2:0]................................................................................................... 19

Table 3-9. Boot Device Selection BOOTMODE[6:3]..................................................................................................................19

Table 3-10. Primary Boot Media Configuration BOOTMODE[9:7]............................................................................................. 20

Table 3-11. Backup Boot Mode Selection BOOTMODE[12:10]................................................................................................. 20

Table 3-12. Backup Boot Media Configuration BOOTMODE[13].............................................................................................. 20

Table 3-13. Selection of HSE Connector and JTAG TRACE Functionality................................................................................ 21

Table 3-14. TI20 Pin Connector (J25) Pin-Out...........................................................................................................................21

Table 3-15. TI 60-Pin Connector (J33) Pin-Out......................................................................................................................... 22

Table 3-16. List of Signals Routed to Test Automation Header................................................................................................. 23

Table 3-17. Test Automation Header (J38) Pin-out....................................................................................................................25

Table 3-18. Board ID Memory Header Information.................................................................................................................... 30

Table 3-19. Default Strap Setting of CPSW Ethernet PHY........................................................................................................ 34

Table 3-20. Default Strap Setting of ICSSG Ethernet PHYs......................................................................................................34

Table 3-21. Display Connector (J36) Pin-Out............................................................................................................................ 40

Table 3-22. PCIe Jumper Options to Enable Root Complex and Endpoint Mode..................................................................... 42

Table of Contents www.ti.com

2AM64x GP EVM User's Guide SPRUIX0B – FEBRUARY 2021 – REVISED MARCH 2021

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated