1

SPRUII5A–December 2017–Revised November 2018

Submit Documentation Feedback Copyright © 2017–2018, Texas Instruments Incorporated

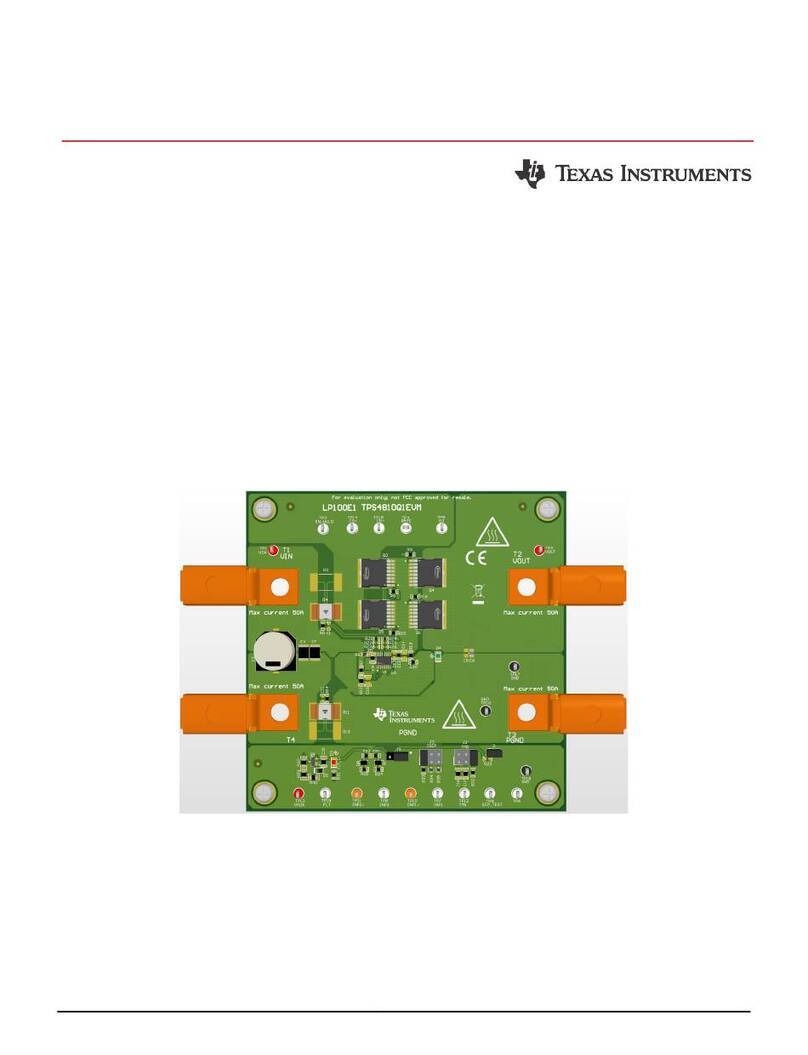

DRA77xP/DRA76xP-ACD CPU EVM Board

User's Guide

SPRUII5A–December 2017–Revised November 2018

DRA77xP/DRA76xP-ACD CPU EVM Board

This user's guide is intended for software and hardware engineers developing applications for the Jacinto

6 high performance, multimedia application processor based on enhanced OMAP™ architecture

implemented with 28-nm technology. It describes the evaluation module (EVM) CPU board’s hardware,

firmware and software functions supplied by Texas Instruments Inc.

Contents

1 Introduction ................................................................................................................... 2

2 Overview...................................................................................................................... 2

3 Hardware...................................................................................................................... 8

4 Signal Multiplex Logic...................................................................................................... 23

5 Application Boards ......................................................................................................... 33

6 USB3 Supported Configurations ......................................................................................... 34

7 References.................................................................................................................. 37

List of Figures

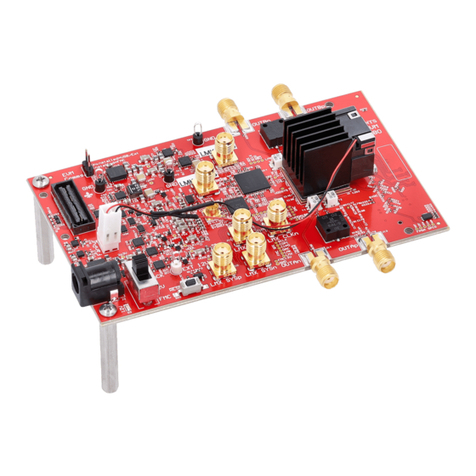

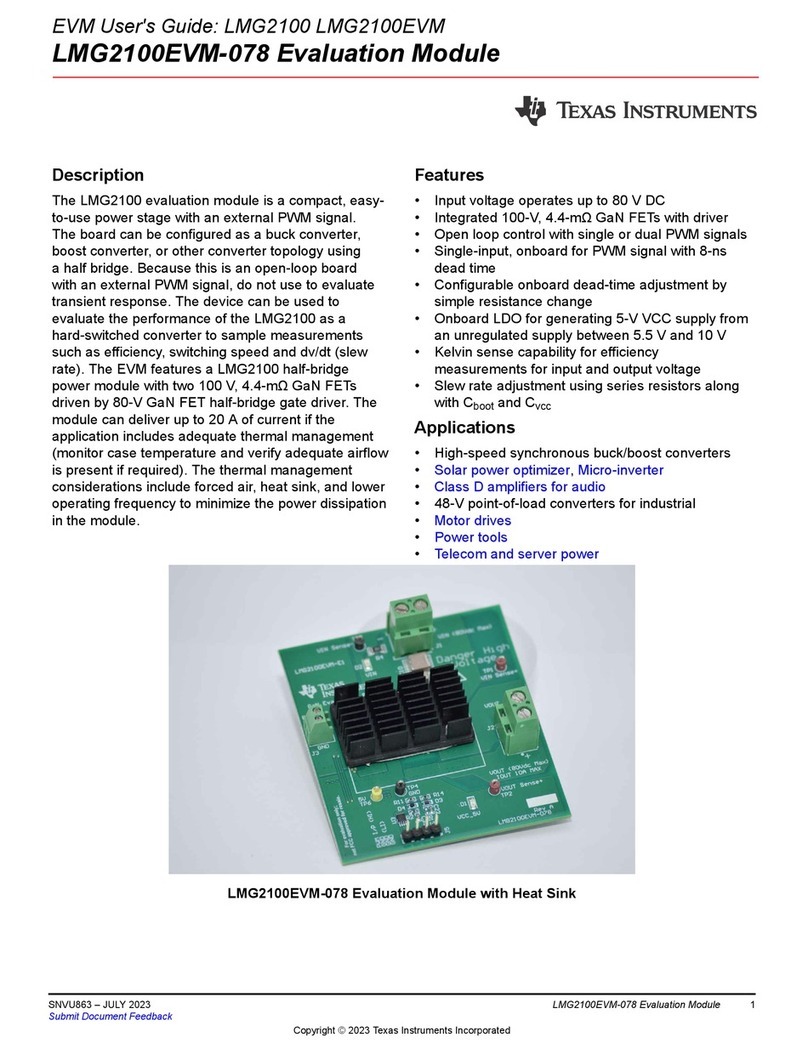

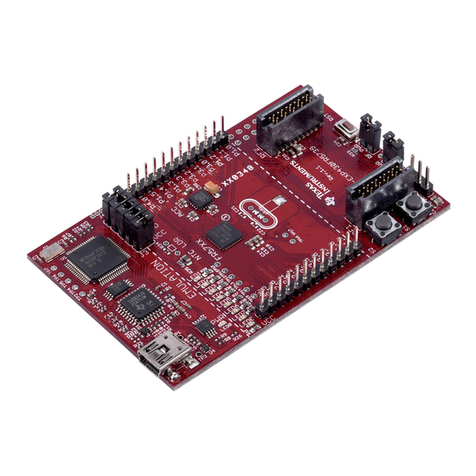

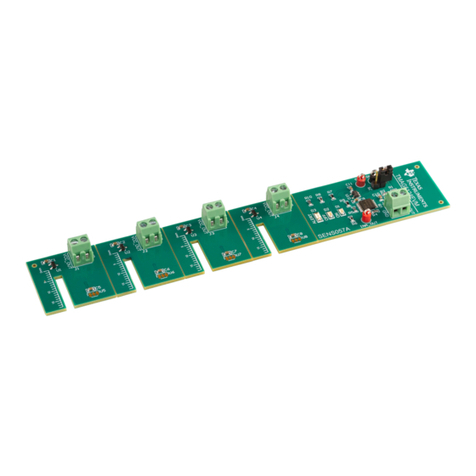

1 CPU Board ................................................................................................................... 3

2 CPU Board - Front........................................................................................................... 6

3 CPU Board - Back........................................................................................................... 7

4 CPU Board Block Diagram................................................................................................. 8

5 Power Distribution Block Diagram......................................................................................... 9

6 Reset Structure............................................................................................................. 10

7 Mux Diagram for GPMC/QSPI............................................................................................ 24

8 Mux Diagram for GPMC/VOUT3......................................................................................... 26

9 Mux Diagram for GPMC/EMMC.......................................................................................... 26

10 Mux Diagram for VIN2A................................................................................................... 27

11 Mux Diagram for VIN2A/RGMII1......................................................................................... 28

12 Mux Diagram for McASP3/7.............................................................................................. 29

13 Mux Diagram for RGMII0/VIN1B......................................................................................... 30

14 Mux Diagram for SPI2/UART3 ........................................................................................... 31

15 Mux Diagram for DCAN2/I2C............................................................................................. 32

16 Mux Diagram for I2C/DDC................................................................................................ 33

17 RGB-to-HDMI Application Bd............................................................................................. 34

List of Tables

1 SoC EVMs/Kits............................................................................................................... 4

2 EVM Accessories............................................................................................................ 4

3 EVM Kit Truth Table......................................................................................................... 4

4 Compatible Wall Supplies (12 V, 5A, 65W)............................................................................. 10

5 Reset Signals Structure ................................................................................................... 11

6 SoC Boot Mode Switch Settings ......................................................................................... 13

7 Board Controls for Booting Options...................................................................................... 13

8 User LEDs................................................................................................................... 17

9 User Switches .............................................................................................................. 17