Users Guide

August 2011

Revision 0.4 – preliminary Page 1 of 31

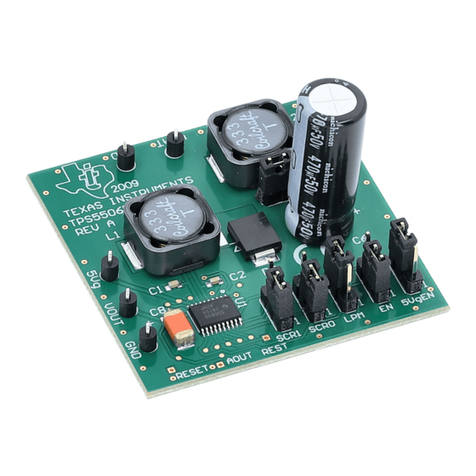

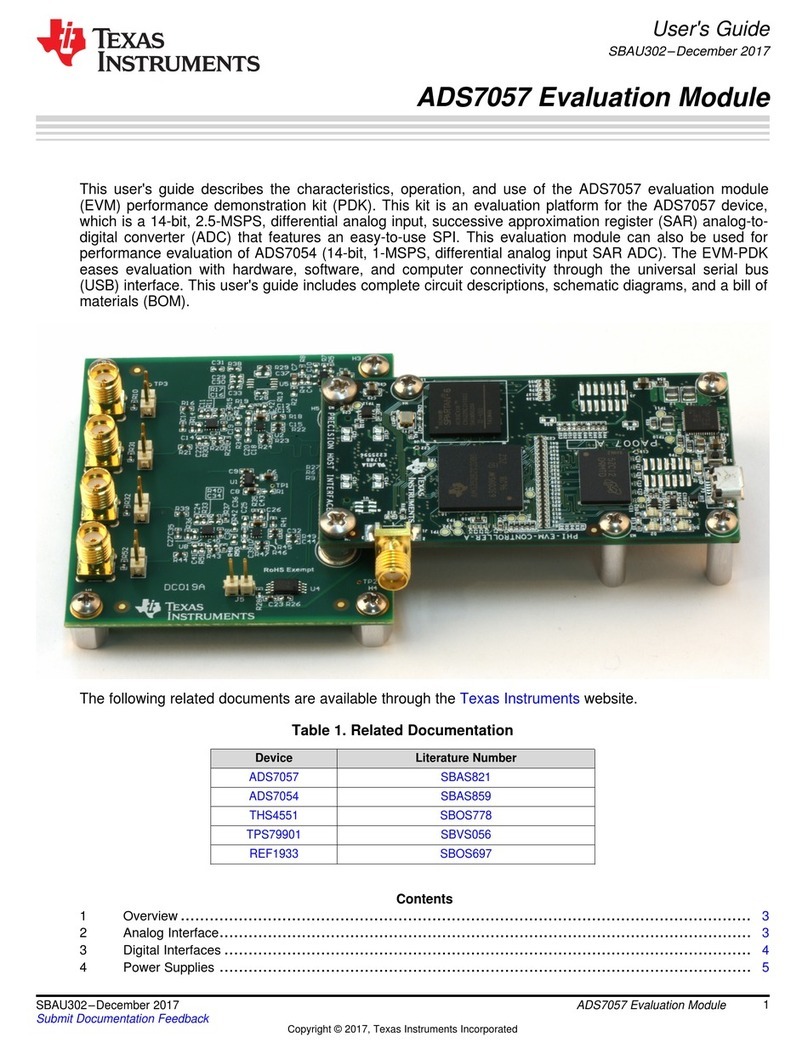

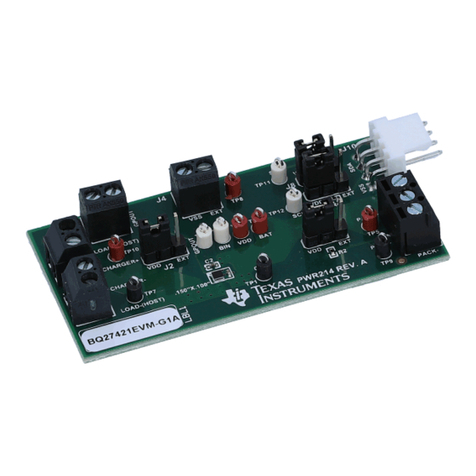

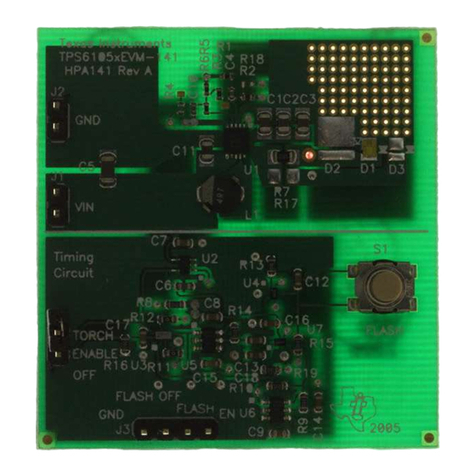

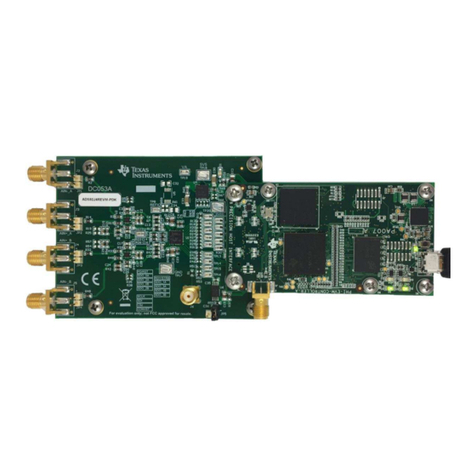

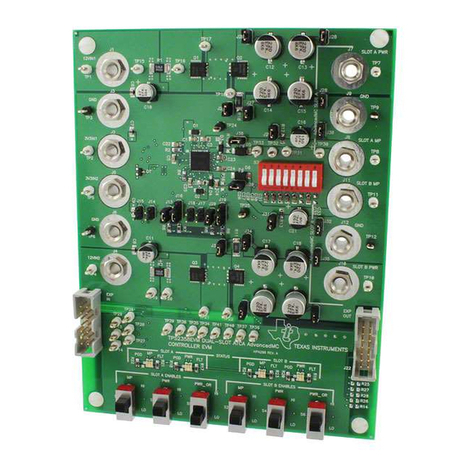

Texas Instruments Dual EVM BoC Card

- Quick Start Guide

High Density Multiprocessor DSP’s

Abstract

This document is provided as a quick start guide for using the Texas Instruments BoC

(Break out Card). The breakout card is intended to provide communication support between

Texas Instruments EVM’s which contain an AMC B+ interface. The EVM BoC is intended

to support EVM to EVM communication for SRIO, PCIe, SGMII, and AIF.

Table of Contents

Abstract...........................................................................................................................................................................1

Table of Contents ...........................................................................................................................................................1

Table of Figures..............................................................................................................................................................2

Table of Tables...............................................................................................................................................................2

I. OVERVIEW...........................................................................................................................................................3

I. Introduction......................................................................................................................................................3

II. Hardware Description......................................................................................................................................3

II. Hardware Configuration.......................................................................................................................................6

I. Initial Installation Procedure...........................................................................................................................6

II. Default Jumper and Pin Settings......................................................................................................................6

III. BoC Logic Power Source Selection [20]..........................................................................................................6

IV. EVM Power Source [16, 17, 18]......................................................................................................................7

V. Emulation Interface [1]....................................................................................................................................8

VI. SGMII Interface ...............................................................................................................................................8

VII. PCIE Interface .................................................................................................................................................8

VIII. SRIO (Serial RapidIO) Interface......................................................................................................................9

IX. AIF (Antenna Interface) Interface....................................................................................................................9

X. I2C interface [5, 9, 11, 23]...............................................................................................................................9

XI. Common REFCLK Source .............................................................................................................................10

a. REFCLK Oscillator Enable Header [19].......................................................................................................10

b. REFCLK Signal Levels...................................................................................................................................10

XII. Timer0 Output Headers [12, 22]....................................................................................................................12

XIII. Timer0 Input Header [10, 24]........................................................................................................................12

XIV. Common RP1CLK Source..............................................................................................................................12

a. RP1CLK Oscillator Enable Header [8].........................................................................................................12

b. RP1CLK Signal Levels...................................................................................................................................13

c. Alternate RP1CLK Inputs [15].......................................................................................................................14

XV. Common TCLK_B Source..............................................................................................................................14

a. TCLK_B Oscillator Enable Header [14] .......................................................................................................14

b. TCLK_B Signal Outputs [2, 13].....................................................................................................................15

c. TCLK_A Signal Outputs [2, 13].....................................................................................................................16

XVI. Common PCIeREFCLK Source [25] .............................................................................................................17