Technical Reference Manual TMDXEVM6657L

SPRUHG7 - Revised August 2012 TMDXEVM6657LE

Page 9 / 90

List of Figures

FIGURE 1.1: BLOCK DIAGRAM OF TMDXEVM6657L.............................................................................................................12

FIGURE 1.2: BLOCK DIAGRAM OF TMDXEVM6657LE..........................................................................................................13

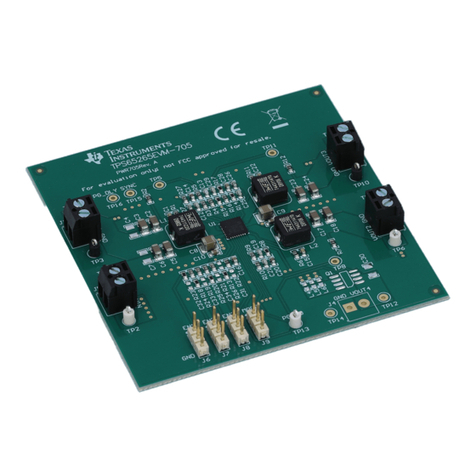

FIGURE 1.3: TMDXEVM6657L ..............................................................................................................................................14

FIGURE 1.4: TMDXEVM6657LE............................................................................................................................................15

FIGURE 2.1: EVM BOARD REVISION .......................................................................................................................................23

FIGURE 2.2: TMDXEVM6657L JTAG EMULATION................................................................................................................24

FIGURE 2.3: TMDXEVM6657LE JTAG EMULATION.............................................................................................................25

FIGURE 2.3: C6657 LITE EVM CLOCK DOMAINS....................................................................................................................27

FIGURE 2.4: C6657 LITE EVM CLOCK DOMAINS....................................................................................................................28

FIGURE 2.5: C6657 LITE EVM FPGA CONNECTIONS............................................................................................................29

FIGURE 2.6: C6657 LITE EVM ETHERNET PHY ROUTING.....................................................................................................30

FIGURE 2.7: C6657 LITE EVM SRIO PORT CONNECTIONS ..................................................................................................31

FIGURE 2.8: C6657 LITE EVM DDR3 INTERFACE .................................................................................................................31

FIGURE 2.9: C6657 LITE EVM EMIF16 INTERFACE ..............................................................................................................32

FIGURE 2.10: C6657 LITE EVM HYPERLINK INTERFACE.......................................................................................................33

FIGURE 2.11: C6657 LITE EVM PCIE INTERFACE .................................................................................................................33

FIGURE 2.12: C6657 LITE EVM MCBSP INTERFACE ............................................................................................................34

FIGURE 2.13: C6657 LITE EVM MCBSP CLOCK GENERATION BY FPGA............................................................................34

FIGURE 2.14: C6657 LITE EVM UART CONNECTIONS .........................................................................................................35

FIGURE 2.15: C6657 LITE EVM MMC CONNECTIONS FOR IPMI..........................................................................................36

FIGURE 3.1: C6657 LITE EVM BOARD ASSEMBLY LAYOUT –TOP VIEW..............................................................................37

FIGURE 3.2: C6657 LITE EVM BOARD LAYOUT –BOTTOM VIEW...........................................................................................38

FIGURE 3.3: COM_SEL1 JUMPER SETTINGS.........................................................................................................................41

FIGURE 3.4: HYPERLINK CONNECTOR ....................................................................................................................................43

FIGURE 3.5: SW3 DEFAULT SETTINGS.....................................................................................................................................48

FIGURE 3.6: SW5 DEFAULT SETTINGS.....................................................................................................................................49

FIGURE 3.7: BOARD TEST POINTS (TOP)................................................................................................................................50

FIGURE 3.8: BOARD TEST POINTS (BOTTOM).........................................................................................................................50

FIGURE 3.9: BOARD LEDS.......................................................................................................................................................52

FIGURE 3.10: TMDXEVM6657LE BOARD ADDITIONAL LEDS..............................................................................................52

FIGURE 4.1: C6657 LITE EVM POWER CONSUMPTION .........................................................................................................55

FIGURE 4.2: C6657 LITE EVM POWER GENERATION TOPOLOGY.........................................................................................56

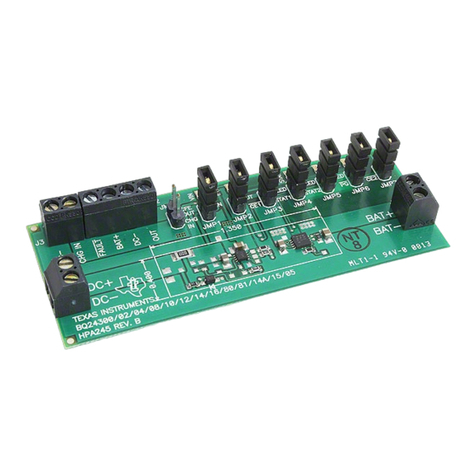

FIGURE 4.3: CVDD AND VCC1V0 DESIGN ON C6657 LITE EVM.........................................................................................57

FIGURE 4.4: VCC3V3_AUX DESIGN ON C6657 LITE EVM..................................................................................................58

FIGURE 4.5: VCC1V5 POWER DESIGN ON C6657 LITE EVM...............................................................................................58

FIGURE 4.6: VCC5 POWER DESIGN ON C6657 LITE EVM....................................................................................................59

FIGURE 4.7: INITIAL POWER UP SEQUENCE TIMING DIAGRAM...............................................................................................61

FIGURE 4.8: POWER DOWN SEQUENCE TIMING DIAGRAM .....................................................................................................62

FIGURE 5.1: POWER-ON RESET BOOT CONFIGURATION TIMING...........................................................................................70

FIGURE 5.2: RESET-FULL SWITCH/TRIGGER BOOT CONFIGURATION TIMING........................................................................70

FIGURE 5.3: SPI ACCESS FROM TMS320C6657 TO FPGA (WRITE /HIGH LEVEL)............................................................73

FIGURE 5.4: SPI ACCESS FROM TMS320C6657 TO FPGA (WRITE)..................................................................................73

FIGURE 5.5: SPI ACCESS FROM TMS320C6657 TO FPGA (READ /HIGH LEVEL)..............................................................73

FIGURE 5.6: SPI ACCESS FROM TMS320C6657 TO FPGA (READ)....................................................................................74

FIGURE 5.7: SPI ACCESS FROM FPGA TO CDCE62005 (WRITE)......................................................................................74

FIGURE 5.8: SPI ACCESS FROM FPGA TO CDCE62005 (READ)........................................................................................74