User’s Guide

LP876242-Q1 Evaluation Module

ABSTRACT

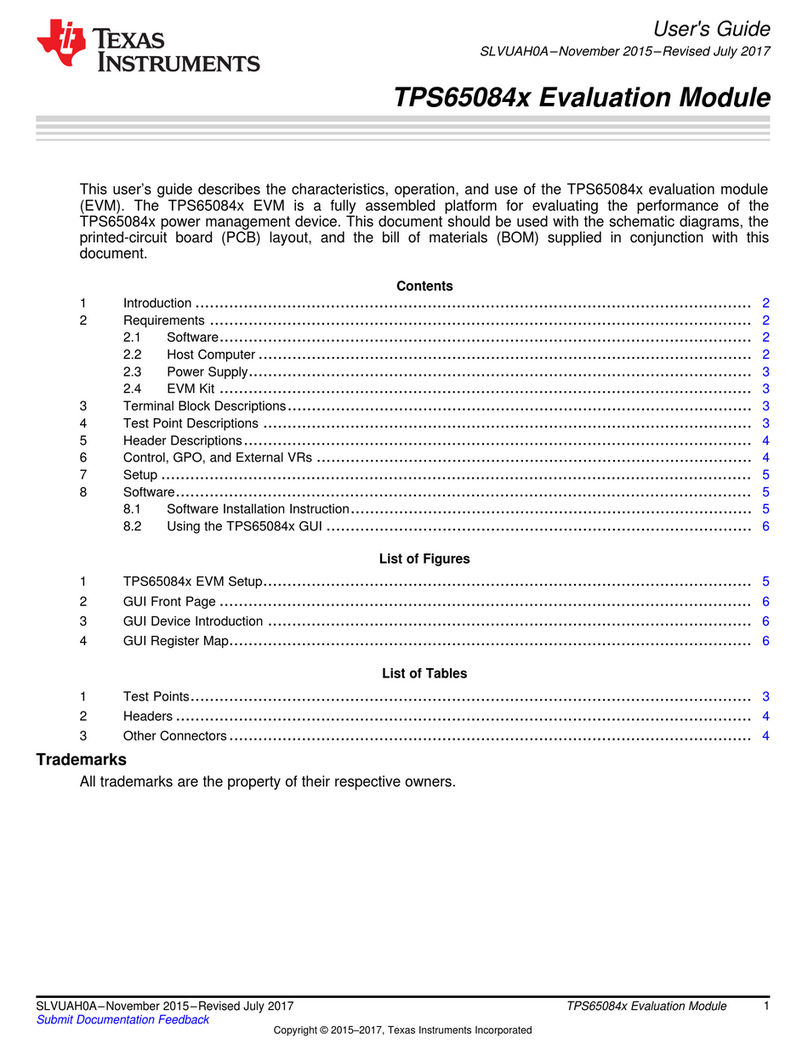

The LP876242-Q1 Evaluation Module (EVM) highlights the performance and flexibility of the LP876242-Q1

power management integrated circuit (PMIC) for xWR radar applications. Use this document in conjunction with

the Scalable PMIC's GUI User's Guide SLVUBT8 and the LP876242-Q1 Four 8.8-MHz Buck Converters for

AWR and IWR MMICs SNVSC07.

Caution Caution Hot surface.

Contact may cause burns.

Do not touch!

Table of Contents

1 Introduction.............................................................................................................................................................................3

2 Getting Started........................................................................................................................................................................3

2.1 The GUI Tool...................................................................................................................................................................... 4

3 EVM Details............................................................................................................................................................................. 4

3.1 Terminal Blocks.................................................................................................................................................................. 4

3.2 Test Point Descriptions.......................................................................................................................................................4

3.3 Configuration Headers....................................................................................................................................................... 4

3.4 Connectors.........................................................................................................................................................................6

3.5 DIP Switches......................................................................................................................................................................7

3.6 EVM Control and GPIO......................................................................................................................................................8

4 Customization......................................................................................................................................................................... 9

4.1 Changing the Communication Interface.............................................................................................................................9

5 Schematic, Layout, and Bill of Materials............................................................................................................................ 10

6 Additional Resources...........................................................................................................................................................23

7 Revision History................................................................................................................................................................... 23

List of Figures

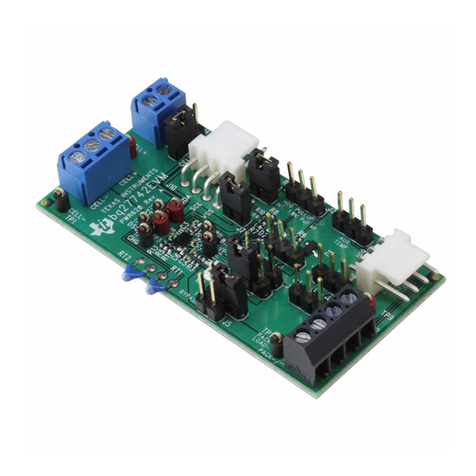

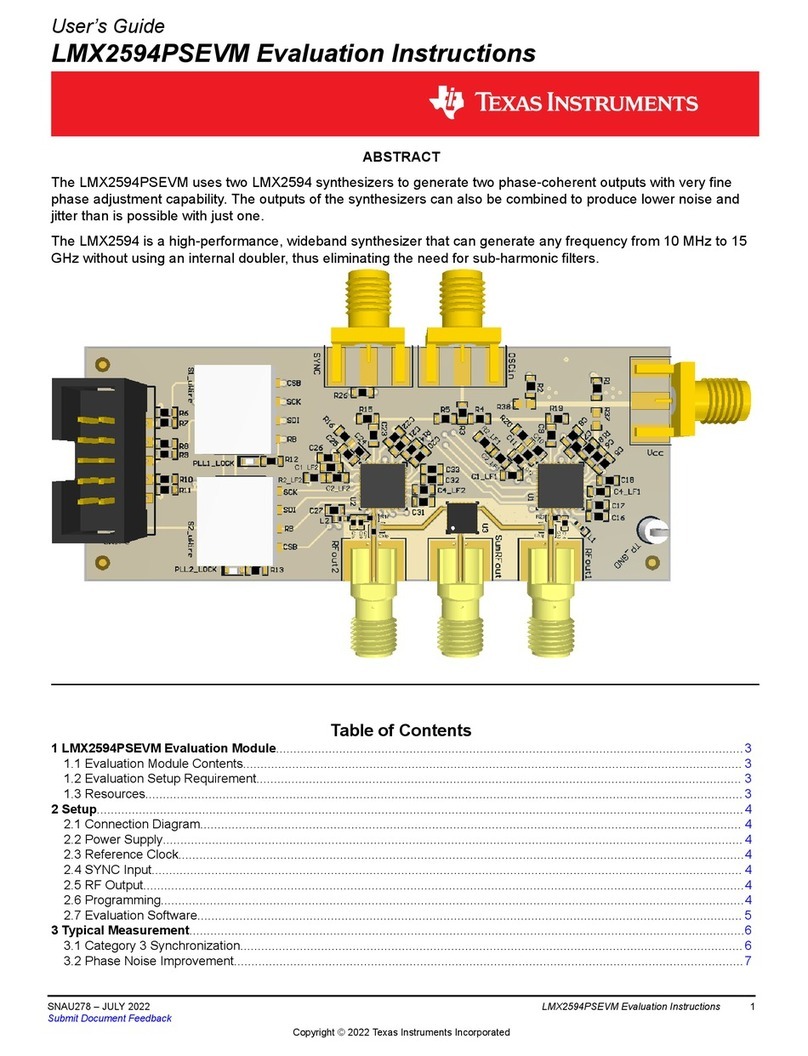

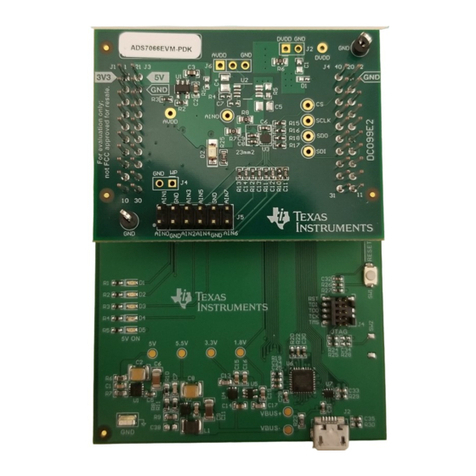

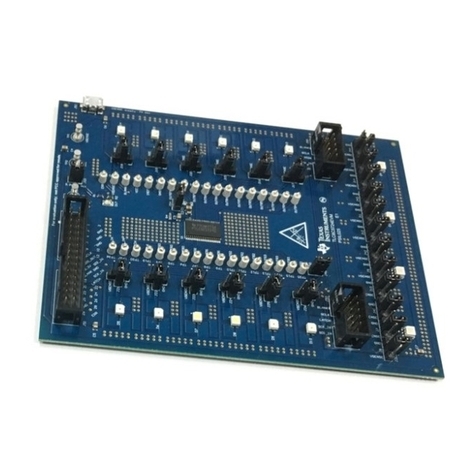

Figure 2-1. EVM Top View........................................................................................................................................................... 3

Figure 3-1. EVM Header J18....................................................................................................................................................... 5

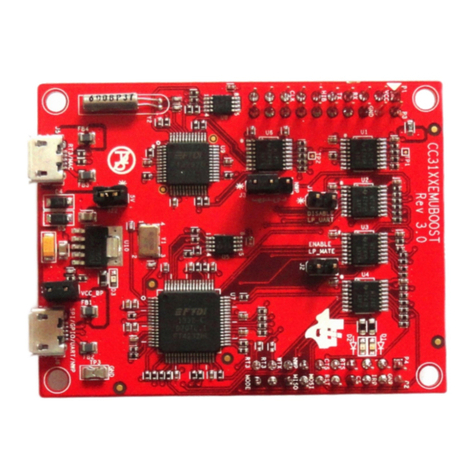

Figure 3-2. EVM Bottom Side...................................................................................................................................................... 7

Figure 4-1. Interface Settings for I2C Communication................................................................................................................. 9

Figure 5-1. Main Schematic Page............................................................................................................................................. 10

Figure 5-2. MCU Schematic Page............................................................................................................................................. 11

Figure 5-3. Layout Top, Layer 1.................................................................................................................................................12

Figure 5-4. Layout Ground, Layer 2...........................................................................................................................................13

Figure 5-5. Layout Signal, Layer 3.............................................................................................................................................14

Figure 5-6. Layout Signal, Layer 4.............................................................................................................................................15

Figure 5-7. Layout Ground, Layer 5...........................................................................................................................................16

Figure 5-8. Layout Bottom, Layer 6........................................................................................................................................... 17

List of Tables

Table 3-1. Terminal Blocks...........................................................................................................................................................4

Table 3-2. Test Point Descriptions............................................................................................................................................... 4

Table 3-3. Header J18 Description.............................................................................................................................................. 5

Table 3-4. Header J33 VIO Voltage Select.................................................................................................................................. 6

Table 3-5. Header J24, 3.3V/5V, GPIO2/I2C/SPI.........................................................................................................................6

Table 3-6. DC Block..................................................................................................................................................................... 7

Table 3-7. DIP Switches...............................................................................................................................................................8

www.ti.com Table of Contents

SLVUC20A – MARCH 2021 – REVISED AUGUST 2022

Submit Document Feedback

LP876242-Q1 Evaluation Module 1

Copyright © 2022 Texas Instruments Incorporated