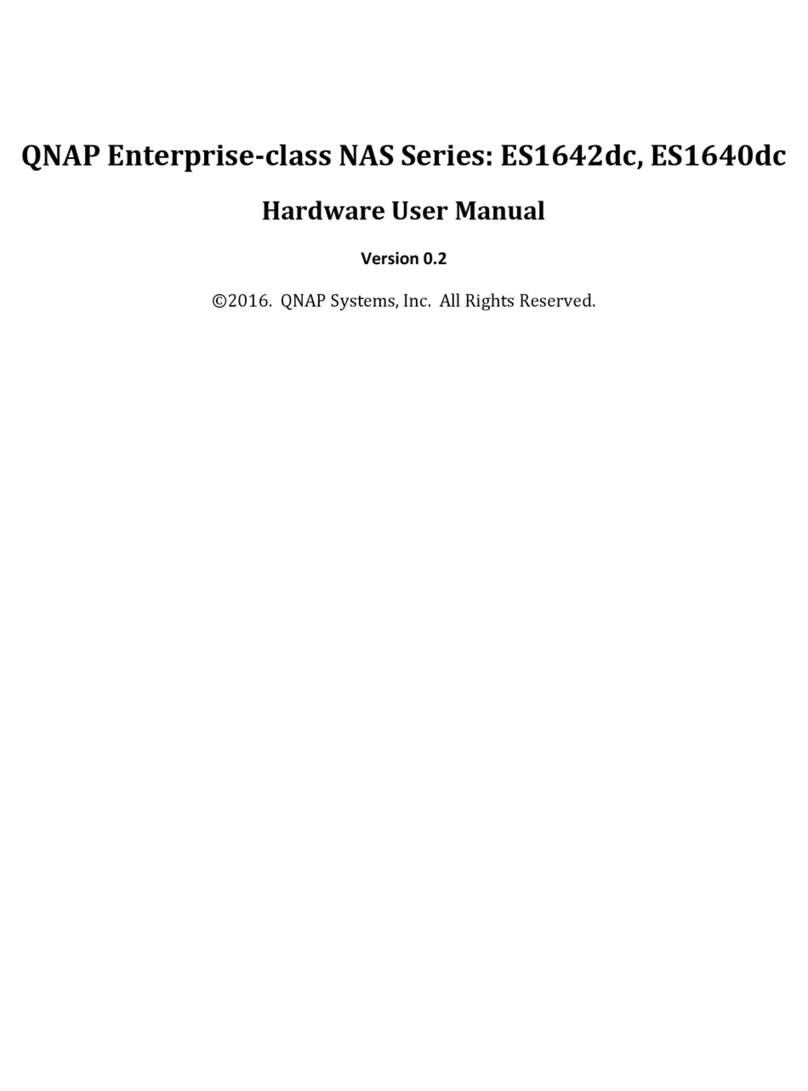

TI Confidential – NDA Restrictions

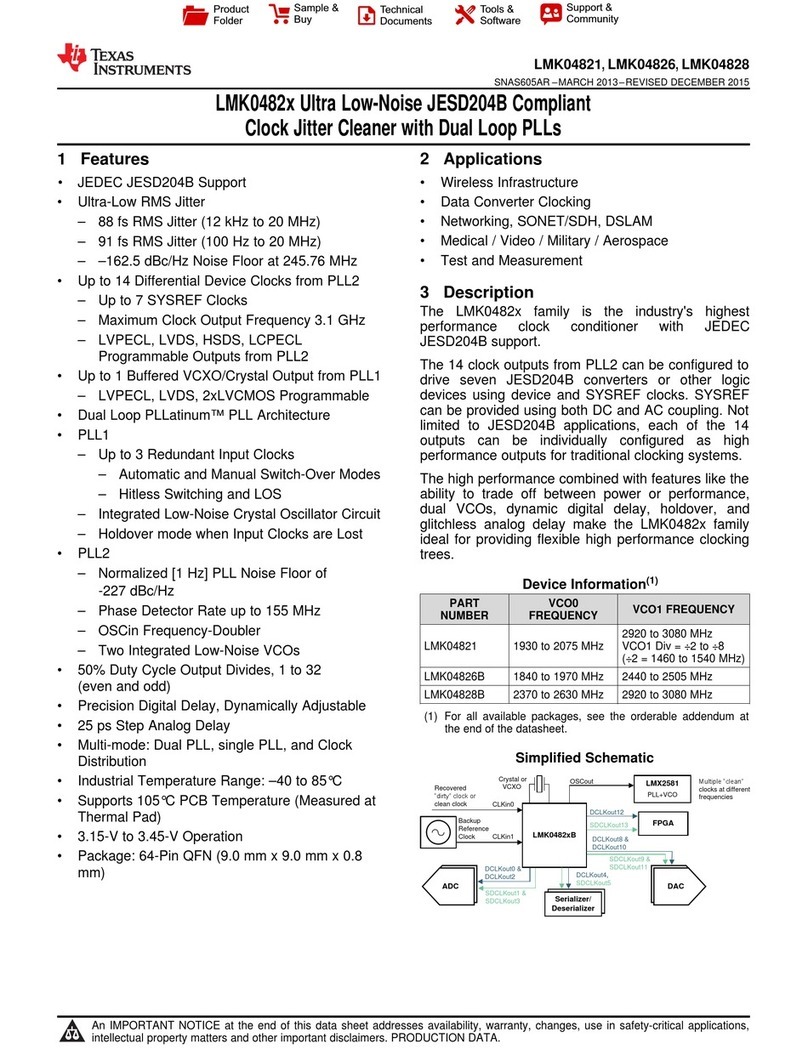

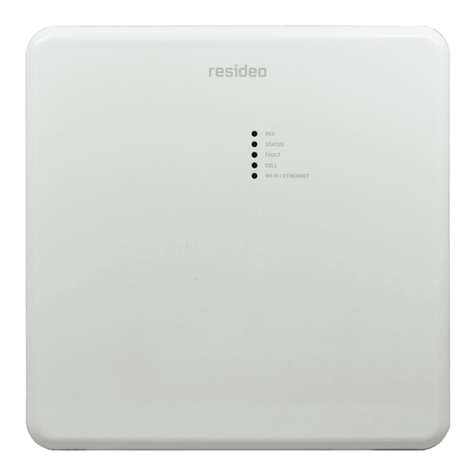

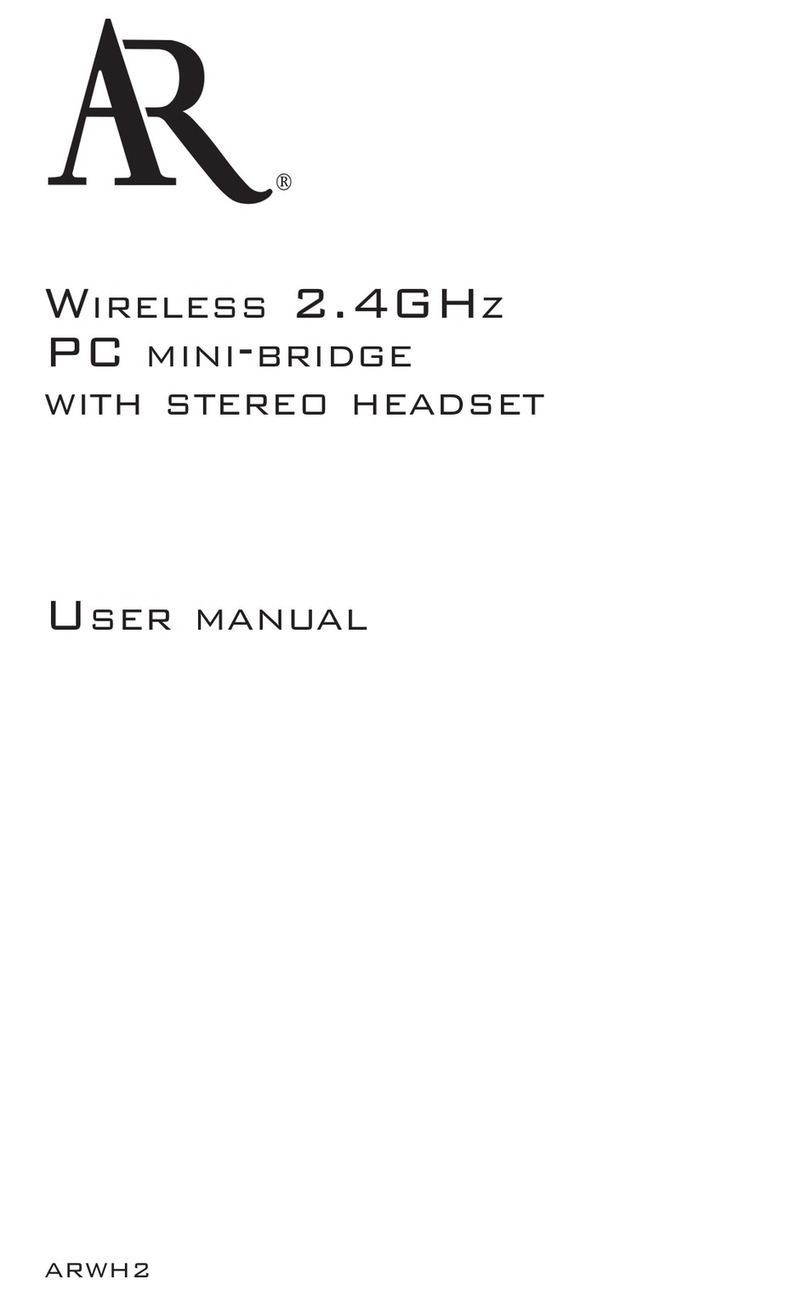

APLL2

APLL1

I2C/SPI

LOGIC I/Os

STATUS

DPLL

÷R

XO/

TCXO/

OCXO

VDD

3.3 V

VDDO

1.8 / 2.5 / 3.3 V

Registers EEPROM,

ROM

Device Control

and Status

Power Conditioning

LMK05318

Ultra-Low Jitter

Network Synchronizer Clock

Hitless

Switching

Differential

or LVCMOS

Differential

or HCSL

DCO

PRIREF

SECREF VCO1

VCO2

OUT0

OUT1

OUT5

÷OD

OUT4÷OD

OUT2

OUT3

OUT7÷OD

OUT6

÷OD

×1, ×2

÷

÷

÷

Output

Muxes

Differential,

HCSL, or

1.8-V LVCMOS

÷

÷OD

÷OD

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. ADVANCE INFORMATION for pre-production products; subject to

change without notice.

LMK05318B

SNAS801 –OCTOBER 2019

LMK05318B Ultra-Low Jitter Network Synchronizer Clock With Two Frequency Domains

1

1 Features

1• One Digital Phase-Locked Loop (DPLL) With:

– Hitless Switching: ±50-ps Phase Transient

– Programmable Loop Bandwidth With Fastlock

– Standards-Compliant Synchronization and

Holdover Using a Low-Cost TCXO/OCXO

• Two Analog Phase-Locked Loops (APLLs) With

Industry-Leading Jitter Performance:

– 50-fs RMS Jitter at 312.5 MHz (APLL1)

– 125-fs RMS Jitter at 155.52 MHz (APLL2)

• Two Reference Clock Inputs

– Priority-Based Input Selection

– Digital Holdover on Loss of Reference

• Eight Clock Outputs With Programmable Drivers

– Up to Six Different Output Frequencies

– AC-LVDS, AC-CML, AC-LVPECL, HCSL, and

1.8-V LVCMOS Output Formats

• EEPROM / ROM for Custom Clocks on Power-Up

• Flexible Configuration Options

– 1 Hz (1 PPS) to 800 MHz on Input and Output

– XO/TCXO/OCXO Input: 10 to 100 MHz

– DCO Mode: < 0.001 ppb/Step for Precise

Clock Steering (IEEE 1588 PTP Slave)

– Advanced Clock Monitoring and Status

– I2C or SPI Interface

• PSNR: –83 dBc (50-mVpp Noise on 3.3-V Supply)

• 3.3-V Supply With 1.8-V, 2.5-V, or 3.3-V Outputs

• Industrial Temperature Range: –40°C to +85°C

2 Applications

• SyncE (G.8262), SONET/SDH (Stratum 3/3E,

G.813, GR-1244, GR-253), IEEE 1588 PTP Slave

Clock, or Optical Transport Network (G.709)

• 400G Line Cards, Fabric Cards for Ethernet

Switches and Routers

• Wireless Base Station (BTS), Wireless Backhaul

• Test and Measurement, Medical Imaging

• Jitter Cleaning, Wander Attenuation, and

Reference Clock Generation for 56G/112G PAM-4

PHYs, ASICs, FPGAs, SoCs, and Processors

3 Description

The LMK05318B is a high-performance network

synchronizer clock device that provides jitter cleaning,

clock generation, advanced clock monitoring, and

superior hitless switching performance to meet the

stringent timing requirements of communications

infrastructure and industrial applications. The ultra-

low jitter and high power supply noise rejection

(PSNR) of the device can reduce bit error rates

(BER) in high-speed serial links.

The device can generate output clocks with 50-fs

RMS jitter using TI's proprietary Bulk Acoustic Wave

(BAW) VCO technology, independent of the jitter and

frequency of the XO and reference inputs.

Device Information(1)

PART NUMBER PACKAGE BODY SIZE (NOM)

LMK05318B VQFN (48) 7.00 mm × 7.00 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Simplified Block Diagram