Topway LMT056DIDFWD-AEN User manual

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

1

of

32

LMT056DIDFWD-AEN

LCD Module User Manual

Prepared by:

Lu jianhui

Checked by: Approved by:

Date

:

201

8

-

0

2

-

07

Date

:

Date

:

Rev.

Descriptions

Release Date

0.1 Preliminary 2016-12-15

0.2 Update section 2,7 2018-2-7

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

2

of

32

Table of Content

1. General Specification ............................................................................................................ 3

2. Block Diagram ........................................................................................................................ 3

3. Terminal Functions ................................................................................................................ 3

3.1 Interface ............................................................................................................................... 4

4. Absolute Maximum Ratings .................................................................................................. 5

5. Electrical Characteristics ...................................................................................................... 5

5.1 DC Characteristics (MCU terminal)....................................................................................... 5

6. AC Characteristics ................................................................................................................. 5

6.1 AC Timing ............................................................................................................................ 5

6.2 TFT Controller Reset Timing ................................................................................................ 6

6.3 Panel Setting of Timing ........................................................................................................ 6

7. Commands ............................................................................................................................. 7

8. Optical Characteristics ........................................................................................................ 28

9. LCD Module Design and Handling Precautions ................................................................. 29

10. CTP Mounting Instructions ................................................................................................. 30

11. RTP Mounting Instructions ................................................................................................. 31

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

3

of

32

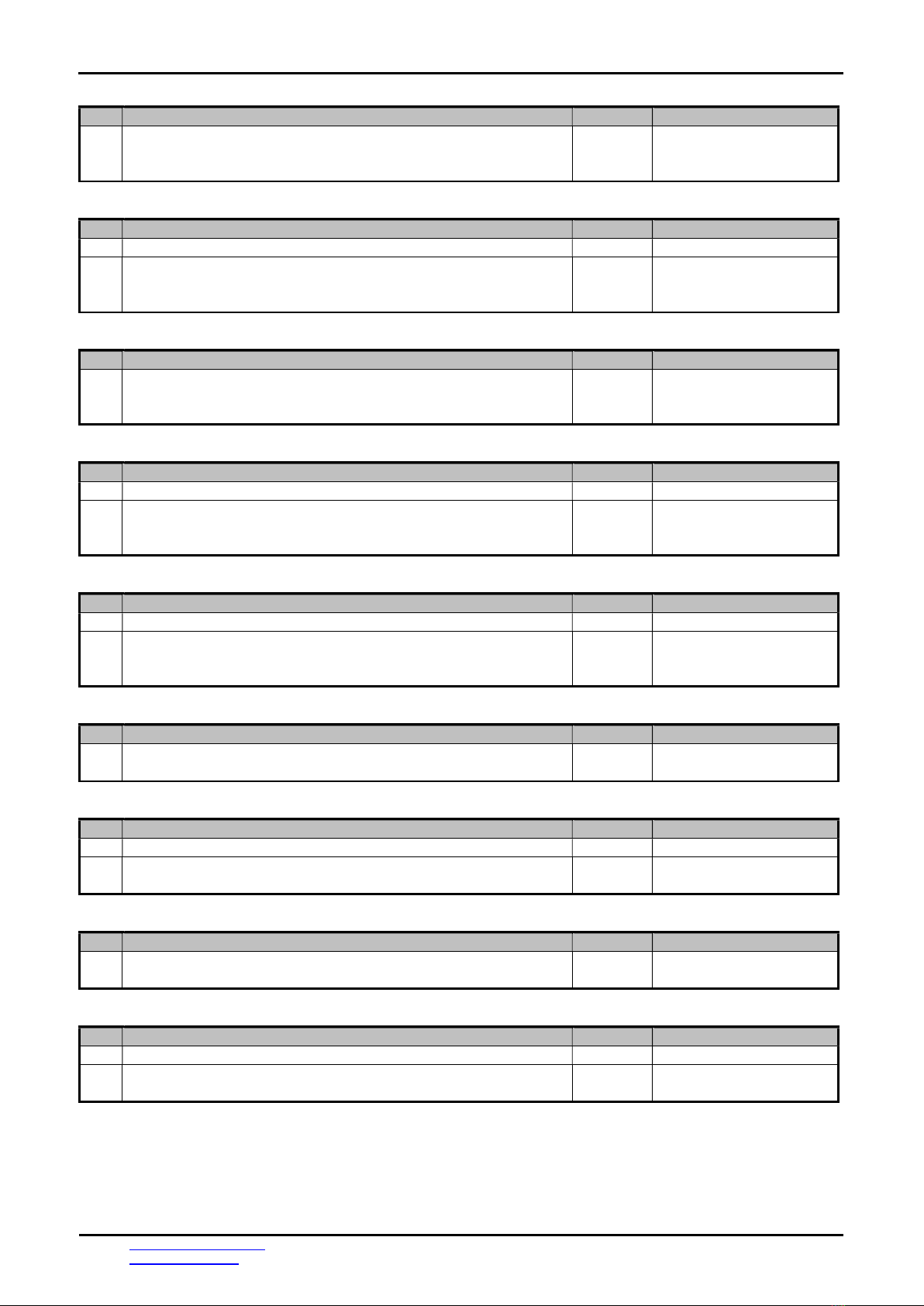

1. General Specification

Note:

*1 Color tune may slightly changed by temperature and driving voltage.

*2. For saturated color display content (eg. pure-red, pure-green, pure-blue, or pure-colors-combinations)

*3. For "color scales" display content

2. Block Diagram

3.

Screen Size(Diagonal) : 5.6”

Outline Dimension : 155.2 x 109.0 x 13.9max (mm)

(see attached drawing for details)

Active Area : 112.886 x 84.672 (mm)

Color Depth:

65k

Number of dots : 640 x 3(RGB) x 480

Pixel Pitch :

0.

0588

x 0.

1

764

(mm)

Pixel Configuration : RGB Stripe

Backlight :

LED

Surface Treatment

:

Anti

-

Glare Treatment

Viewing Direction : 12H (gray scale inverse)(*2)

6

H(*3)

Operating Temperature : -20 ~ +70°C

Storage Temperature :

-

3

0 ~ +

8

0°C

VDD, VSS

D/C, /CS, /RES, TE, /RD, /WR

D0~D7

640 x 480 pixels

TFT Panel

Backlight Circuit

RA8875 or equivalent

Font ROM (GT30L24T3Y)

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

4

of

32

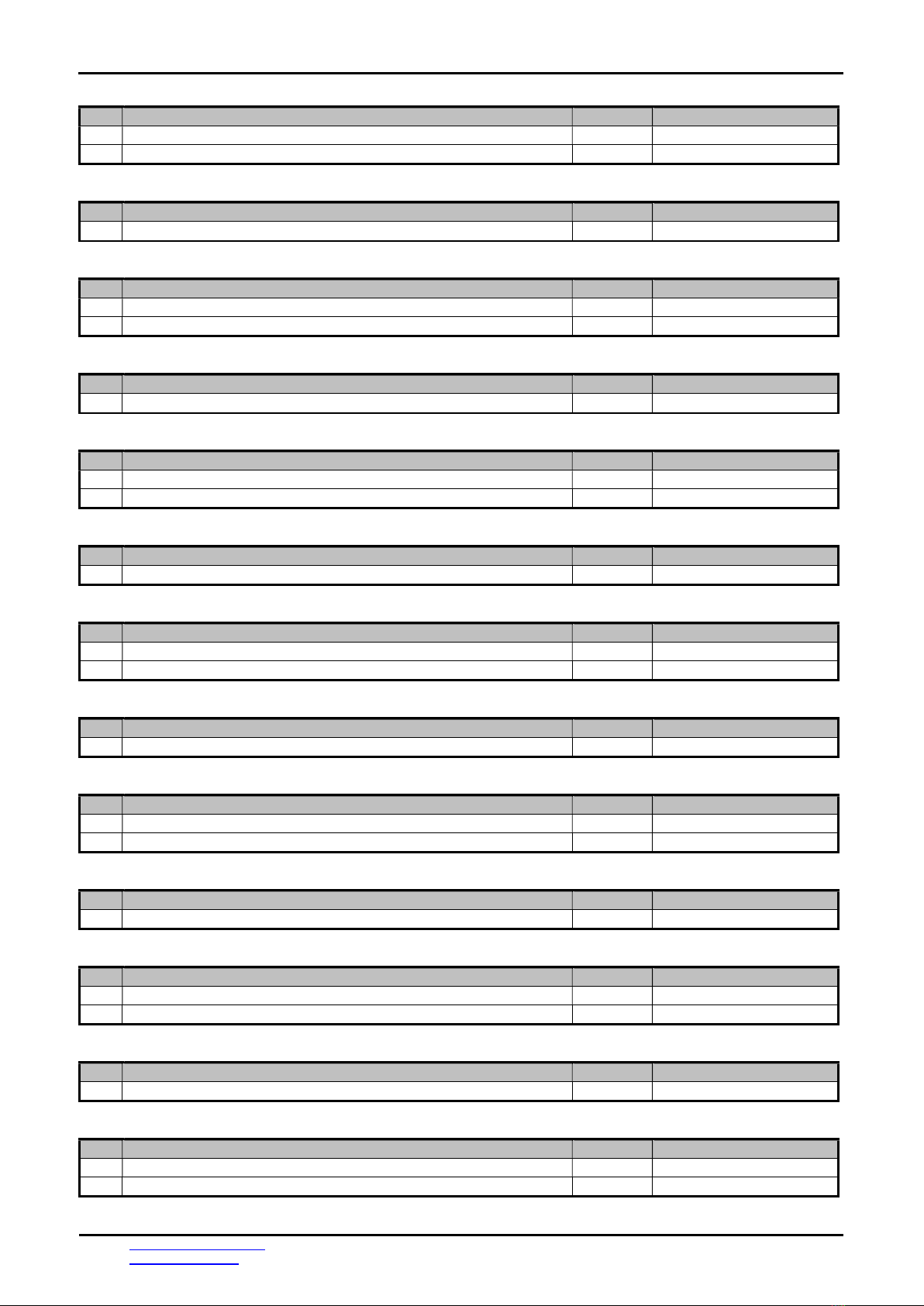

Terminal Functions

3.1 Interface

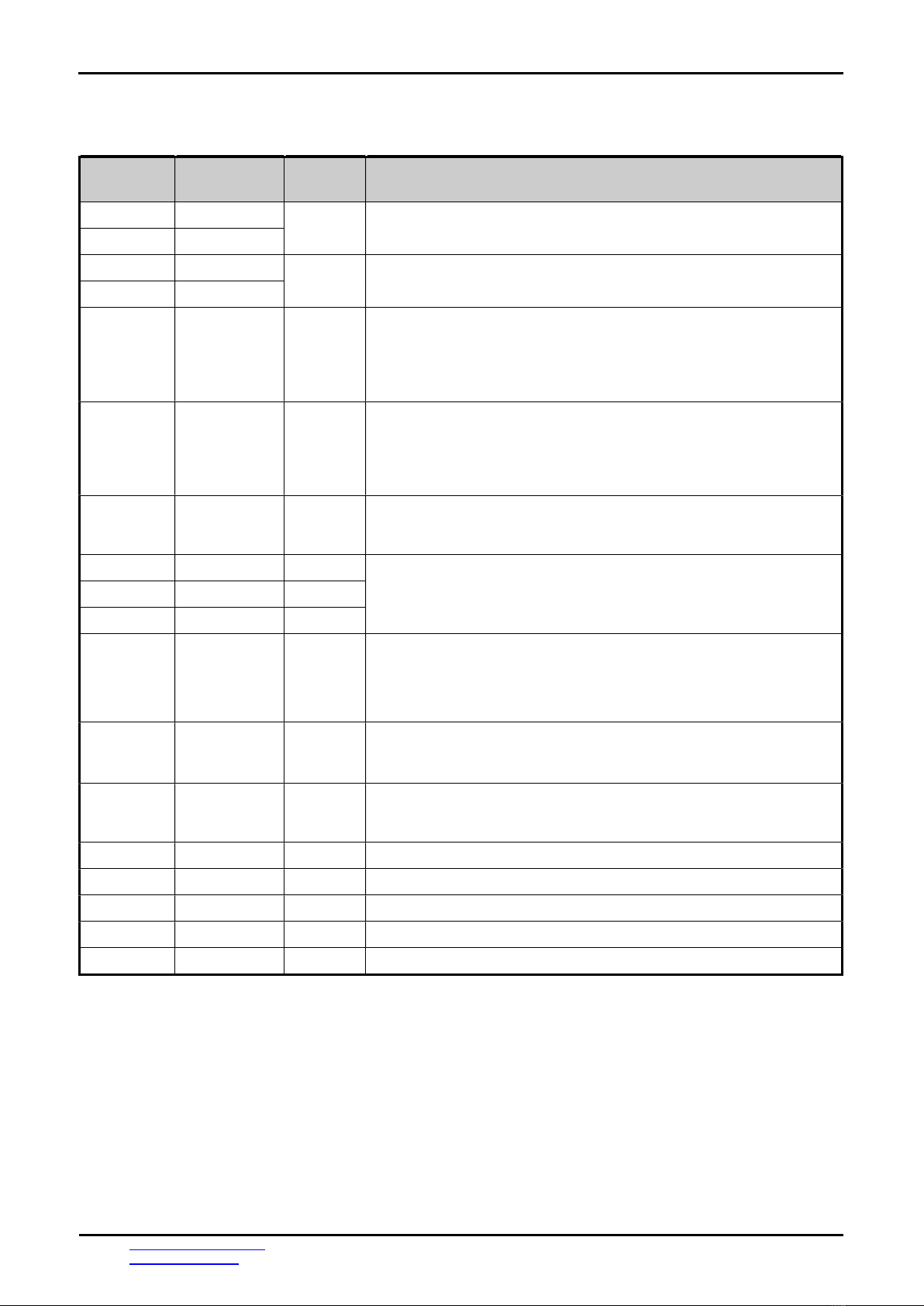

Pin No. Pin Name I/O Descriptions

1 VSS P Power Ground

2 VSS

3 VDD P Positive Power Supply

4 VDD

5 D/C I

Register Select

D/C = H, status read/command write cycle is selected.

D/C = L, data Read/Write cycle is selected.

6 /CS I

Chip Select

/CS=L, enable access to the LCD interface

/CS=H, disable access to the LCD interface

7 /RES I

Reset signal

/RES = L, Initialization is executed

/RES = H, Normal running.

8 D0 I/O

Data BUS

: : :

15 D7 I/O

16 TE O

Controller busy signal output,It is active low and could be used for

MCU to pull busy status by connecting it to I/O port,

MCU should poll this signal before accessing the LCD module

17 /RD I /WR=H, /RD=L;

Data or Status read form the LCD module

18 /WR I /WR=LH, RD=H;

Data or Instruction latch into the LCD module

19 NC -- No Connection

: : : :

28 NC -- No Connection

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

5

of

32

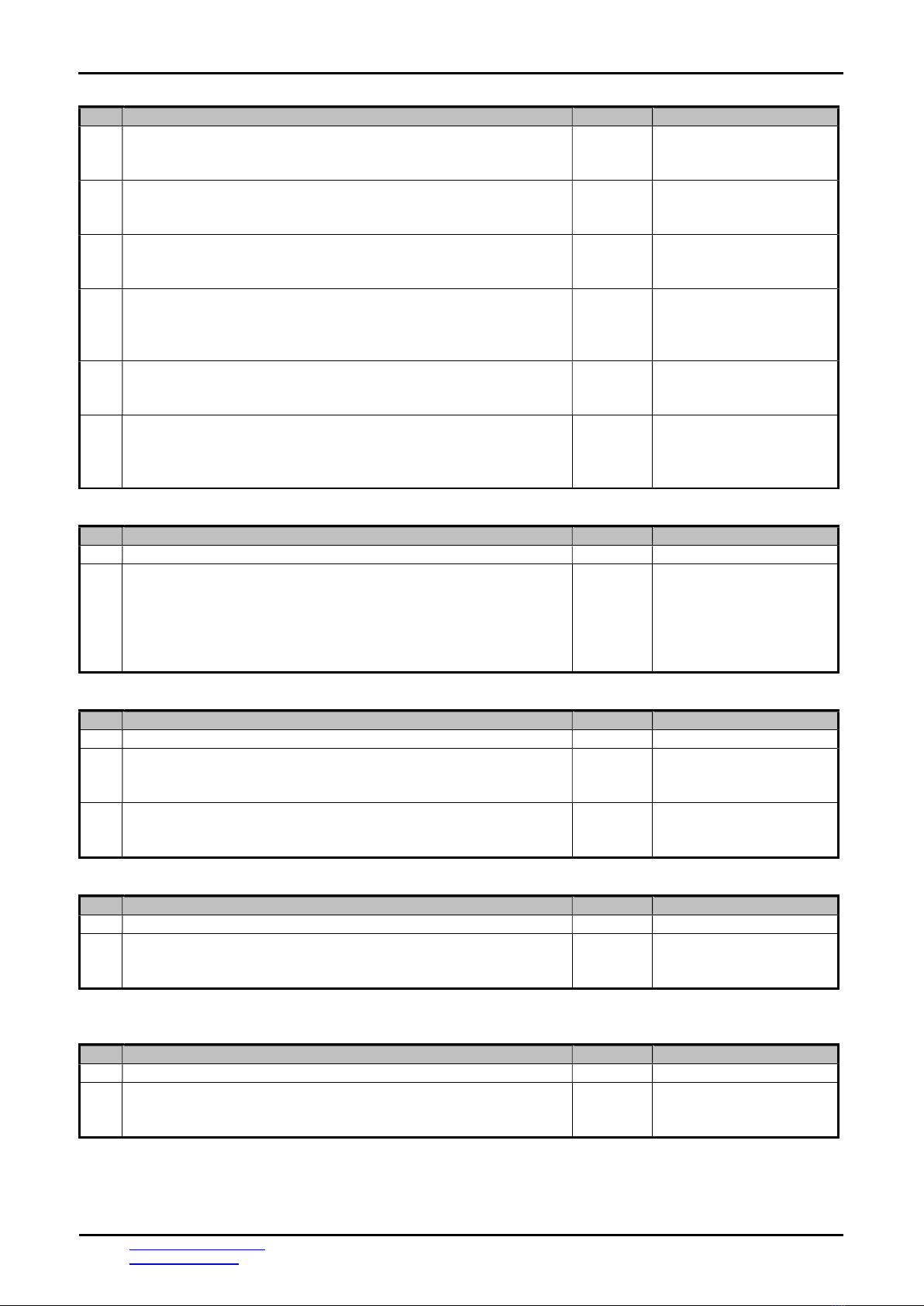

4. Absolute Maximum Ratings

Items

Symbol

Min.

Max.

Unit

Condition

Supply Voltage

V

DD

-

0.3

+

6

.

0

V

GND = 0V

Operating Temperature TOP -20 +70 C No Condensation

Storage Temperature TST -30 +80 C No Condensation

Cautions:

Any Stresses exceeding the Absolute Maximum Ratings may cause substantial damage to the device. Functional

operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure

to extreme conditions may affect device reliability.

5. Electrical Characteristics

5.1 DC Characteristics (MCU terminal)

VDD=5.0V, VSS=0V, TOP =25C

Items

Symbol

MIN.

TYP.

MAX.

Unit

Applicable Pin

Operating Voltage VDD 4.8 5.0 5.2 V VDD

Input High Voltage VIH 3.0 - VDD V /RD, /WR, D/C, /CS,

D0~D7, /RES

Input Low Voltage VIL 0 - 0.6 V

Output Signal High Voltage

VOH 3.0 - 3.6 V D0~D7, TE

Output Signal Low Voltage VOL 0 - 0.6 V

Operating Current IDD - 450 - mA Backlight (100%PWM)

- 349 - mA Backlight (70%PWM)

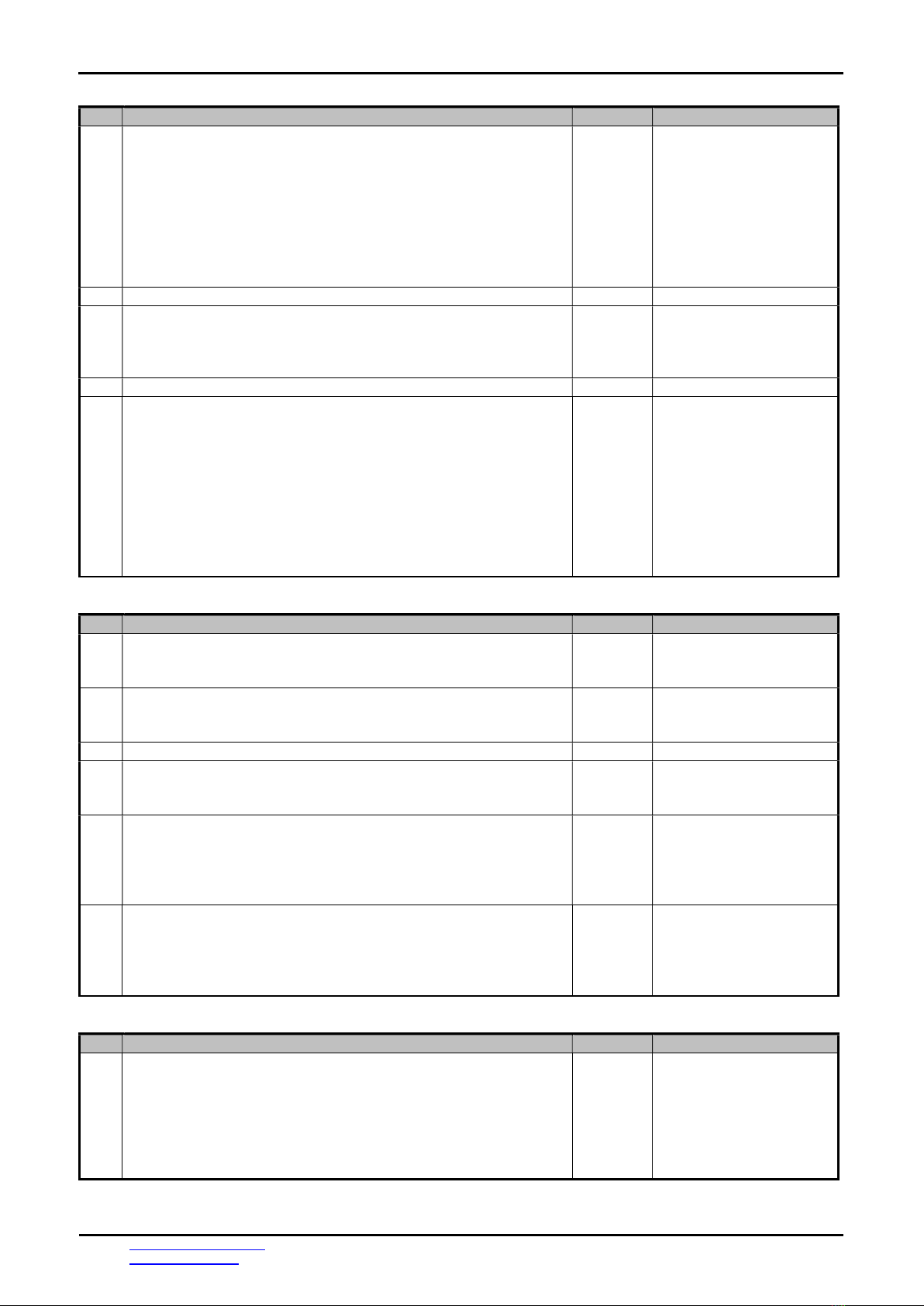

6. AC Characteristics

6.1 AC Timing

VDD=5.0V, VSS=0V, TOP =25C

Parameter Symbol

Spec. Unit

Description

Min.

T

yp

M

ax

.

Cycle time tCYC8 71 - -

ns

tc is one system

clock period:

tc = 1/SYS_CLK

Strobe Pulse width tCCC8 28 - -

Address setup time tAS8 5 - -

Address hold time tAH8 14 - -

Data setup time tDS8 28 - -

Data hold time tDH8 14 - -

Data output access time tACC8 0 - 28

Data output hold time tOH8 0 - 28

Note:1. Refer to the RA8875 datasheet for more details.

2. SYS_CLK (System clock) = 30MHz

Register Write/Read timing (for CPU 8 Bit)

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

6

of

32

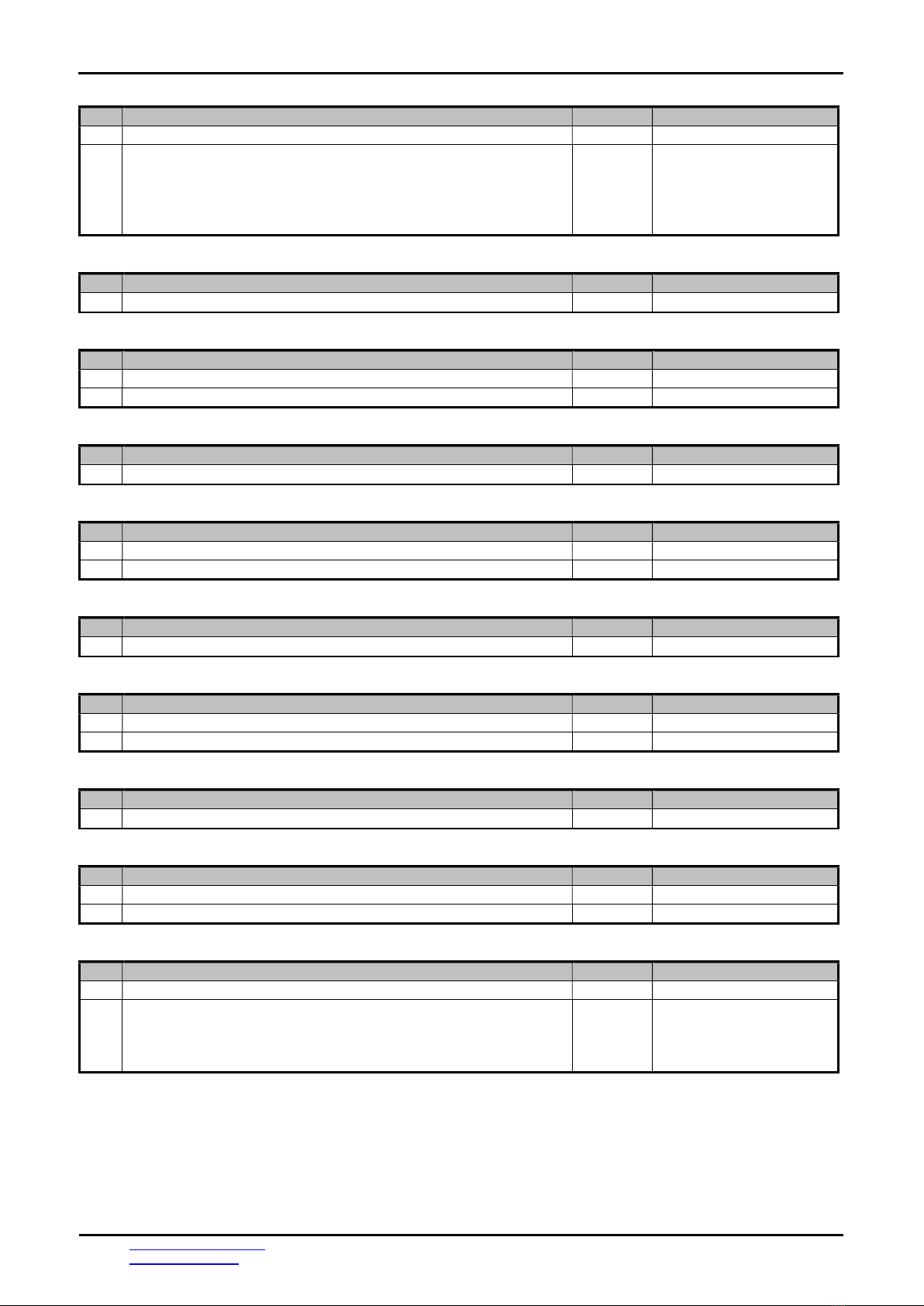

6.2 TFT Controller Reset Timing

VSS=0V, VDD=5.0V, TOP=25C

6.3 Panel Setting of Timing

Item

Symbol

MIN.

TYP.

MAX.

Unit

Reset setup time trs 2 - - ms

Reset pulse

trst

0.2

-

-

ms

Reset hold time trh 2 - - ms

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

7

of

32

7. Commands

REG[01h] Power and Display Control Register (PWRR)

Bit

Description

Default

Access

7

LCD Display Off

0:display off.

1:display on.

0 RW

6-2

NA 0 RO

1

Sleep Mode

0:Normal mode.

1:Sleep mode.

Note:

1.There are 3 ways to wake up from sleep mode:

Touch Panel wake up,Key Scan wake up,Software wake up.

2. When using IIC, this function is not supported.

3. When using SPI, it has its particular steps to use this

function, refer to section 6-1-2-3 please.

0 RW

0

Software Reset

0 : No action.

1 : Software Reset.

Note:The bit must be set to 1 and then set to 0 to complete

a software reset

0 WO

REG[02h] Memory Read/Write Command (MRWC)

Bit

Description

Default

Access

7-0

Write Function : Memory Write Data

Data to write in memory corresponding to the setting of

MWCR1[3:2].Continuous data write cycle can be accepted in

bulk data write case.

Read Function : Memory Read Data

Data to read from memory corresponding to the setting of

MWCR1[3:2]. Continuous data read cycle can be accepted in

bulk data read case. Note that the first data read cycle is

dummy read and need to be ignored.

-- RW

REG[04h] Pixel Clock Setting Register (PCSR)

B

it

Description

Default

Access

7

PCLK Inversion

0 : PDAT is fetched at PCLK rising edge.

1 : PDAT is fetched at PCLK falling edge.

0 RW

6-2

NA 0 RO

1-0

PCLK Period Setting

pixel clock (PCLK) period setting.

00b: PCLK period = System Clock period.

01b: PCLK period = 2 times of System Clock period.

10b: PCLK period = 4 times of System Clock period.

11b: PCLK period = 8 times of System Clock period.

0 RW

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

8

of

32

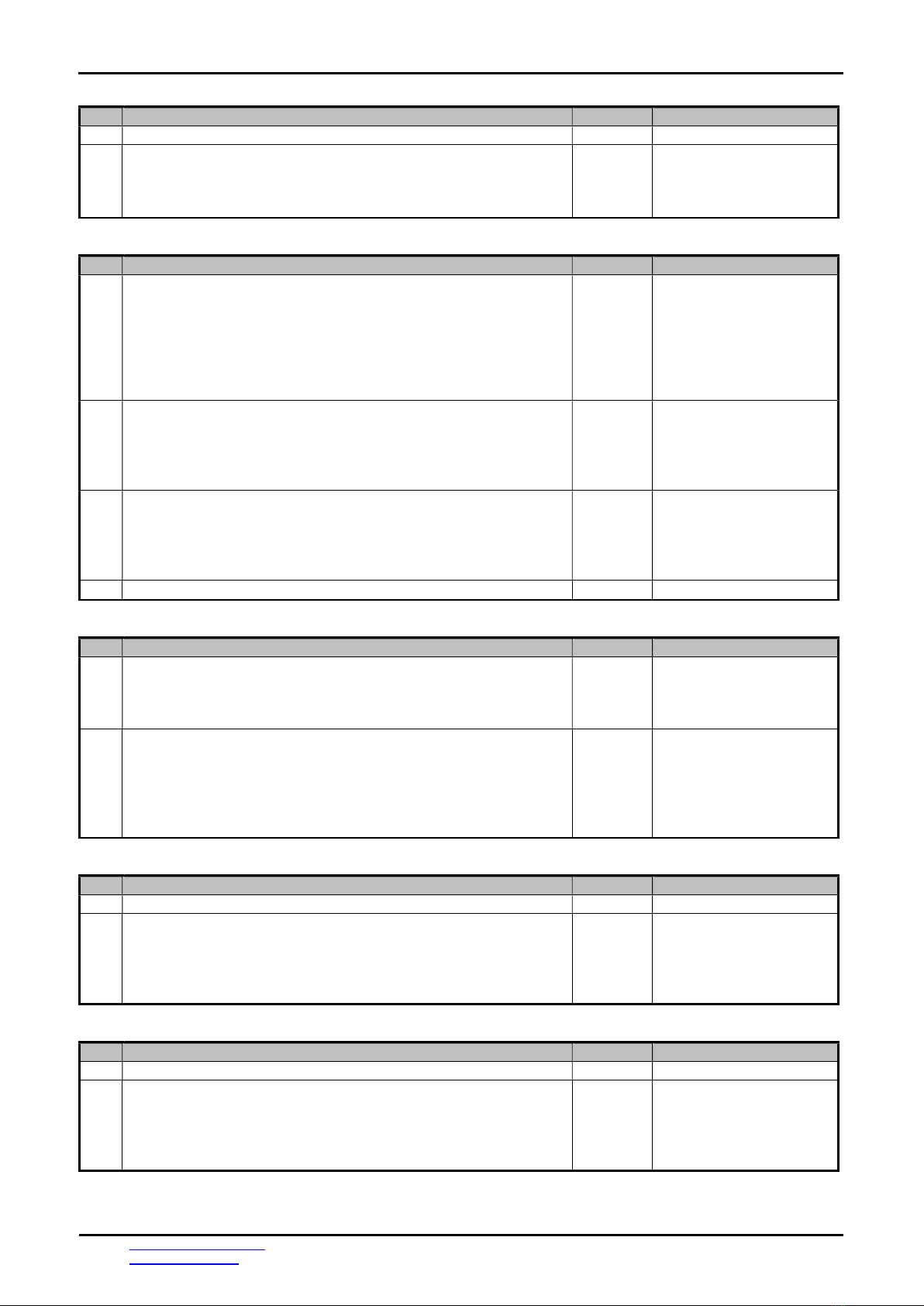

REG[05h] Serial Flash/ROM Configuration Register (SROC)

Bit

Description

Default

Access

7

Serial Flash/ROM I/F # Select

0: Serial Flash/ROM 0 I/F is selected.

1: Serial Flash/ROM 1 I/F is selected.

0 RW

6

Serial Flash/ROM Address Mode

0: 24 bits address mode

This bit must set to 0 for serial flash .

0 RW

5

Serial Flash/ROM Waveform Mode

Mode 0.

Mode 3.

0 RW

4-3

Serial Flash /ROM Read Cycle

00b: 4 bus no dummy cycle

01b: 5 bus 1 byte dummy cycle

1xb: 6 bus 2 byte dummy cycle

0 RW

2

Serial Flash /ROM Access Mode

0: Font mode

1: DMA mode

0 RW

1-0

Serial Flash /ROM I/F Data Latch Mode Select

0xb: Single Mode

10b: Dual Mode 0.

11b: Dual Mode 1.

0 RW

REG[06h] Serial Flash/ROM CLK Setting Register(SFCLR)

Bit

Description

Default

Access

7-2

NA 0 RO

1-0

Serial Flash/ROM Clock Frequency Setting

0xb: SFCL frequency = System clock frequency

(When DMA enable and Color depth = 256 color)

SFCL frequency = System clock frequency /2)

10b: SFCL frequency = System clock frequency / 2

11b: SFCL frequency = System clock frequency / 4

0 RW

REG[10h] System Configuration Register (SYSR)

Bit

Description

Default

Access

7-4

N/A 0 RO

3-2

Color Depth Setting

00b : 8-bpp generic TFT, i.e. 256 colors.

1xb : 16-bpp generic TFT, i.e. 65K colors.

0 RW

1-0

MCUIF Selection

00b : 8-bit MCU Interface.

1xb : 16-bit MCU Interface.

0 RW

REG[12h] GPI

Bit

Description

Default

Access

7-5

NA 0 RO

4-0

GPI[4:0] : General Purpose Input.

KEY_EN = 0: General Purpose Input from pin KIN[4:0]

KEY_EN = 1: NC

NA RO

Note:KEY_EN : REG[C0h] bit 7

REG[13h] GPO

Bit

Description

Default

Access

7-4

NA 0 RO

3-0

GPO[3:0] : General Purpose Output

KEY_EN = 0: General Purpose Output to KOUT[3:0]

KEY_EN = 1: NC

0 RW

Note: KxY_EN : REG[C0h] bit 7

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

9

of

32

REG[14h] LCD Horizontal Display Width Register (HDWR)

Bit

Description

Default

Access

7 NA 0 RO

6-0

Horizontal Display Width Setting Bit[6:0]

The register specifies the LCD panel horizontal display width

in the unit of 8 pixels resolution.

Horizontal display width(pixels) = (HDWR + 1)x8

0 RW

Note : HDWR must be set less than 64h because that the maximum horizontal display width is 800 pixels

.

REG[15h] Horizontal Non-Display Period Fine Tuning Option Register (HNDFTR)

Bit

Description

Default

Access

7

DE Polarity

0 : high active.

1 : low active.

0 RW

6-4

NA 0 RO

3-0

Horizontal Non-Display Period Fine Tuning(HNDFT) [3:0]

This register specifies the fine tuning for horizontal non-

display period; it is used to support the SYNC mode panel.

Each level of this modulation is 2-pixel.

0 RW

REG[16h] LCD Horizontal Non-Display Period Register (HNDR)

Bit

Descript

ion

Default

Access

7-5

NA 0 RO

4-0

Horizontal Non-Display Period(HNDP) Bit[4:0]

This register specifies the horizontal non-display period.

Horizontal Non-Display Period (pixels)

=(HNDR + 1)x8+(HNDFTR/2+1)x2 + 2

0 RW

REG[17h] HSYNC Start Position Register (HSTR)

Bit

Description

Default

Access

7-5

NA 0 RO

4-0

HSYNC Start Position[4:0]

The starting position from the end of display area to the

beginning of HSYNC. Each level of this modulation is 8-pixel.

HSYNC Start Position(pixels) = (HSTR + 1)x8

0 RW

REG[18h] HSYNC Pulse Width Resister (HPWR)

Bit

Description

Default

Access

7

HSYNC Polarity

0 : Low active.

1 : High active.

0 RW

6-5

NA 0 RO

4-0

HSYNC Pulse Width(HPW) [4:0]

The period width of HSYNC.

HSYNC Pulse Width(pixels) = (HPW + 1)x8

0 RW

REG[19h] LCD Vertical Display Height Register (VDHR0)

Bit

Description

Default

Access

7-0

Vertical Display Height Bit[7:0]

Vertical display Height(Line) = VDHR + 1

0 RW

REG[1Ah] LCD Vertical Display Height Register0 (VDHR1)

Bit

Description

Default

Acc

ess

7-1

NA

0 RO

0 Vertical Display Height bit[8]

Vertical Display Height(Line) = VDHR + 1

0 RW

Note : The VDHR must be set less than 1E0h, because the maximum vertical display height is 480.

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

10

of

32

REG[1Bh] LCD Vertical Non-Display Period Register (VNDR0)

Bit

Description

Default

Access

7-0

Vertical Non-Display Period Bit[7:0]

Vertical Non-Display Period(Line) = (VNDR + 1) 0 RW

REG[1Ch] LCD Vertical Non-Display Period Register (VNDR1)

Bit

Description

Default

Acces

s

7-1

NA 0 RO

0 Vertical Non-Display Period bit[8]

Vertical Non-Display Period(Line) = (VNDR + 1)

0 RW

REG[1Dh] VSYNC Start Position Register (VSTR0)

Bit

Description

Default

Access

7-0

VSYNC Start Position[7:0]

The starting position from the end of display area to the

beginning of VSYNC.

VSYNC Start Position(Line) = (VSTR + 1)

0 RW

REG[1Eh] VSYNC Start Position Register (VSTR1)

Bit

Description

Default

Access

7-1

NA 0 RO

0

VSYNC Start Position[8]

The starting from the end of display area to the beginning of

VSYNC.

VSYNC Start Position(Line) = (VSTR + 1)

0 RW

REG[1Fh] VSYNC Pulse Width Register (VPWR)

Bit

Description

Default

Access

7

VSYNC Polarity

0 : Low active.

1 : High active.

0 RW

6-0

VSYNC Pulse Width[6:0]

The pulse width of VSYNC in lines.

VSYNC Pulse Width(Line) = (VPWR + 1)

0 RW

REG[20h] Display Configuration Register (DPCR)

Bit

Description

Default

Access

7

Layer Setting Control

0 : One layer configuration is selected.

1 : Two layers configuration is selected.

0 RW

6-4

NA 0 RO

3

HDIR

Horizontal Scan Direction, for n = SEG number.

0 : SEG0 to SEG(n-1).

1 : SEG(n-1) to SEG0.

0 RW

2

VDIR

Vertical Scan direction, for n = COM number

0 : COM0 to COM(n-1).

1 : COM(n-1) to COM0.

0 RW

1-0

NA 0 RO

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

11

of

32

REG[21h] Font Control Register 0 (FNCR0)

Bit

Description

Default

Access

7

CGRAM/CGROM Font Selection Bit in Text Mode

0 : CGROM font is selected.

1 : CGRAM font is selected.

Note:

1. The bit is used to select the bit-map source when text-mode

is active(REG[40h] bit 7 is 1), when CGRAM is

writing(REG[41h] bit 3-2 =01b), the bit must be set as “0”.

2. When CGRAM font is select, REG[21h] bit 5 must be set as

1.

0 RW

6 NA 0 RO

5

External/Internal CGROM Selection Bit

0 : Internal CGROM is selected.(REG[2Fh] must bx set 00h )

1 : External CGROM is selected. (REG[2Eh] bit6 &bit7 must

be set 0)

0 RW

4-2

NA 0 RO

1-0

Font Selection for internal CGROM

When FNCR0 B7 = 0 and B5 = 0, Internal CGROM supports

the 8x16 character sets with the standard coding of ISO/IEC

8859- 1~4, which supports English and most of European

country languages.

00b : ISO/IEC 8859-1.

01b : ISO/IEC 8859-2.

10b : ISO/IEC 8859-3.

11b : ISO/IEC 8859-4.

0 RW

REG[22h] Font Control Register1 (FNCR1)

Bit

Description

Default

Access

7

Full Alignment Selection Bit

0 : Full alignment is disable.

1 : Full alignment is enable.

0 RW

6

Font Transparency

0 : Font with background color.

1 : Font with background transparency.

0 RW

5 NA 0 RO

4

Font Rotation

0 : Normal.

1 : 90 degree display.

0 RW

3-2

Horizontal Font Enlargement

00b : X1.

01b : X2.

10b : X3.

11b : X4.

0 RW

1-0

Vertical Font Enlargement

00b : X1.

01b : X2.

10b : X3.

11b : X4.

0 RW

REG[23h] CGRAM Select Register (CGSR)

Bit

Description

Default

Access

7-0

CGRAM No.

The setting of the number of the character in CGRAM. It’s

used to write the user-defined character bitmap data into

CGRAM. 16 continuous data write cycles compete the bitmap

writing of a 8x16 character. Note that the MWCR1 bit 3-2 must

be set as 01b(CGRAM) first. And more than 16 data write

cycles will loop back to the 1st data and cover the bitmap.

0 RW

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

12

of

32

REG[24h] Horizontal Scroll Offset Register 0 (HOFS0)

Bit

Description

Default

Access

7-0

Horizontal Display Scroll Offset [7:0]

The display offset of the horizontal direction, changing the

value will cause the effect of scrolling at horizontal direction.

0 RW

REG[25h] Horizontal Scroll Offset Register 1 (HOFS1)

Bit

Description

Default

Access

7-3

NA

0 RO

2-0

Horizontal Display Scroll Offset [10:8]

The display offset of the horizontal direction, changing the

value will cause the effect of scrolling at horizontal direction.

0 RW

REG[26h] Vertical Scroll Offset Register 0 (VOFS0)

Bit

Description

Default

Access

7-0

Vertical Display Scroll Offset [7:0]

The display offset of the vertical direction, changing the

value will cause the effect of scrolling at vertical direction.

0 RW

REG[27h] Vertical Scroll Offset Register 1 (VOFS1)

Bit

Description

Default

Access

7-2

NA

0 RO

1-0

Vertical Display Scroll Offset [9:8]

The display offset of the v ertical direction, changing the

value will cause the effect of scrolling at vertical direction.

0 RW

REG[29h] Font Line Distance Setting Register (FLDR)

Bit

Description

Default

Access

7-5

NA

0 RO

4-0

Font Line Distance Setting

Setting the font character line distance when setting

memory font write cursor auto move. (Unit: pixel)

0 RW

REG[2Ah] Font Write Cursor Horizontal Position Register 0 (F_CURXL)

Bit

Description

Default

Access

7-0

Font Write Cursor Horizontal Position[7:0]

The setting of the horizontal cursor position for font writing. 0 RW

REG[2Bh] Font Write Cursor Horizontal Position Register 1 (F_CURXH)

Bit

Description

Default

Access

7-2

NA

0 RO

1-0

Font Write Cursor Horizontal Position[9:8]

The setting of the horizontal cursor position for font writing.

0 RW

REG[2Ch] Font Write Cursor Vertical Position Register 0 (F_CURYL)

Bit

Description

Default

Access

7-0

Font Write Cursor Vertical Position[7:0]

The setting of the vertical cursor position for font writing.

0 RW

REG[2Dh] Font Write Cursor Vertical Position Register 1 (F_CURYH)

Bit

Description

Default

Access

7-1

NA

0 RO

0 Font Write Cursor Vertical Position[8]

The setting of the vertical cursor position for font writing.

0 RW

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

13

of

32

REG[2Eh] Font Write Type Setting Resister

Bit

Description

Default

Access

7-6

Font Size Setting(* 1)

Full Size Half-Size Variable

Width

00b

16x16

8x16

NX16

01b

24x24

12x24

NX24

1Xb(* 2)

32x32

16x32

NX32

Note:

* 1The font width indicated by “N” depends on the character

code of the FONT.

* 2 The command is invalid , GT30L24T3Y does not support

size of 32x32 .

0 RW

5-0

Font to Font Width Setting

00h : Font width off

01h : Font to Font width = 1 pixel

02h : Font to Font width = 2 pixels

:

3Fh : Font to Font width = 63 pixels

0 RW

REG[2Fh] Serial Font ROM Setting

Bit

Description

Default

Access

7-5

GT Serial Font ROM Select

000b: GT21L16TW / GT21H16T1W

001b: GT30L16U2W

010b: GT30L24T3Y / GT30H24T3Y

011b: GT30L24M1Z

100b: GT30L32S4W / GT30H32S4W

0 RW

4-2

FONT ROM Coding Setting

For specific GT serial Font ROM, the coding method must

be set for decoding.

000b: GB2312

001b: GB12345/GB18030

010b: BIG5

011b: UNICODE

100b: ASCII

101b: UNI-Japanese

110b: JIS0208

111b: Latin/Greek/ Cyrillic / Arabic

0 RW

1-0

ASCII / Latin/Greek/ Cyrillic / Arabic Latin

ASCII Latin/Greek/

C

y

rillic

Arabic

Latin

00b

Normal

Normal

NA

01b Arial Variable

Width

Presentation

forms-A

10b Roman

NA

Forms-B

11b Bold

NA

NA

0 RW

REG[30h] Horizontal Start Point 0 of Active Window (HSAW0)

Bit

Description

Default

Access

7-0

Horizontal Star

t

P

r

int of

a

ctive Win

d

ow [7:0]

0 RW

REG[31h] Horizontal Start Point 1 of active Window (HSAW1)

Bit

Description

Default

Access

7-2

NA

0 RO

1-0

Horizontal

S

t

art

Point

of

Acti

ve

Window

[9:8]

0 RW

REG[32h] Vertical Start Point 0 of Active Window (VSAW0)

Bit

Description

Default

Access

7-0

Vertical Start Point of Active Window [7:0]

0 RW

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

14

of

32

REG[33h] Vertical Start Point 1 of Active Window (VSAW1)

Bit

Description

Default

A

ccess

7-1

NA

0 RO

0

Vertical

Start

Point

of

Acti

v

e Windo

w

[8]

0 RW

REG[34h] Horizontal End Point 0 of Active Window (HEAW0)

Bit

Description

Default

Access

7-0

Horizontal End Poi

n

t of Active Window [7:0]

0 RW

REG[35h] Horizontal End Point 1 of Active Window (HEAW1)

Bit

Description

Default

Access

7-2

NA

0 RO

1-0

Horizontal

En

d

Point of Acti

ve

Window

[9:8]

0 RW

REG[36h] Vertical End Point of Active Window 0 (VEAW0)

Bit

Description

Default

Access

7-0

Vertica

l

End

Point

of

Acti

ve

Window

[7:0]

0 RW

REG[37h] Vertical End Point of Active Window 1 (VEAW1)

Bit

Description

Default

Access

7-1

NA

0 RO

0

Vertical End Point of Acti

ve

Window

[8]

0 RW

REG[38h] Horizontal Start Point 0 of Scroll Window (HSSW0)

Bit

Description

Default

Access

7-0

H

oriz

ontal Start Poi

n

t of Scrol

l

Wi

n

dow [7:0]

0 RW

REG[39h] Horizontal Start Point 1 of Scroll Window (HSSW1)

Bit

Description

Default

Access

7-2

NA

0 RO

1-0

Horizonta

l

Start Point of Scroll

W

indo

w

[9:8]

0 RW

REG[3Ah] Vertical Start Point 0 of Scroll Window (VSSW0)

Bit

Description

Default

Access

7-0

Vertical

Start

Point

of

Scrol

l

Window

[7:0]

0 RW

REG[3Bh] Vertical Start Point 1 of Scroll Window (VSSW1)

Bit

Description

Default

Access

7-1

NA

0 RO

0

Vertical St

art Point of Scroll Window

[8]

0 RW

REG[3Ch] Horizontal End Point 0 of Scroll Window (HESW0)

Bit

Description

Default

Access

7-0

Horizontal End Point of Scroll Window

[7:0]

0 RW

REG[3Dh] Horizontal End Point 1 of Scroll Window (HESW1)

Bit

Description

Default

Access

7-2

NA

0 RO

1-0

Hori

zontal End Point of Scroll Window

[9:8]

0 RW

REG[3Eh] Vertical End Point 0 of Scroll Window (VESW0)

Bit

Description

Default

Access

7-0

Vertica

l

End Point of Scroll Windo

w

[7:0]

0 RW

REG[3Fh] Vertical End Point 1 of Scroll Window (VESW1)

Bit

Descri

ption

Default

Access

7-1

NA

0 RO

0

V

e

rtica

l

End Point of Scroll Window [8]

0 RW

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

15

of

32

REG[40h] Memory Write Control Register 0 (MWCR0)

Bit

Description

Default

Access

7

Text Mode enable

0 : Graphic mode.

1 : Text mode.

0 RW

6

Font Write Cursor/ Memory Write Cursor Enable

0 : Font write cursor/ Memory Write Cursor is not visible.

1 : Font write cursor/ Memory Write Cursor is visible.

0 RW

5

Font Write Cursor/ Memory Write Cursor Blink Enable

0 : Normal display.

1 : Blink display.

0 RW

4

NA

0 RO

3-2

Memory Write Direction (Only for Graphic Mode)

00b : Left Right then Top Down.

01b : Right Left then Top Down.

10b : Top Down then Left Right.

11b : Down Top then Left Right.

0 RW

1

Memory Write Cursor Auto-Increase Disable

0 : Cursor auto-increases when memory write.

1 : Cursor doesn’t auto-increases when memory write.

0 RW

0

Memory Read Cursor Auto-Increase Disable

0 : Cursor auto-increases when memory read.

1 : Cursor doesn’t auto-increases when memory read.

0 RW

REG[41h] Memory Write Control Register 1 (MWCR1)

Bit

Description

D

efault

Access

7

Graphic Cursor Enable

0 : Graphic Cursor disable.

1 : Graphic Cursor enable.

0 RW

6-4

Graphic Cursor Selection Bit

Select one from eight graphic cursor types.(000b to 111b)

000b : Graphic Cursor Set 1.

001b : Graphic Cursor Set 2.

010b : Graphic Cursor Set 3.

: :

111b : Graphic Cursor Set 8.

0 RW

3-2

Write Destination Selection

00b : Layer 1~2.

01b : CGRAM.

10b : Graphic Cursor.

11b : Pattern.

Note : When CGRAM is selected (01b), REG[21h] bit 7 must

be set as “0”.

0 RW

1

NA

0 RO

0

Layer No. for Read/Write Selection

When resolution =< 480x400 or color depth = 8bpp:

0 : Layer 1.

1 : Layer 2.

When resolution > 480x400 and color depth > 8bpp:

NA, always writing to Layer 1.

0 RW

REG[44h] Blink Time Control Register (BTCR)

Bit

Description

Default

Access

7-0

Text Blink Time Setting (Unit: Frame)

00h : 1 frame time.

01h : 2 frames time.

02h : 3 frames time.

:

:

:

FFh : 256 frames time.

0 RW

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

16

of

32

REG[45h] Memory Read Cursor Direction (MRCD)

Bit

Description

Defaul

t

Access

7-2

NA

0 RO

1-0

Memory Read Direction (Only for Graphic Mode)

00b : Left Right then Top Down.

01b : Right Left then Top Down.

10b : Top Down then Left Right.

11b : Down Top then Left Right.

0 RW

REG[46h] Memory Write Cursor Horizontal Position Register 0 (CURH0)

Bit

Description

Default

Access

7-0

Memory

Write

Cursor

Horizontal Location[7:

0

]

0 RW

REG[47h] Memory Write Cursor Horizontal Position Register 1 (CURH1)

Bit

Description

Default

Access

7-2

NA

0 RO

1-0

Memory

Write

Cursor

Horizontal L

o

cation[9:8]

0 RW

REG[48h] Memory Write Cursor Vertical Position Register 0 (CURV0)

Bit

Description

Default

Access

7-0

Memory

Write

Cursor

Vertical

Location[7:0]

0 RW

REG[49h] Memory Write Cursor Vertical Position Register 1 (CURV1)

Bit

Description

Default

Access

7-1

NA

0 RO

0

Memory Write Cur

sor Verti

c

al Location[8]

0 RW

REG[4Ah] Memory Read Cursor Horizontal Position Register 0 (RCURH0)

Bit

Description

Default

Access

7-0

Memory

Read

Cursor Horizontal Lo

c

ation[7:0]

0 RW

REG[4Bh] Memory Read Cursor Horizontal Position Register 1 (RCURH01)

Bit

Description

Default

Access

7-2

NA

0 RO

1-0

Memory

Read

Cursor

Horizontal

Location[9:8]

0 RW

REG[4Ch] Memory Read Cursor Vertical Position Register 0 (RCURV0)

Bit

Description

Default

Access

7-0

Me

m

ory

Read

Cursor

Verti

c

al

Location[7:0]

0 RW

REG[4Dh] Memory Read Cursor Vertical Position Register 1 (RCURV1)

Bit

Description

Default

Access

7-1

NA

0 RO

0

Memory Read

C

u

r

sor Vertical Location[8]

0 RW

REG[4Eh] Font Write Cursor and Memory Write Cursor Horizontal Size Register (CURHS)

Bit

Description

Default

Access

7-5

NA

0 RO

4-0

Font Write Cursor Horizontal Size Setting[4:0]

Unit : Pixel

Note : When font is enlarged, the cursor setting will multiply

the same times as the font enlargement.

7h RW

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

17

of

32

REG[4Fh] Font Write Cursor Vertical Size Register (CURVS)

Bit

Description

Default

Access

7-5

NA

0 RO

4-0

Font Write Cursor Vertical Size Setting[4:0]

Unit : Pixel

Note : When font is enlarged, the cursor setting will multiply

the same times as the font enlargement.

0 RW

REG[50h] BTE Function Control Register 0 (BECR0)

Bit

Description

Default

Access

7

BTE Function Enable / Status

Write

0 : No action.

1 : BTE function enable.

Read

0 : BTE function is idle.

1 : BTE function is busy.

0 RW

6

BTE Source Data Select

0 : Block mode,the Source BTE is stored as a rectangular

region of memory.

1 : Linear mode, the Source BTE is stored as a continuous

block of memory.

0 RW

5

BTE Destination Data Type Select

0 : Block mode, the Destination BTE is stored as a rectangular

region of memory.

1 : Linear mode, the Destination BTE is stored as a

continuous block of memory.

0 RW

4-0

NA

0 RO

REG[51h] BTE Function Control Register1 (BECR1)

Bit

Description

Default

Access

7-5

BTE ROP Code Bit[3:0]

ROP is the acronym for Raster Operation. Some of BTE

operation code has to collocate with ROP for the detailed

function. (Please refer to the Section 7-6)

0 RW

4-0

BTE Operation Code Bit[3:0]

RA8875 includes a 2D BTE Engine, it can execute 13 BTE

functions, the operation code range is from 1100b to 0000b

and 1111b to 1101b are not used. Some of BTE Operation

Code has to collocate with the ROP code for the advance

function. (Please refer to the Section 7-6)

0 RW

REG[68h] Background Color Register for Transparent 1 (BGTR1)

Bit

Description

Default

Access

7-6

NA

0 RO

5-0

Foreground Color Green[5:0]

If REG[10h] Bit[3:2] is set to 256 colors, the register only uses

Bit[2:0].

If REG[10h] Bit[3:2] is set to 65K colors, the register uses

Bit[5:0].

0 RW

REG[69h] Background Color Register for Transparent 2 (BGTR2)

Bit

Description

Default

Access

7-5

NA

0 RO

4-0

Foreground Color Blue[4:0]

If REG[10h] Bit[3:2] is set to 256 colors, the register only uses

Bit[1:0].

If REG[10h] Bit[3:2] is set to 65K colors, the register uses

Bit[4:0].

0 RW

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

18

of

32

REG[80h] Graphic Cursor Horizontal Position Register 0 (GCHP0)

Bit

Description

Default

Access

7-0

Graphic C

u

rsor H

o

riz

o

ntal Location[7:0]

0 RW

REG[81h] Graphic Cursor Horizontal Position Register 1 (GCHP1)

Bit

Description

Default

A

ccess

7-2

NA

0 RO

1-0

G

r

ap

h

ic Cursor Horizont

a

l Lo

c

ation[

9

:8]

0 RW

REG[82h] Graphic Cursor Vertical Position Register 0 (GCVP0)

Bit

Description

Default

Access

7-0

Graphic

Cursor

Vertical

Location[7:0]

0 RW

REG[83h] Graphic Cursor Vertical Position Register 1 (GCVP1)

Bit

Description

Default

Access

7-1

NA

0 RO

0

Graphic C

u

rsor

V

ertical Locatio

n

[8]

0 RW

REG[84h] Graphic Cursor Color 0 (GCC0)

Bit

Description

Default

Access

7-0

Graphic Cursor Color 0 with 256 colors

RGB Format [7:0] = RRRGGGBB.

0 RW

REG[85h] Graphic Cursor Color 1 (GCC1)

Bit

Description

Default

Access

7-0

Graphic Cursor Color 1 with 256 Colors

RGB Format [7:0] = RRRGGGBB.

0 RW

REG[88h] PLL Control Register 1 (PLLC1)

Bit

Description

Default

Access

7

PLLDIVM

PLL Pre-driver parameter.

0 : divided by 1.

1 : divided by 2.

0 RW

6-5

NA 0 RO

4-0

PLLDIVN[4:0]

PLL input parameter, the value should be 1~31. (i.e. value 0

is forbidden).

0 RW

REG[89h] PLL Control Register 2 (PLLC2)

Bit

Description

Default

Access

7-3

NA

0 RO

2-0

PLLDIVK[2:0]

PLL Output divider

000b : divided by 1.

001b : divided by 2.

010b : divided by 4.

011b : divided by 8.

100b : divided by 16.

101b : divided by 32.

110b : divided by 64.

111b : divided by 128.

03h RW

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

19

of

32

REG[8Ah] PWM1 Control Register (P1CR)

Bit

Description

Default

Access

7

PWM1 Enable

0 : Disable, PWM1_OUT level depends on P1CR bit6.

1 : Enable.

0 RW

6

PWM1 Disable Level

0 : PWM1_OUT is Normal L when PWM disable or Sleep

mode.

1 : PWM1_OUT is Normal H when PWM disable or Sleep

mode.

The bit is only usable when P1CR bit 4 is 0

0 RW

5 Reserved 0 RO

4

PWM1 Function Selection

0 : PWM1 function.

1 : PWM1 output a fixed frequency signal and it is equal to 1

/16 oscillator clock.

PWM1 = FOSC / 16(

N

ote

)

0 RW

3-0

PWM1 Clock Source Divide Ratio

0000b : SYS_CLK / 1

1000b : SYS_CLK / 256

0001b : SYS_CLK / 2

1001b : SYS_CLK / 512

0010b : SYS_CLK / 4

1010b : SYS_CLK / 1024

0011b : SYS_CLK / 8

1011b : SYS_CLK / 2048

0100b : SYS_CLK / 16

1100b : SYS_CLK / 4096

0101b : SYS_CLK / 32

1101b : SYS_CLK / 8192

0110b : SYS_CLK / 64

1110b : SYS_CLK / 16384

0111b : SYS_CLK / 128

1111b : SYS_CLK / 32768

For example, if the system clock is 20MHz and Bit[3:0]

=0001b, when the clock source of PWM1 is 10MHz.

0 RW

Note : FOSC is the frequency of external oscillator.

REG[8Bh] PWM1 Duty cycle Register (P1DCR)

Bit

Description

Default

Access

7-0

PWM Cycle Duty Selection Bit

00h 1 / 256 Duty with PWM1 clock source.

01h 2 / 256 Duty with PWM1 clock source.

02h 3 / 256 Duty with PWM1 clock source.

:

:

FEh 255 / 256 Duty with PWM1 clock source.

FFh 256 / 256 Duty with PWM1 clock source.

0 RW

TOPWAY

LCD Module User Manual LMT056DIDFWD-AEN

URL: www.topwaydisplay.com

www.topwaysz.com Document Name: LMT056DIDFWD-AEN-Manual-Rev0.2

Page:

20

of

32

REG[8Ch] PWM2 Control Register (P2CR)

Bit

Description

Default

Access

7

PWM2 Enable

0 : Disable, PWM_OUT level depends on P2CR bit6.

1 : Enable.

0 RW

6

PWM2 Disable Level

0 : PWM2_OUT is Normal L when PWM disable or Sleep

mode.

1 : PWM2_OUT is Normal H when PWM disable or Sleep

mode.

The bit is only usable when P2CR bit 4 is 0

0 RW

5 Reserved 0 RO

4

PWM2 Function Selection

0 : PWM2 function.

1 : PWM2 output a signal which is the same with system clock.

PWM2 = SYS_CLK / 16 .

0 RW

3-0

PWM2 Clock Source Divide Ratio

0000b : SYS_CLK / 1 1000b : SYS_CLK / 256

0001b : SYS_CLK / 2 1001b : SYS_CLK / 512

0010b : SYS_CLK / 4 1010b : SYS_CLK / 1024

0011b : SYS_CLK / 8 1011b : SYS_CLK / 2048

0100b : SYS_CLK / 16 1100b : SYS_CLK / 4096

0101b : SYS_CLK / 32 1101b : SYS_CLK / 8192

0110b : SYS_CLK / 64 1110b : SYS_CLK / 16384

0111b : SYS_CLK / 128 1111b : SYS_CLK / 32768

For example, if the system clock is 20MHz and Bit[3:0]

=0010b,then the clock source of PWM2 is 5MHz.

0 RW

REG[8Dh] PWM2 Control Register (P2DCR)

Bit

Description

Default

Access

7-0

PWM Cycle Duty Selection Bit

00h 1 / 256 Duty with PWM2 clock source.

01h 2 / 256 Duty with PWM2 clock source.

02h 3 / 256 Duty with PWM2 clock source.

:

:

FEh 255 / 256 Duty with PWM2 clock source.

FFh 256 / 256 Duty with PWM2 clock source.

0 RW

REG[8Eh] Memory Clear Control Register (MCLR)

Bit

Description

Default

Access

7

Memory Clear Function

0 : End or Stop. When write 0 to this bit RA8875 will stop

the Memory clear function. Or if read back this bit is

0, it indicates than Memory clear function is complete.

1 : Start the memory clear function.

0 RW

6

Memory Clear Area Setting

0 : Clear the full window. (Please refer to the setting of

REG[14h], [19h], [1Ah])

1 : Clear the active window(Please refer to the setting

of REG[30h~37h]). The layer to be cleared is according to

the setting REG[41h] Bit0.

0 RW

5-0

NA 0 RO

Table of contents

Other Topway Control Unit manuals

Topway

Topway LM2088RCW User manual

Topway

Topway HMT028ATB-C User manual

Topway

Topway LM6020FCW-2 User manual

Topway

Topway LMT070DICFWD-NJN User manual

Topway

Topway LMT050DNCFWU-NWN User manual

Topway

Topway LM6093ACW User manual

Topway

Topway LM12864LFC User manual

Topway

Topway LM8053-1 User manual

Topway

Topway LMT035KDH03-NHN User manual

Topway

Topway LMT080TDGP01 User manual