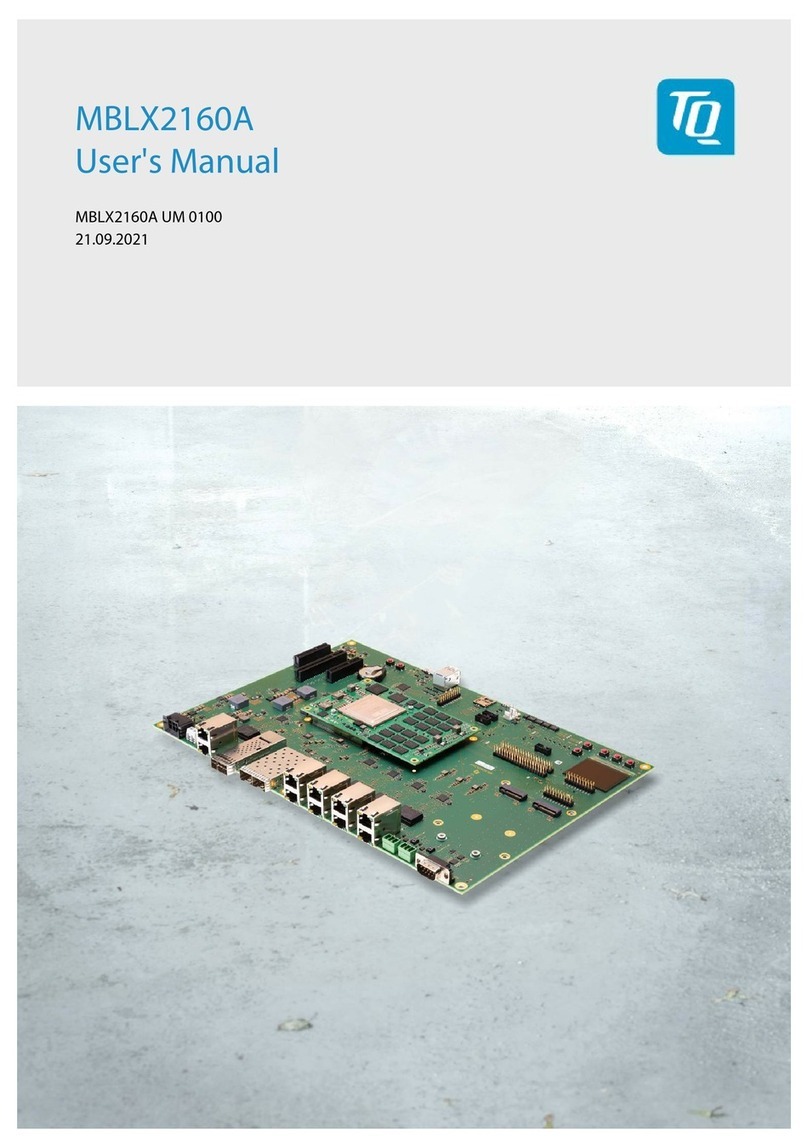

TQ TQMa65 Series User manual

TQMa65xx

Preliminary User's Manual

TQMa65xx UM 0001

07.02.2021

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page i

TABLE OF CONTENTS

1. ABOUT THIS MANUAL......................................................................................................................................................................................1

1.1 Copyright and license expenses..................................................................................................................................................................1

1.2 Registered trademarks ....................................................................................................................................................................................1

1.3 Disclaimer ............................................................................................................................................................................................................1

1.4 Imprint...................................................................................................................................................................................................................1

1.5 Tips on safety......................................................................................................................................................................................................2

1.6 Symbols and typographic conventions....................................................................................................................................................2

1.7 Handling and ESD tips.....................................................................................................................................................................................2

1.8 Naming of signals..............................................................................................................................................................................................3

1.9 Further applicable documents / presumed knowledge.....................................................................................................................3

2. BRIEF DESCRIPTION ..........................................................................................................................................................................................4

2.1 Block diagram AM65xx....................................................................................................................................................................................5

2.2 Key functions and characteristics................................................................................................................................................................5

3. ELECTRONICS......................................................................................................................................................................................................6

3.1 Interfaces to other systems and devices...................................................................................................................................................6

3.1.1 AM65xx pin multiplexing...............................................................................................................................................................................6

3.1.2 Pinout TQMa65xx..............................................................................................................................................................................................7

3.2 System components .....................................................................................................................................................................................12

3.2.1 AM65xx CPU.....................................................................................................................................................................................................12

3.2.1.1 Boot Mode ........................................................................................................................................................................................................12

3.2.1.2 MCU Boot Mode Selection..........................................................................................................................................................................13

3.2.1.3 Boot Mode pin mapping .............................................................................................................................................................................14

3.2.2 Memory..............................................................................................................................................................................................................16

3.2.2.1 DDR4 SDRAM...................................................................................................................................................................................................16

3.2.2.2 eMMC..................................................................................................................................................................................................................16

3.2.2.3 OSPI NOR flash ................................................................................................................................................................................................17

3.2.2.4 EEPROM .............................................................................................................................................................................................................17

3.2.2.5 EEPROM with temperature sensor...........................................................................................................................................................18

3.2.3 RTC.......................................................................................................................................................................................................................19

3.2.4 Secure Element ...............................................................................................................................................................................................19

3.2.5 I2C devices.........................................................................................................................................................................................................20

3.2.6 Board Controller .............................................................................................................................................................................................20

3.2.7 Reset....................................................................................................................................................................................................................20

3.3 Power..................................................................................................................................................................................................................21

3.3.1 Power supply ...................................................................................................................................................................................................21

3.3.2 TQMa65xx power-up sequencing............................................................................................................................................................21

3.3.3 Power consumption......................................................................................................................................................................................21

3.3.4 Power modes...................................................................................................................................................................................................21

4. MECHANICS......................................................................................................................................................................................................22

4.1 Connectors .......................................................................................................................................................................................................22

4.2 Dimensions.......................................................................................................................................................................................................23

4.3 Component placement................................................................................................................................................................................25

4.4 Protection against external effects..........................................................................................................................................................26

4.5 Thermal management..................................................................................................................................................................................26

4.6 Structural requirements...............................................................................................................................................................................26

4.7 Notes of treatment ........................................................................................................................................................................................26

5. SOFTWARE........................................................................................................................................................................................................26

6. SAFETY REQUIREMENTS AND PROTECTIVE REGULATIONS ............................................................................................................27

6.1 EMC .....................................................................................................................................................................................................................27

6.2 ESD.......................................................................................................................................................................................................................27

6.3 Operational safety and personal security..............................................................................................................................................27

6.4 Shock and vibration ......................................................................................................................................................................................27

6.5 Climate and operational conditions........................................................................................................................................................28

6.6 Reliability and service life............................................................................................................................................................................28

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page ii

TABLE OF CONTENTS (continued)

7. ENVIRONMENT PROTECTION.....................................................................................................................................................................29

7.1 RoHS....................................................................................................................................................................................................................29

7.2 WEEE®.................................................................................................................................................................................................................29

7.3 REACH®..............................................................................................................................................................................................................29

7.4 EuP.......................................................................................................................................................................................................................29

7.5 Battery ................................................................................................................................................................................................................29

7.6 Packaging..........................................................................................................................................................................................................29

7.7 Other entries ....................................................................................................................................................................................................29

8. APPENDIX..........................................................................................................................................................................................................30

8.1 Acronyms and definitions...........................................................................................................................................................................30

8.2 References ........................................................................................................................................................................................................32

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page iii

TABLE DIRECTORY

Table 1: Terms and conventions ..................................................................................................................................................................................2

Table 2: Pinout TQMa65xx connector X1..................................................................................................................................................................7

Table 3: Pinout TQMa65xx connector X2..................................................................................................................................................................9

Table 4: Pinout TQMa65xx connector X3...............................................................................................................................................................11

Table 5: MCU_BOOTMODE Pin Mapping...............................................................................................................................................................13

Table 6: PLL Reference Clock Selection...................................................................................................................................................................13

Table 7: POST Selection ................................................................................................................................................................................................13

Table 8: 1.8V LDO Configuration...............................................................................................................................................................................13

Table 9: BOOTMODE Pin Mapping ...........................................................................................................................................................................14

Table 10: Primary Boot Mode Selection ....................................................................................................................................................................14

Table 11: Backup Mode Selection ...............................................................................................................................................................................14

Table 12: Min Pin Configuration ..................................................................................................................................................................................15

Table 13: Primary Boot Mode Configuration...........................................................................................................................................................15

Table 14: Backup Boot Mode Configuration ...........................................................................................................................................................15

Table 15: Unsupported eMMC modes.......................................................................................................................................................................16

Table 16: Temperature sensor SE97BTP....................................................................................................................................................................18

Table 17: TQMa65xx WKUP_I2C addresses..............................................................................................................................................................20

Table 18: TQMa65xx connectors..................................................................................................................................................................................22

Table 19: Carrier board mating connectors.............................................................................................................................................................22

Table 20: TQMa65xx, heights .......................................................................................................................................................................................23

Table 21: Labels on TQMa65xx.....................................................................................................................................................................................25

Table 22: Shock resistance .............................................................................................................................................................................................27

Table 23: Vibration resistance.......................................................................................................................................................................................27

Table 24: Climate and operational conditions –25 °C to +85 °C ......................................................................................................................28

Table 25: Climate and operational conditions –40 °C to +85 °C ......................................................................................................................28

Table 26: Acronyms ..........................................................................................................................................................................................................30

Table 27: Further applicable documents..................................................................................................................................................................32

ILLUSTRATION DIRECTORY

Figure 1: Block diagram AM65xx CPU family.............................................................................................................................................................5

Figure 2: Block diagram TQMa65xx ..............................................................................................................................................................................6

Figure 3: Block diagram MMCSD interface..............................................................................................................................................................16

Figure 4:Block diagram OSPI interface.....................................................................................................................................................................17

Figure 5: Block diagram EEPROM................................................................................................................................................................................17

Figure 6: Block diagram temperature sensor interface ......................................................................................................................................18

Figure 7: Block diagram RTC.........................................................................................................................................................................................19

Figure 8: Block diagram Secure Element .................................................................................................................................................................19

Figure 9: Block diagram I2C devices ...........................................................................................................................................................................20

Figure 10: TQMa65xx dimensions, side view ............................................................................................................................................................23

Figure 11: TQMa65xx CPU position, top view...........................................................................................................................................................24

Figure 12: TQMa65xx dimensions, top view through TQMa65xx .....................................................................................................................24

Figure 13: TQMa65xx, component placement top.................................................................................................................................................25

Figure 14: TQMa65xx, component placement bottom.........................................................................................................................................25

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page iv

REVISION HISTORY

Rev. Date Name Pos. Modification

0001 07.02.2021 Petz Initial release

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 1

1.

ABOUT THIS MANUAL

1.1

Copyright and license expenses

Copyright protected © 2021 by TQ-Systems GmbH.

This Preliminary User's Manual may not be copied, reproduced, translated, changed or distributed, completely or partially in

electronic, machine readable, or in any other form without the written consent of TQ-Systems GmbH.

The drivers and utilities for the components used as well as the BIOS are subject to the copyrights of the respective

manufacturers. The licence conditions of the respective manufacturer are to be adhered to.

Bootloader-licence expenses are paid by TQ-Systems GmbH and are included in the price.

Licence expenses for the operating system and applications are not taken into consideration and must be calculated / declared

separately.

1.2

Registered trademarks

TQ-Systems GmbH aims to adhere to copyrights of all graphics and texts used in all publications, and strives to use original

or license-free graphics and texts.

All brand names and trademarks mentioned in this Preliminary User's Manual, including those protected by a third party, unless

specified otherwise in writing, are subjected to the specifications of the current copyright laws and the proprietary laws of the

present registered proprietor without any limitation. One should conclude that brand and trademarks are rightly protected by a

third party.

1.3

Disclaimer

TQ-Systems GmbH does not guarantee that the information in this Preliminary User's Manual is up-to-date, correct, complete or

of good quality. Nor does TQ-Systems GmbH assume guarantee for further usage of the information. Liability claims against TQ-

Systems GmbH, referring to material or non-material related damages caused, due to usage or non-usage of the information

given in this Preliminary User's Manual, or due to usage of erroneous or incomplete information, are exempted, as long as there

is no proven intentional or negligent fault of TQ-Systems GmbH.

TQ-Systems GmbH explicitly reserves the rights to change or add to the contents of this Preliminary User's Manual or parts of it

without special notification.

Important Notice:

Before using the MBa65xx or parts of the schematics of the MBa65xx, you must evaluate it and determine if it is suitable for your

intended application. You assume all risks and liability associated with such use. TQ-Systems GmbH makes no other warranties

including, but not limited to, any implied warranty of merchantability or fitness for a particular purpose. Except where prohibited

by law, TQ-Systems GmbH will not be liable for any indirect, special, incidental or consequential loss or damage arising from the

usage of the MBa65xx or schematics used, regardless of the legal theory asserted.

1.4

Imprint

TQ-Systems GmbH

Gut Delling, Mühlstraße 2

D-82229 Seefeld

Tel: +49 8153 9308–0

Fax: +49 8153 9308–4223

E-Mail: Info@TQ-Group

Web: TQ-Group

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 2

1.5

Tips on safety

Improper or incorrect handling of the product can substantially reduce its life span.

1.6

Symbols and typographic conventions

Table 1: Terms and conventions

Symbol Meaning

This symbol represents the handling of electrostatic-sensitive modules and / or components. These

components are often damaged / destroyed by the transmission of a voltage higher than about 50 V.

A human body usually only experiences electrostatic discharges above approximately 3,000 V.

This symbol indicates the possible use of voltages higher than 24 V.

Please note the relevant statutory regulations in this regard.

Non-compliance with these regulations can lead to serious damage to your health and may damage

or destroy the component.

This symbol indicates a possible source of danger.

Ignoring the instructions described can cause health damage, or damage the hardware.

This symbol represents important details or aspects for working with TQ-products.

Command

A font with fixed-width is used to denote commands, contents, file names, or menu items.

1.7

Handling and ESD tips

General handling of your TQ-products

The TQ-product may only be used and serviced by certified personnel who have taken note of the

information, the safety regulations in this document and all related rules and regulations.

A general rule is not to touch the TQ-product during operation. This is especially important when

switching on, changing jumper settings or connecting other devices without ensuring beforehand

that the power supply of the system has been switched off.

Violation of this guideline may result in damage / destruction of the TQMa65xx and be dangerous

to your health.

Improper handling of your TQ-product would render the guarantee invalid.

Proper ESD handling

The electronic components of your TQ-product are sensitive to electrostatic discharge (ESD).

Always wear antistatic clothing, use ESD-safe tools, packing materials etc., and operate your TQ-

product in an ESD-safe environment. Especially when you switch modules on, change jumper settings,

or connect other devices.

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 3

1.8

Naming of signals

A hash mark (#) at the end of the signal name indicates a low-active signal.

Example: RESET#

If a signal can switch between two functions and if this is noted in the name of the signal, the low-active function is marked with

a hash mark and shown at the end.

Example: C / D#

If a signal has multiple functions, the individual functions are separated by slashes when they are important for the wiring.

The identification of the individual functions follows the above conventions.

Example: WE2# / OE#

1.9

Further applicable documents / presumed knowledge

•

Specifications and manual of the modules used:

These documents describe the service, functionality and special characteristics of the module used (incl. BIOS).

•

Specifications of the components used:

The manufacturer’s specifications of the components used, for example CompactFlash cards, are to be taken note of.

They contain, if applicable, additional information that must be taken note of for safe and reliable operation. These

documents are stored at TQ-Systems GmbH.

•

Chip errata:

It is the user's responsibility to make sure all errata published by the manufacturer of each component are taken note of.

The manufacturer’s advice should be followed.

•

Software behaviour:

No warranty can be given, nor responsibility taken for any unexpected software behaviour due to deficient components.

•

General expertise:

Expertise in electrical engineering / computer engineering is required for the installation and the use of the device.

The following documents are required to fully comprehend the following contents:

•MBa65xx circuit diagram

•MBa65xx User’s Manual

•AM65xx Data Sheet

•AM65xx Reference Manual

•U-Boot documentation: www.denx.de/wiki/U-Boot/Documentation

•Yocto documentation: www.yoctoproject.org/docs/

•TQ-Support Wiki: Support-Wiki TQMa65xx

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 4

2.

BRIEF DESCRIPTION

This Preliminary User's Manual describes the hardware of the TQMa65xx Rev. 01xx, in combination with the MBa65xx and refers

to some software settings. The MBa65xx serves as an evaluation board for the TQMa65xx.

A certain TQMa65xx version does not necessarily provide all features described in this Preliminary User's Manual.

This Preliminary User's Manual does also not replace the TI AM65xx Reference Manual (2).

The CPU derivatives feature ARM®Cortex-A53 cores, and two ARM®Cortex-R5F coprocessors. The CPUs also provide a 3D GPU.

The TQMa65xx is a universal Minimodule based on these TI ARM®Cortex-A53 AM65xx CPUs, see also (1), (2).

An AM65xx Cortex-A53 core typically operates at 1.1 GHz.

The TQMa65xx extends the TQ-Systems GmbH product range and offers an outstanding computing performance.

A suitable AM65xx derivative (AM6526, AM6527, AM6528, AM6546, or AM6548) can be selected for each requirement.

All essential CPU signals are routed to the connectors. There are therefore no restrictions for customers using the TQMa65xx

with respect to an integrated customised design. All essential components like CPU, DDR4 SDRAM, eMMC, RTC, EEPROM, power

supply, and power management are already integrated on the TQMa65xx.

The main features of the TQMa65xx are:

•TI AM65xx CPU with up to 4 × ARM®Cortex-A53 and 2 × ARM®Cortex-R5F cores

•CPU derivatives: AM6526, AM6527, AM6528, AM6546, or AM6548

•Up to 4 Gbyte DDR4 SDRAM, optional additional ECC

•Up to 64 Gbyte eMMC NAND flash

•Up to 512 Mbyte OSPI NOR flash (optional)

•64 Kbit EEPROM

•EEPROM + temperature sensor

•On-board RTC

•Secure Element (optional)

•All essential AM65XX signals are routed to the TQMa65xx connectors

•Extended temperature range

•5 V single supply voltage

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 5

2.1

Block diagram AM65xx

Figure 1: Block diagram AM65xx CPU family

(Source: Texas Instruments)

2.2

Key functions and characteristics

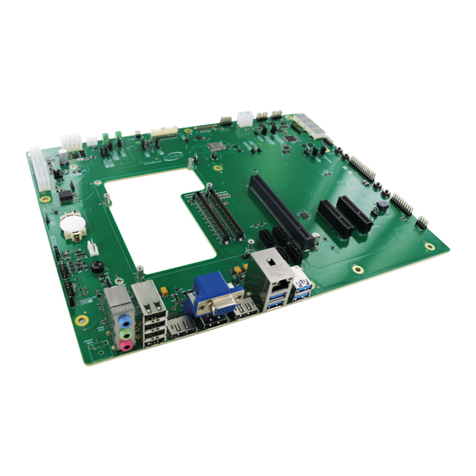

The following components are implemented on the TQMa65xx:

•AM6526, AM6527, AM6528, AM6546, or AM6548

•DDR4 SDRAM

•eMMC NAND flash

•OSPI NOR flash

•EEPROM

•EEPROM + Temperature sensor

•RTC

•Reset structure

•Power supply with Power Sequencing (single 5 V supply)

•Voltage monitoring

•Boot configuration

•Three connectors (2 × 220 pins, 1 × 120 pins)

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 6

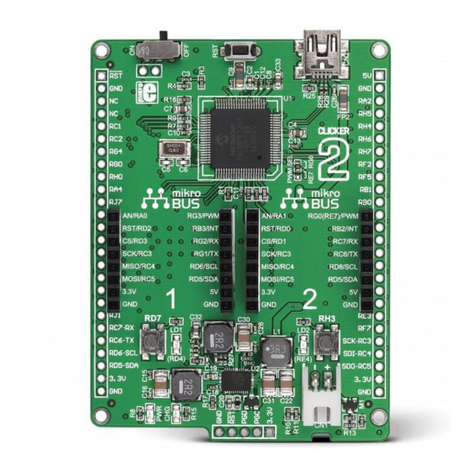

3.

ELECTRONICS

The information provided in this Preliminary User's Manual is only valid in connection with the tailored boot loader,

which is preinstalled on the TQMa65xx, and the BSP provided by TQ-Systems, see also chapter 5.

Figure 2: Block diagram TQMa65xx

3.1

Interfaces to other systems and devices

3.1.1 AM65xx pin multiplexing

When using the AM65XX signals, the multiple pin configurations by different AM65xx-internal function units must be taken note

of. TI provides a tool showing the multiplexing and simplifies the selection and configuration (TI Pin Mux Tool).

The pin assignment listed in Table 2 to Table 4 refers to the corresponding BSP provided by TQ-Systems

in combination with the MBa65xx.

The electrical and pin characteristics are to be taken from the AM65xx Data Sheet (1), and the AM65xx Reference Manual (2).

Attention: Destruction or malfunction, AM65xx pin multiplexing, TQMa65xx reserved pins

Depending on the configuration, many AM65xx balls can provide several different functions.

Please take note of the information in the AM65xx Reference Manual (2), and the AM65xx Errata (3)

concerning the configuration of these pins before integration or start-up of your carrier board.

Improper programming by operating software can cause malfunctions, deterioration or destruction

of the TQMa65xx. Pins marked with “NC” must never be connected and have to be left open.

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 7

3.1.2 Pinout TQMa65xx

Table 2: Pinout TQMa65xx connector X1

AM65xx

Dir. Level Group Signal Pin Signal Group Level Dir. AM65x

– P 0 V Ground DGND A1 B1 DGND Ground 0 V P –

– P 5 V Power VIN A2 B2 VIN Power 5 V P –

– P 5 V Power VIN A3 B3 VIN Power 5 V P –

– P 5 V Power VIN A4 B4 VIN Power 5 V P –

– P 5 V Power VIN A5 B5 VIN Power 5 V P –

– P 5 V Power VIN A6 B6 VIN Power 5 V P –

–

P

5 V

Power

VIN

A7

B7

VIN

Power

5 V

P

–

– P 5 V Power VIN A8 B8 VIN Power 5 V P –

– P 5 V Power VIN A9 B9 VIN Power 5 V P –

– P 0 V Ground DGND A10 B10 VIN Power 5 V P –

– P 0 V Ground DGND A11 B11 DGND Ground 0 V P –

– P 0 V Ground DGND A12 B12 DGND Ground 0 V P –

– P 0 V Ground DGND A13 B13 DGND Ground 0 V P –

– P 0 V Ground DGND A14 B14 DGND Ground 0 V P –

– P 0 V Ground DGND A15 B15 DGND Ground 0 V P –

– P 0 V Ground DGND A16 B16 DGND Ground 0 V P –

– P 0 V Ground DGND A17 B17 DGND Ground 0 V P –

– P 0 V Ground DGND A18 B18 VDD_SD Power 3.3 V P –

–

P

0 V

Ground

DGND

A19

B19

V_BAT

Power

3.3 V

P

–

– P 1.8 V Power VCC1V8L1 A20 B20 VCC3V3S Power 1.8 / 3.3 V P –

– P 0 V Ground DGND A21 B21 DGND Ground 0 V P –

– P 1.8 V Power VCC1V8 A22 B22 VCC3V3 Power 3.3 V P –

– P 1.8 V Power VCC1V8 A23 B23 VCC3V3 Power 3.3 V P –

– P 0 V Ground DGND A24 B24 DGND Ground 0 V P –

– I 3.3 V JTAG nSRST_JTAG# A25 B25 IO1_RES Factory Test 3.3 V I/O –

– I 1.8 V SYSTEM POR#_MB A26 B26 IO2_RES Factory Test 3.3 V I/O –

C19 O 1.8 / 3.3 V SYSTEM POR#_OUT A27 B27 IO3_RES Factory Test 3.3 V I/O –

– P 0 V Ground DGND A28 B28 RES_BC# Factory Test 3.3 V I –

AH10 I 1.8 V SERDES SERDES1_RXP A29 B29 SWD_CLK Factory Test 3.3 V I –

AG9 I 1.8 V SERDES SERDES1_RXN A30 B30 SWD_DIO Factory Test 3.3 V I/O –

–

P

0 V

Ground

DGND

A31

B31

DGND

Ground

0 V

P

–

AH9 O 1.8 V SERDES SERDES1_TXN_C A32 B32 DGND Ground 0 V P –

AG8 O 1.8 V SERDES SERDES1_TXP_C A33 B33 SERDES0_PCIe_REFCLK0P SERDES 1.8 V O AF10

– P 0 V Ground DGND A34 B34 SERDES0_PCIe_REFCLK0N SERDES 1.8 V O AF9

AE9 O 1.8 V SERDES SERDES1_PCIe_REFCLK1P A35 B35 DGND Ground 0 V P –

AE8 O 1.8 V SERDES SERDES1_PCIe_REFCLK1N A36 B36 SERDES0_RXN SERDES 1.8 V I AH3

– P 0 V Ground DGND A37 B37 SERDES0_RXP SERDES 1.8 V I AG2

AH7 O 1.8 V SERDES SERDES1_REFCLKP A38 B38 DGND Ground 0 V P –

AH6 O 1.8 V SERDES SERDES1_REFCLKN A39 B39 SERDES0_TXP_C SERDES 1.8 V O AG3

– P 0 V Ground DGND A40 B40 SERDES0_TXN_C SERDES 1.8 V O AH4

– P 0 V Ground DGND A41 B41 DGND Ground 0 V P –

AD13 I/O 1.8 / 3.3 V SPI SPI0_D1 A42 B42 SERDES0_REFCLKP SERDES 1.8 V O AG6

AE13 I/O 1.8 / 3.3 V SPI SPI0_D0 A43 B43 SERDES0_REFCLKN SERDES 1.8 V O AG5

– P 0 V Ground DGND A44 B44 DGND Ground 0 V P –

AG12 I/O 1.8 / 3.3 V SPI SPI1_CS1 A45 B45 UART0_CTS# UART 1.8 / 3.3 V I AG11

AD12 I/O 1.8 / 3.3 V SPI SPI1_CS0 A46 B46 UART0_RXD UART 1.8 / 3.3 V I AF11

– P 0 V Ground DGND A47 B47 UART0_TXD UART 1.8 / 3.3 V O AE11

AH13 I/O 1.8 / 3.3 V SPI SPI0_CLK A48 B48 UART0_RST# UART 1.8 / 3.3 V O AD11

– P 0 V Ground DGND A49 B49 DGND Ground 0 V P –

AH12 I/O 1.8 / 3.3 V SPI SPI1_CLK A50 B50 USB0_VBUS_R USB VDDA_3P3_USB

P AE7

– P 0 V Ground DGND A51 B51 DGND Ground 0 V – –

AG13 I/O 1.8 / 3.3 V SPI SPI0_CS0 A52 B52 USB0_ID USB 3.3 V – AF1

AF13 I/O 1.8 / 3.3 V SPI SPI0_CS1 A53 B53 USB0_DRVVBUS USB 1.8 / 3.3 V – AD9

–

P

0 V

Ground

DGND

A54

B54

DGND

Ground

0 V

P

–

AE12 I/O 1.8 / 3.3 V SPI SPI1_D0 A55 B55 USB0_DM USB 3.3 V – AE2

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 8

3.1.2 Pinout TQMa65xx (continued)

Table 2: Pinout TQMa65xx connector X1 (continued)

AM65xx

Dir. Level Group Signal Pin Signal Group Level Dir. AM65x

AF12 I/O 1.8 / 3.3 V SPI SPI1_D1 A56 B56 USB0_DP USB 3.3 V – AF1

– P 0 V Ground DGND A57 B57 DGND Ground 0 V P –

AC3 O 1.8 / 3.3 V CAN MCU_MCAN1_TX A58 B58 USB1_VBUS_R USB VDDA_3P3_USB – AF6

AD3 I 1.8 / 3.3 V CAN MCU_MCAN1_RX A59 B59 USB1_ID USB 3.3 V – AF5

– P 0 V Ground DGND A60 B60 DGND Ground 0 V P –

– P 0 V Ground DGND A61 B61 USB1_DRVVBUS USB 1.8 / 3.3 V – AC8

W2

I

1.8 / 3.3 V

CAN

MCU_MCAN0_RX

A62

B62

DGND

Ground

0 V

P

–

W1 O 1.8 / 3.3 V CAN MCU_MCAN0_TX A63 B63 USB1_DP USB 3.3 V – AE1

– P 0 V Ground DGND A64 B64 USB1_DM USB 3.3 V – AD2

AD6 I/O/D

1.8 / 3.3 V I2C WKUP_I2C_SDA A65 B65 DGND Ground 0 V P –

AC7 I/O/D

1.8 / 3.3 V I2C WKUP_I2C_SCL A66 B66 WKUP_GPIO0_11 GPIO 1.8 / 3.3 V I/O AB2

– P 0 V Ground DGND A67 B67 WKUP_GPIO0_10 GPIO 1.8 / 3.3 V I/O AB3

AD7 I/O/D

1.8 / 3.3 V I2C MCU_I2C_SDA A68 B68 WKUP_GPIO0_9 GPIO 1.8 / 3.3 V I/O AB4

AD8 I/O/D

1.8 / 3.3 V I2C MCU_I2C_SCL A69 B69 WKUP_GPIO0_8 GPIO 1.8 / 3.3 V I/O AC5

– P 0 V Ground DGND A70 B70 DGND Ground 0 V P –

AC1 O 1.8 / 3.3 V UART WKUP_UART0_RTSn A71 B71 WKUP_GPIO0_3 GPIO 1.8 / 3.3 V I/O AD1

AC2 I 1.8 / 3.3 V UART WKUP_UART0_CTSn A72 B72 WKUP_GPIO0_2 GPIO 1.8 / 3.3 V I/O AE3

AB5 O 1.8 / 3.3 V UART WKUP_UART0_TXD A73 B73 WKUP_GPIO0_1 GPIO 1.8 / 3.3 V I/O AF3

AB1

I

1.8 / 3.3 V

UART

WKUP_UART0_RXD

A74

B74

WKUP_GPIO0_0

GPIO

1.8 / 3.3 V

I/O

AF4

– P 0 V Ground DGND A75 B75 WKUP_GPIO0_33 GPIO 1.8 / 3.3 V I/O N3

Y2 I/O 1.8 / 3.3 V SPI MCU_SPI0_D1 A76 B76 DGND Ground 0 V P –

Y3 I/O 1.8 / 3.3 V SPI MCU_SPI0_D0 A77 B77 DGND Ground 0 V P –

Y4 I/O 1.8 / 3.3 V SPI MCU_SPI0_CS0 A78 B78 DGND Ground 0 V P –

Y1 I/O 1.8 / 3.3 V SPI MCU_SPI0_CLK A79 B79 DGND Ground 0 V P –

– P 0 V Ground DGND A80 B80 DGND Ground 0 V P –

N2 I/O 1.8 / 3.3 V GPIO WKUP_GPIO0_32 A81 B81 DGND Ground 0 V P –

P1 I/O 1.8 / 3.3 V GPIO WKUP_GPIO0_31 A82 B82 MCU_POR#_OUT SYSTEM 1.8 / 3.3 V O V2

P3 I/O 1.8 / 3.3 V GPIO WKUP_GPIO0_28 A83 B83 MCU_WARM_RESET#_OUT SYSTEM 1.8 / 3.3 V O V3

P2 I/O 1.8 / 3.3 V GPIO WKUP_GPIO0_27 A84 B84 DGND Ground 0 V P –

R1 I/O 1.8 / 3.3 V GPIO WKUP_GPIO0_26 A85 B85 MCU_RESET#_MB SYSTEM 1.8 / 3.3 V I W4

T1

I/O

1.8 / 3.3 V

GPIO

WKUP_GPIO0_25

A86

B86

MCU_SAFETY_ERROR#

SYSTEM

1.8 / 3.3 V

I/O

W3

– P 0 V Ground DGND A87 B87 DGND Ground 0 V P –

D19 O 1.8 V SYSTEM WARM_RESET#_OUT A88 B88 MCU_UART0_TXD UART 1.8 / 3.3 V O P5

F17 I 1.8 / 3.3 V SYSTEM WARM_RESET#_MB A89 B89 MCU_UART0_RXD UART 1.8 / 3.3 V I P4

– P 0 V Ground DGND A90 B90 DGND Ground 0 V P –

N1 I/O 1.8 / 3.3 V RGMII MCU_RGMII1_TXC A91 B91 MCU_RGMII1_RXC RGMII 1.8 / 3.3 V I M1

N4 O 1.8 / 3.3 V RGMII MCU_RGMII1_TX_CTL A92 B92 MCU_RGMII1_RX_CTL RGMII 1.8 / 3.3 V I N5

M2 O 1.8 / 3.3 V RGMII MCU_RGMII1_TD3 A93 B93 MCU_RGMII1_RD0 RGMII 1.8 / 3.3 V I L6

M3 O 1.8 / 3.3 V RGMII MCU_RGMII1_TD2 A94 B94 MCU_RGMII1_RD1 RGMII 1.8 / 3.3 V I M6

M4 O 1.8 / 3.3 V RGMII MCU_RGMII1_TD1 A95 B95 MCU_RGMII1_RD2 RGMII 1.8 / 3.3 V I L5

M5 O 1.8 / 3.3 V RGMII MCU_RGMII1_TD0 A96 B96 MCU_RGMII1_RD3 RGMII 1.8 / 3.3 V I L2

– P 0 V Ground DGND A97 B97 DGND Ground 0 V P –

L1 O 1.8 / 3.3 V RGMII MCU_RGMII1_MDC A98 B98 DGND Ground 0 V P –

L4 I/O 1.8 / 3.3 V RGMII MCU_RGMII1_MDIO A99 B99 SOC_SAFETY_ERROR# SYSTEM 1.8 V I/O E20

– P 0 V Ground DGND A100 B100 DGND Ground 0 V P –

– P 0 V Ground DGND A101 B101 DGND Ground 0 V P –

H4 A 1.8 V ADC MCU_ADC1_AIN7 A102 B102 MCU_ADC0_AIN7 ADC 1.8 V A J6

G3 A 1.8 V ADC MCU_ADC1_AIN6 A103 B103 MCU_ADC0_AIN6 ADC 1.8 V A J2

G5 A 1.8 V ADC MCU_ADC1_AIN5 A104 B104 MCU_ADC0_AIN5 ADC 1.8 V A J4

F5 A 1.8 V ADC MCU_ADC1_AIN4 A105 B105 MCU_ADC0_AIN4 ADC 1.8 V A K4

H5 A 1.8 V ADC MCU_ADC1_AIN3 A106 B106 MCU_ADC0_AIN3 ADC 1.8 V A J5

G4 A 1.8 V ADC MCU_ADC1_AIN2 A107 B107 MCU_ADC0_AIN2 ADC 1.8 V A J1

G6 A 1.8 V ADC MCU_ADC1_AIN1 A108 B108 MCU_ADC0_AIN1 ADC 1.8 V A J3

F4

A

1.8 V

ADC

MCU_ADC1_AIN0

A109

B109

MCU_ADC0_AIN0

ADC

1.8 V

A

K5

– P 0 V Ground DGND A110 B110 DGND Ground 0 V P –

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 9

3.1.2 Pinout TQMa65xx (continued)

Table 3: Pinout TQMa65xx connector X2

AM65xx

Dir. Level Group Signal Pin Signal Group Level Dir. AM65x

– P 0 V Ground DGND A1 B1 DGND Ground 0 V P –

AE16 O 1.8 / 3.3 V RGMII PRG2_RGMII1_TD3 A2 B2 PRG2_RGMII2_TD3 RGMII 1.8 / 3.3 V O AD14

AF16 O 1.8 / 3.3 V RGMII PRG2_RGMII1_TD2 A3 B3 PRG2_RGMII2_TD2 RGMII 1.8 / 3.3 V O AC15

AG16 O 1.8 / 3.3 V RGMII PRG2_RGMII1_TD1 A4 B4 PRG2_RGMII2_TD1 RGMII 1.8 / 3.3 V O AF14

AH16 O 1.8 / 3.3 V RGMII PRG2_RGMII1_TD0 A5 B5 PRG2_RGMII2_TD0 RGMII 1.8 / 3.3 V O AD15

– P 0 V Ground DGND A6 B6 DGND Ground 0 V P –

AG18

I

1.8 / 3.3 V

RGMII

PRG2_RGMII1_RD3

A7

B7

PRG2_RGMII2_RD3

RGMII

1.8 / 3.3 V

I

AH14

AH17 I 1.8 / 3.3 V RGMII PRG2_RGMII1_RD2 A8 B8 PRG2_RGMII2_RD2 RGMII 1.8 / 3.3 V I AD17

AE18 I 1.8 / 3.3 V RGMII PRG2_RGMII1_RD1 A9 B9 PRG2_RGMII2_RD1 RGMII 1.8 / 3.3 V I AC16

AF18 I 1.8 / 3.3 V RGMII PRG2_RGMII1_RD0 A10 B10 PRG2_RGMII2_RD0 RGMII 1.8 / 3.3 V I AH15

– P 0 V Ground DGND A11 B11 DGND Ground 0 V P –

AG17 I 1.8 / 3.3 V RGMII PRG2_RGMII1_RX_CTL A12 B12 PRG2_RGMII2_RX_CTL RGMII 1.8 / 3.3 V I AG14

AF17 I 1.8 / 3.3 V RGMII PRG2_RGMII1_RXC A13 B13 PRG2_RGMII2_RXC RGMII 1.8 / 3.3 V I AG15

AD16 I/O 1.8 / 3.3 V RGMII PRG2_RGMII1_TXC A14 B14 PRG2_RGMII2_TXC RGMII 1.8 / 3.3 V I/O AE14

AE17 O 1.8 / 3.3 V RGMII PRG2_RGMII1_TX_CTL A15 B15 PRG2_RGMII2_TX_CTL RGMII 1.8 / 3.3 V O AC17

– P 0 V Ground DGND A16 B16 DGND Ground 0 V P –

AG19 O 1.8 / 3.3 V RGMII PRG1_RGMII2_TD3 A17 B17 PRG1_RGMII1_TD3 RGMII 1.8 / 3.3 V O AD19

AH19 O 1.8 / 3.3 V RGMII PRG1_RGMII2_TD2 A18 B18 PRG1_RGMII1_TD2 RGMII 1.8 / 3.3 V O AG20

AF19

O

1.8 / 3.3 V

RGMII

PRG1_RGMII2_TD1

A19

B19

PRG1_RGMII1_TD1

RGMII

1.8 / 3.3 V

O

AH21

AE20 O 1.8 / 3.3 V RGMII PRG1_RGMII2_TD0 A20 B20 PRG1_RGMII1_TD0 RGMII 1.8 / 3.3 V O AH20

– P 0 V Ground DGND A21 B21 DGND Ground 0 V P –

AH22 I 1.8 / 3.3 V RGMII PRG1_RGMII2_RD3 A22 B22 PRG1_RGMII1_RD3 RGMII 1.8 / 3.3 V I AD21

AG21 I 1.8 / 3.3 V RGMII PRG1_RGMII2_RD2 A23 B23 PRG1_RGMII1_RD2 RGMII 1.8 / 3.3 V I AF23

AH23 I 1.8 / 3.3 V RGMII PRG1_RGMII2_RD1 A24 B24 PRG1_RGMII1_RD1 RGMII 1.8 / 3.3 V I AG24

AH24 I 1.8 / 3.3 V RGMII PRG1_RGMII2_RD0 A25 B25 PRG1_RGMII1_RD0 RGMII 1.8 / 3.3 V I AE22

– P 0 V Ground DGND A26 B26 DGND Ground 0 V P –

AE21 I 1.8 / 3.3 V RGMII PRG1_RGMII2_RX_CTL A27 B27 PRG1_RGMII1_RX_CTL RGMII 1.8 / 3.3 V I AG23

AG22 I 1.8 / 3.3 V RGMII PRG1_RGMII2_RXC A28 B28 PRG1_RGMII1_RXC RGMII 1.8 / 3.3 V I AF22

AE19 I/O 1.8 / 3.3 V RGMII PRG1_RGMII2_TXC A29 B29 PRG1_RGMII1_TXC RGMII 1.8 / 3.3 V I/O AD20

AC20 O 1.8 / 3.3 V RGMII PRG1_RGMII2_TX_CTL A30 B30 PRG1_RGMII1_TX_CTL RGMII 1.8 / 3.3 V O AF21

–

P

0 V

Ground

DGND

A31

B31

DGND

Ground

0 V

P

–

AE27 O 1.8 / 3.3 V RGMII PRG0_RGMII2_TD3 A32 B32 PRG0_RGMII1_TD3 RGMII 1.8 / 3.3 V O AA24

AD24 O 1.8 / 3.3 V RGMII PRG0_RGMII2_TD2 A33 B33 PRG0_RGMII1_TD2 RGMII 1.8 / 3.3 V O AD26

AD25 O 1.8 / 3.3 V RGMII PRG0_RGMII2_TD1 A34 B34 PRG0_RGMII1_TD1 RGMII 1.8 / 3.3 V O AC26

AC25 O 1.8 / 3.3 V RGMII PRG0_RGMII2_TD0 A35 B35 PRG0_RGMII1_TD0 RGMII 1.8 / 3.3 V O AD27

– P 0 V Ground DGND A36 B36 DGND Ground 0 V P –

AB26 I 1.8 / 3.3 V RGMII PRG0_RGMII2_RD3 A37 B37 PRG0_RGMII1_RD3 RGMII 1.8 / 3.3 V I AA27

AC27 I 1.8 / 3.3 V RGMII PRG0_RGMII2_RD2 A38 B38 PRG0_RGMII1_RD2 RGMII 1.8 / 3.3 V I W24

AC28 I 1.8 / 3.3 V RGMII PRG0_RGMII2_RD1 A39 B39 PRG0_RGMII1_RD1 RGMII 1.8 / 3.3 V I W25

AB28 I 1.8 / 3.3 V RGMII PRG0_RGMII2_RD0 A40 B40 PRG0_RGMII1_RD0 RGMII 1.8 / 3.3 V I V24

– P 0 V Ground DGND A41 B41 DGND Ground 0 V P –

AA25 I 1.8 / 3.3 V RGMII PRG0_RGMII2_RX_CTL A42 B42 PRG0_RGMII1_RX_CTL RGMII 1.8 / 3.3 V I Y24

AB27 I 1.8 / 3.3 V RGMII PRG0_RGMII2_RXC A43 B43 PRG0_RGMII1_RXC RGMII 1.8 / 3.3 V I Y25

AC24 I/O 1.8 / 3.3 V RGMII PRG0_RGMII2_TXC A44 B44 PRG0_RGMII1_TXC RGMII 1.8 / 3.3 V I/O AD28

AB24 O 1.8 / 3.3 V RGMII PRG0_RGMII2_TX_CTL A45 B45 PRG0_RGMII1_TX_CTL RGMII 1.8 / 3.3 V O AB25

– P 0 V Ground DGND A46 B46 DGND Ground 0 V P –

AH18 O 1.8 / 3.3 V RGMII PRG1_MDIO0_MDC A47 B47 GPIO1_37 GPIO 1.8 / 3.3 V I/O V27

AD18 I/O 1.8 / 3.3 V RGMII PRG1_MDIO0_MDIO A48 B48 PRG0_PRU0_GPO5 GPIO 1.8 / 3.3 V I/O V28

– P 0 V Ground DGND A49 B49 VOUT_DE GPMC 1.8 / 3.3 V O T23

AE15 O 1.8 / 3.3 V RGMII PRG2_MDIO0_MDC A50 B50 VOUT_PCLK GPMC 1.8 / 3.3 V O R24

– P 0 V Ground DGND A51 B51 DGND Ground 0 V P –

AC19 I/O 1.8 / 3.3 V RGMII PRG2_MDIO0_MDIO A52 B52 VOUT_HSYNC GPMC 1.8 / 3.3 V O T24

– P 0 V Ground DGND A53 B53 VOUT_VSYNC GPMC 1.8 / 3.3 V O T25

AE28

O

1.8 / 3.3 V

RGMII

PRG0_MDIO0_MDC

A54

B54

VOUT_DATA23

GPMC

1.8 / 3.3 V

O

R23

AE26 I/O 1.8 / 3.3 V RGMII PRG0_MDIO0_MDIO A55 B55 VOUT_DATA22 GPMC 1.8 / 3.3 V O R26

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 10

3.1.2 Pinout TQMa65xx (continued)

Table 3: Pinout TQMa65xx connector X2 (continued)

AM65xx

Dir. Level Group Signal Pin Signal Group Level Dir. AM65x

– P 0 V Ground DGND A56 B56 VOUT_DATA21 GPMC 1.8 / 3.3 V O P23

AF27 I/O 1.8 / 3.3 V RGMII PRG1_PRU0_GPO5 A57 B57 VOUT_DATA20 GPMC 1.8 / 3.3 V O T28

AF28 I/O 1.8 / 3.3 V GPIO GPIO0_64 A58 B58 VOUT_DATA19 GPMC 1.8 / 3.3 V O U28

AG25 I/O 1.8 / 3.3 V GPIO GPIO0_74 A59 B59 VOUT_DATA18 GPMC 1.8 / 3.3 V O P26

– P 0 V Ground DGND A60 B60 DGND Ground 0 V P –

AH26 I/O 1.8 / 3.3 V GPIO GPIO0_73 A61 B61 VOUT_DATA17 GPMC 1.8 / 3.3 V O P25

AH25

I/O

1.8 / 3.3 V

GPIO

GPIO0_66

A62

B62

VOUT_DATA16

GPMC

1.8 / 3.3 V

O

R28

AG26 I/O 1.8 / 3.3 V GPIO GPIO0_75 A63 B63 VOUT_DATA15 GPMC 1.8 / 3.3 V O R27

AG27 I/O 1.8 / 3.3 V GPIO GPIO0_63 A64 B64 VOUT_DATA14 GPMC 1.8 / 3.3 V O P24

AF25 I/O 1.8 / 3.3 V GPIO GPIO0_85 A65 B65 VOUT_DATA13 GPMC 1.8 / 3.3 V O N25

AF26 I/O 1.8 / 3.3 V GPIO GPIO0_65 A66 B66 VOUT_DATA12 GPMC 1.8 / 3.3 V O N26

AF24 I/O 1.8 / 3.3 V GPIO GPIO0_86 A67 B67 VOUT_DATA11 GPMC 1.8 / 3.3 V O P27

AE24 I/O 1.8 / 3.3 V GPIO GPIO0_84 A68 B68 VOUT_DATA10 GPMC 1.8 / 3.3 V O P28

AE23 I/O 1.8 / 3.3 V GPIO GPIO0_93 A69 B69 VOUT_DATA9 GPMC 1.8 / 3.3 V O M26

– P 0 V Ground DGND A70 B70 DGND Ground 0 V P –

AD22 I/O 1.8 / 3.3 V GPIO GPIO0_94 A71 B71 VOUT_DATA8 GPMC 1.8 / 3.3 V O N23

AD23 I/O 1.8 / 3.3 V GPIO GPIO0_83 A72 B72 VOUT_DATA7 GPMC 1.8 / 3.3 V O M25

AC21 I/O 1.8 / 3.3 V GPIO GPIO0_95 A73 B73 VOUT_DATA6 GPMC 1.8 / 3.3 V O N28

–

P

0 V

Ground

DGND

A74

B74

VOUT_DATA5

GPMC

1.8 / 3.3 V

O

N27

– P 0 V Ground DGND A75 B75 VOUT_DATA4 GPMC 1.8 / 3.3 V O N24

Y26 I/O 1.8 / 3.3 V GPIO GPIO1_67 A76 B76 VOUT_DATA3 GPMC 1.8 / 3.3 V O M24

AA28 I/O 1.8 / 3.3 V GPIO GPIO1_59 A77 B77 VOUT_DATA2 GPMC 1.8 / 3.3 V O M28

Y27 I/O 1.8 / 3.3 V GPIO GPIO1_66 A78 B78 VOUT_DATA1 GPMC 1.8 / 3.3 V O M23

Y28 I/O 1.8 / 3.3 V GPIO GPIO1_58 A79 B79 VOUT_DATA0 GPMC 1.8 / 3.3 V O M27

– P 0 V Ground DGND A80 B80 DGND Ground 0 V P –

W26 I/O 1.8 / 3.3 V GPIO GPIO1_68 A81 B81 DGND Ground 0 V P –

W28 I/O 1.8 / 3.3 V GPIO GPIO1_56 A82 B82 I2C2_SCL I2C 1.8 / 3.3 V I/O/D T27

W27 I/O 1.8 / 3.3 V GPIO GPIO1_57 A83 B83 I2C2_SDA I2C 1.8 / 3.3 V I/O/D R25

V26 I/O 1.8 / 3.3 V GPIO GPIO1_38 A84 B84 DGND Ground 0 V P –

U27 I/O 1.8 / 3.3 V GPIO GPIO1_36 A85 B85 OLDI0_A0P LCD 1.8 V I/O K28

V25

I/O

1.8 / 3.3 V

GPIO

GPIO1_47

A86

B86

OLDI0_A0N

LCD

1.8 V

I/O

J28

U26 I/O 1.8 / 3.3 V GPIO GPIO1_46 A87 B87 DGND Ground 0 V P –

U25 I/O 1.8 / 3.3 V GPIO GPIO1_39 A88 B88 OLDI0_A1P LCD 1.8 V I/O K27

U24 I/O 1.8 / 3.3 V GPIO GPIO1_48 A89 B89 OLDI0_A1N LCD 1.8 V I/O L27

– P 0 V Ground DGND A90 B90 DGND Ground 0 V P –

U23 I/O 1.8 / 3.3 V GPIO PRG0_PRU1_GPO5 A91 B91 DGND Ground 0 V P –

AC22 I/O 1.8 / 3.3 V GPIO PRG1_PRU1_GPO5 A92 B92 OLDI0_A2P LCD 1.8 V I/O J24

A23 I/O 1.8 / 3.3 V GPIO GPIO1_13 A93 B93 OLDI0_A2N LCD 1.8 V I/O K24

B23 I/O 1.8 / 3.3 V GPIO GPIO1_14 A94 B94 DGND Ground 0 V P –

– P 0 V Ground DGND A95 B95 OLDI0_A3P LCD 1.8 V I/O K26

D28 I/O 1.8 / 3.3 V MMC/SD SD_DAT0 A96 B96 OLDI0_A3N LCD 1.8 V I/O J26

E27 I/O 1.8 / 3.3 V MMC/SD SD_DAT1 A97 B97 DGND Ground 0 V P –

D26 I/O 1.8 / 3.3 V MMC/SD SD_DAT2 A98 B98 OLDI0_CLKN LCD 1.8 V I/O L25

D27 I/O 1.8 / 3.3 V MMC/SD SD_DAT3 A99 B99 OLDI0_CLKP LCD 1.8 V I/O K25

– P 0 V Ground DGND A100 B100 DGND Ground 0 V P –

C28 I/O 1.8 / 3.3 V MMC/SD SD_CMD A101 B101 NMI# SYSTEM 1.8 / 3.3 V I F18

C24 I 1.8 / 3.3 V MMC/SD SD_SDWP A102 B102 ECAP0_IN_APWM_OUT PWM 1.8 / 3.3 V I/O D21

B24 I 1.8 / 3.3 V MMC/SD SD_SDCD A103 B103 TIMER_IO1 TIMER 1.8 / 3.3 V I/O C23

C27 O 1.8 / 3.3 V MMC/SD SD_CLK_R A104 B104 TIMER_IO0 TIMER 1.8 / 3.3 V I/O B22

– P 0 V Ground DGND A105 B105 DGND Ground 0 V P –

– P 0 V Ground DGND A106 B106 I2C0_SDA I2C 1.8 / 3.3 V I/O/D C21

A22 I 1.8 / 3.3 V SYSTEM EXT_REFCLK1 A107 B107 I2C0_SCL I2C 1.8 / 3.3 V I/O/D D20

– P 0 V Ground DGND A108 B108 I2C1_SDA I2C 1.8 / 3.3 V I/O/D E21

AD15

O

1.8 V

SYSTEM

OSC1

A109

B109

I2C1_SCL

I2C

1.8 / 3.3 V

I

B21

– P 0 V Ground DGND A110 B110 DGND Ground 0 V P –

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 11

3.1.2 Pinout TQMa65xx (continued)

Table 4: Pinout TQMa65xx connector X3

AM65xx

Dir. Level Group Signal Pin Signal Group Level Dir. AM65x

–

P

0 V

Ground

DGND

A1

B1

DGND

Ground

0 V

P

–

V1

O

1.8 / 3.3 V

XSPI

XSPI_CLK

A2

B2

NC

NC

–

–

–

–

P

0 V

Ground

DGND

A3

B3

NC

NC

–

–

–

R4

O

1.8 / 3.3 V

XSPI

XSPI_CS0

A4

B4

NC

NC

–

–

–

U2

I

1.8 / 3.3 V

XSPI

XSPI_DQS

A5

B5

NC

NC

–

–

–

–

P

0 V

Ground

DGND

A6

B6

DGND

Ground

0 V

P

–

U4

I/O

1.8 / 3.3 V

XSPI

XSPI_DQ0

A7

B7

NC

NC

–

–

–

U5

I/O

1.8 / 3.3 V

XSPI

XSPI_DQ1

A8

B8

NC

NC

–

–

–

T2

I/O

1.8 / 3.3 V

XSPI

XSPI_DQ2

A9

B9

NC

NC

–

–

–

T3

I/O

1.8 / 3.3 V

XSPI

XSPI_DQ3

A10

B10

NC

NC

–

–

–

T4

I/O

1.8 / 3.3 V

XSPI

XSPI_DQ4

A11

B11

NC

NC

–

–

–

T5

I/O

1.8 / 3.3 V

XSPI

XSPI_DQ5

A12

B12

NC

NC

–

–

–

R2

I/O

1.8 / 3.3 V

XSPI

XSPI_DQ6

A13

B13

NC

NC

–

–

–

R3

I/O

1.8 / 3.3 V

XSPI

XSPI_DQ7

A14

B14

NC

NC

–

–

–

R5

O

1.8 / 3.3 V

XSPI

XSPI_CS1

A15

B15

NC

NC

–

–

–

–

P

0 V

Ground

DGND

A16

B16

DGND

Ground

0 V

P

–

U1

O

1.8 / 3.3 V

XSPI

XSPI_LBCLKO

A17

B17

JTAG_EMU1

JTAG

1.8 / 3.3 V

I/O

AA1

–

P

0 V

Ground

DGND

A18

B18

JTAG_EMU0

JTAG

1.8 / 3.3 V

I/O

AA1

–

–

–

NC

NC

A19

B19

JTAG_TRST#

JTAG

1.8 / 3.3 V

I

AA3

–

–

–

NC

NC

A20

B20

DGND

Ground

0 V

P

–

–

–

–

NC

NC

A21

B21

JTAG_TCK

JTAG

1.8 / 3.3 V

I

AA4

–

–

–

NC

NC

A22

B22

DGND

Ground

0 V

P

–

–

–

–

NC

NC

A23

B23

JTAG_TDO

JTAG

1.8 / 3.3 V

O/Z

A20

–

–

–

NC

NC

A24

B24

JTAG_TMS

JTAG

1.8 / 3.3 V

I

A21

–

–

–

NC

NC

A25

B25

JTAG_TDI

JTAG

1.8 / 3.3 V

I

C20

–

P

0 V

Ground

DGND

A26

B26

DGND

Ground

0 V

P

–

–

–

–

NC

NC

A27

B27

SE_ISO_7816_IO1

SECURITY

3.3 V

I/O

–

–

–

–

NC

NC

A28

B28

SE_ISO_7816_IO2

SECURITY

3.3 V

I/O

–

–

–

–

NC

NC

A29

B29

SE_ISO_14443_LA

SECURITY

–

I/O

–

–

–

–

NC

NC

A30

B30

SE_ISO_14443_LB

SECURITY

–

I/O

–

–

–

–

NC

NC

A31

B31

SE_ISO_7816_RST#

SECURITY

3.3 V

I

–

–

–

–

NC

NC

A32

B32

DGND

Ground

0 V

P

–

–

–

–

NC

NC

A33

B33

SE_ISO_7816_CLK

SECURITY

3.3 V

I

–

–

–

–

NC

NC

A34

B34

DGND

Ground

0 V

P

–

–

P

0 V

Ground

DGND

A35

B35

DGND

Ground

0 V

P

–

B25

O

1.8 / 3.3 V

MMC/SD

eMMC_CLK

A36

B36

NC

NC

–

–

–

–

P

0 V

Ground

DGND

A37

B37

NC

NC

–

–

–

B27

O

1.8 / 3.3 V

MMC/SD

eMMC_CMD

A38

B38

NC

NC

–

–

–

C25

I

1.8 / 3.3 V

MMC/SD

eMMC_DS

A39

B39

NC

NC

–

–

–

A26

I/O

1.8 / 3.3 V

MMC/SD

eMMC_DAT0

A40

B40

NC

NC

–

–

–

E25

I/O

1.8 / 3.3 V

MMC/SD

eMMC_DAT1

A41

B41

DGND

Ground

0 V

P

–

C26

I/O

1.8 / 3.3 V

MMC/SD

eMMC_DAT2

A42

B42

DGND

Ground

0 V

P

–

A25

I/O

1.8 / 3.3 V

MMC/SD

eMMC_DAT3

A43

B43

CSI0_RXN4

CSI

1.8 V

I

G24

E24

I/O

1.8 / 3.3 V

MMC/SD

eMMC_DAT4

A44

B44

CSI0_RXP4

CSI

1.8 V

I

F24

–

P

0 V

Ground

DGND

A45

B45

DGND

Ground

0 V

P

–

B24

I/O

1.8 / 3.3 V

MMC/SD

eMMC_DAT5

A46

B46

CSI0_RXN3

CSI

1.8 V

I

H25

B26

I/O

1.8 / 3.3 V

MMC/SD

eMMC_DAT6

A47

B47

CSI0_RXP3

CSI

1.8 V

I

G25

D25

I/O

1.8 / 3.3 V

MMC/SD

eMMC_DAT7

A48

B48

DGND

Ground

0 V

P

–

–

P

0 V

Ground

DGND

A49

B49

CSI0_RXN2

CSI

1.8 V

I

F26

–

–

–

NC

NC

A50

B50

CSI0_RXP2

CSI

1.8 V

I

G26

–

–

–

NC

NC

A51

B51

DGND

CSI

0 V

P

–

–

–

–

NC

NC

A52

B52

CSI0_RXN1

CSI

1.8 V

I

H27

–

–

–

NC

NC

A53

B53

CSI0_RXP1

CSI

1.8 V

I

G27

–

–

–

NC

NC

A54

B54

DGND

Ground

0 V

P

–

–

P

0 V

Ground

DGND

A55

B55

DGND

Ground

0 V

P

–

–

–

–

NC

NC

A56

B56

CSI0_RXN0

CSI

1.8 V

I

G28

–

–

–

NC

NC

A57

B57

CSI0_RXP0

CSI

1.8 V

I

F28

–

–

–

NC

NC

A58

B58

DGND

Ground

0 V

P

–

–

–

–

NC

NC

A59

B59

DGND

Ground

0 V

P

–

–

P

0 V

Ground

DGND

A60

B60

DGND

Ground

0 V

P

–

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 12

3.2

System components

3.2.1 AM65xx CPU

Depending on the TQMa65xx version, one of the following AM65xx derivatives is assembled:

•AM6526

•AM6527

•AM6528

•AM6546

•AM6548

Attention: Destruction or malfunction, AM65xx errata

Please take note of the current AM65xx errata (3).

Attention: MMCSD peripherals, no HS400 mode

MMCSD peripherals do not support the Multimedia Card HS400 mode.

Please take note of the current AM65xx errata (3).

3.2.1.1 Boot Mode

The Boot Mode configuration of the AM65xx is selected via boot strapping pins when the reset is released.

At this time the correct levels must be applied to the corresponding AM65XX pins to ensure the desired configuration.

More information about boot interfaces and its configuration is to be taken from the AM65xx Data Sheet (1) and the AM65xx

Reference Manual (2).

Standard boot devices are, e.g. the eMMC or the QSPI NOR flash on the TQMa65xx, or an SD card on the carrier board.

The boot configuration pins are multiplexed. For this reason, tri-state buffers should be used for other usage of these pins.

Note: Field software updates

When designing a carrier board, it is recommended to have a redundant update concept for field

software updates.

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 13

3.2.1.2 MCU Boot Mode Selection

The MCU_BOOTMODE[9:0] pins have to be configured on the carrier board (e.g., MBa65xx).

Table 5: MCU_BOOTMODE Pin Mapping

9 8 7 6 5 4 3 2 1 0

1.8 V

MMC/SD POST 1Reserved 2Ref Clock

Table 6: PLL Reference Clock Selection

MCU_BOOTMODE Pins Ref Clock (MHz)

2 1 0

0 0 0 19.2

0 0 1 20

0 1 0 24

0 1 1 25

1 0 0 26

1 0 1 27

1 1 0 Reserved

1 1 1 No PLL configuration (slow speed backup)

Table 7: POST Selection

MCU_BOOTMODE Pins POST Select

8 7 6 5

0 0 0 0 POST bypass

X X X 1 Enable POST DMSC, MCU LBIST Parallel

X X 1 X POST DMSC LBIST Enable

X 1 X X POST MCU LBIST Enable

1 X X X POST PBIST Enable

Table 8: 1.8V LDO Configuration

MCU_BOOTMODE Pin 1.8V MMC/SD

9

0 MMCSD0 connected to 1.8V LDO

1 MMCSD1 connected to 1.8V LDO

1: Only on safety-enabled devices. Refer to device Datasheet for device nomenclature.

2: Always set to 0s (via pulldowns to VSS).

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 14

3.2.1.3 Boot Mode pin mapping

In normal boot operation the ROM execution is directed through the main BOOTMODE[18:0] pins.

Table 9: BOOTMODE Pin Mapping

18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Backup Config Primary Config Min Backup Mode Primary Mode

Table 10: Primary Boot Mode Selection

BOOTMODE Pins

Primary Boot Mode Selected

3 2 1 0

0 0 0 0 Sleep (No boot – debug mode)

0 0 0 1 OSPI

0 0 1 0 QSPI

0 0 1 1 Hyperflash

0 1 0 0 SPI (on QSPI/OSPI port 0 in legacy SPI mode)

0 1 0 1 I2C

0 1 1 0 MMC/SD card, eMMC boot from UDA or file system

0 1 1 1 Ethernet

1 0 0 0 USB

1 0 0 1 PCIe

1 0 1 0 UART

1 0 1 1 Reserved

1 1 0 0 GPMC NOR

1 1 0 1 eMMC boot from boot partition (with auto-fall back to file system)

1 1 1 0 Reserved (acts as Sleep)

1 1 1 1 Reserved (acts as Sleep)

Table 11: Backup Mode Selection

BOOTMODE Pins Backup Boot Mode Selected

6 5 4

0 0 0 None (no backup boot will be attempted)

0 0 1 USB

0 1 0 UART

0 1 1 Ethernet

1 0 0 MMC/SD

1 0 1 SPI (on OSPI port 0 in legacy SPI mode)

1 1 0 Hyperflash

1 1 1 I2C

Preliminary User's Manual l TQMa65xx UM 0001 l © 2021, TQ-Systems GmbH Page 15

3.2.1.3 Boot Mode pin mapping (continued)

Table 12: Min Pin Configuration

BOOTMODE Pin

Min Pin Configuration

7

0 All boot mode pins must be properly set

1 Certain boot mode pins are don't cares. ROM code uses built-in values instead.

Table 13: Primary Boot Mode Configuration

BOOTMODE Pins 3

Boot Mode Description

15

14

13

12

11

10

9

8

3 – 0

0000 Sleep Boot not attempted

Pin Cmd Iclk Csel Speed Addr

Width 0001 OSPI –

Port Pin

Cmd Iclk Csel Speed Addr

Width 0010 QSPI –

ns Csel Speed 0011 Hyperflash –

Port Mode Csel Read

Cmd Addr Width 0100 SPI –

Bus Reset Mode Speed Addr 0101 I2C –

Volt Port Interface Config 1bit 0110 MMC/SD –

Clken Clkf Interface Speed Duplex Extern conf 0111 Ethernet –

Mode Port 1000 USB –

Port Dual Sref 1001 PCIe –

1010 UART –

Base A/D mux Csel Size Csel Bus

Width 1100 GPMC NOR –

Port Alt Bus Width Speed Ack 1101 eMMC –

Table 14: Backup Boot Mode Configuration

BOOTMODE Pins 3

Backup Boot Mode Description

18

17

16

6 – 4

000 None No backup boot performed

Mode Port 001 USB –

010 UART –

Clkout Interface 011 Ethernet –

Volt Port 1bit 100 MMC/SD –

Port Addr Width/Cmd 101 SPI –

Csel Speed 110 Hyperflash –

Bus Reset Mode Addr 111 I2C –

3: Shaded cells are don’t cares and pins can take any value.

Table of contents

Other TQ Carrier Board manuals