Doc. No: Unex-QSG-21-003

2/23

A printed version of this document is an uncontrolled copy

© 2021 Unex Technology Corporation – Company Confidential

TABLE OF CONTENTS

1. Objective...................................................................................................4

2. Reference .................................................................................................4

3. Limited Warranty Policy ............................................................................4

4. Safety Guidelines......................................................................................5

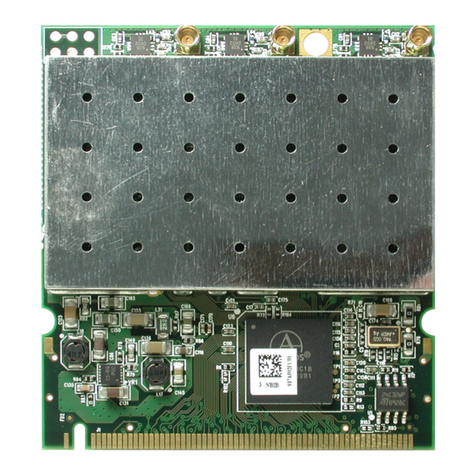

5. Product Appearance .................................................................................5

6. Functional Block Diagram.........................................................................6

7. Electrical Characteristics ..........................................................................7

7.1. Absolute Maximum Ratings .................................................................................. 7

7.2. Recommended Operating Conditions................................................................... 7

7.3. Power Consumption.............................................................................................. 8

8. I/O Interfaces ............................................................................................9

8.1. Antenna Connectors ............................................................................................. 9

8.2. Mini PCIe Card Pinout..........................................................................................11

8.3. I/O Cable Pinout.................................................................................................. 12

8.4. DIP Switch........................................................................................................... 13

9. Design-in Guidelines...............................................................................15

9.1. Power Line Traces .............................................................................................. 15

9.2. Power Sequence................................................................................................. 15

9.3. Brown Out ........................................................................................................... 16

9.4. Grounding ........................................................................................................... 16

9.5. USB Data Lines................................................................................................... 16

9.6. Serial Port ........................................................................................................... 17

9.7. Reset ................................................................................................................... 17

9.8. 1PPS ................................................................................................................... 17

9.9. Tamper Detection (Optional) ............................................................................... 19

9.9.1. Production Mode................................................................................... 20

9.9.2. Test Mode ............................................................................................. 20

9.10. Thermal Management ......................................................................................... 20

10. Dimensions and Weight ..........................................................................21

10.1. Component Keep Out Area ................................................................................. 22

11. Software Settings....................................................................................23

11.1. Verifying the Integration with a Host System ...................................................... 23

11.1.1. Linux ..................................................................................................... 23

LIST OF FIGURES