VMIC VMIVME-7487A User manual

-~

ARTISAN

®

~I

TECHNOLOGY

GROUP

Your definitive source

for

quality

pre-owned

equipment.

Artisan Technology

Group

Full-service,

independent

repair

center

with

experienced

engineers

and

technicians

on staff.

We

buy

your

excess,

underutilized,

and

idle

equipment

along

with

credit

for

buybacks

and

trade-ins

.

Custom

engineering

so

your

equipment

works

exactly as

you

specify.

•

Critical

and

expedited

services

•

Leasing

/

Rentals/

Demos

• In

stock/

Ready-to-ship

•

!TAR-certified

secure

asset

solutions

Expert

team

ITrust

guarantee

I

100%

satisfaction

All

tr

ademarks,

br

a

nd

names, a

nd

br

a

nd

s a

pp

earing here

in

are

th

e property of

th

e

ir

r

es

pecti

ve

ow

ner

s.

Find the Abaco Systems / VMIC VMIVME-7487-222 at our website: Click HERE

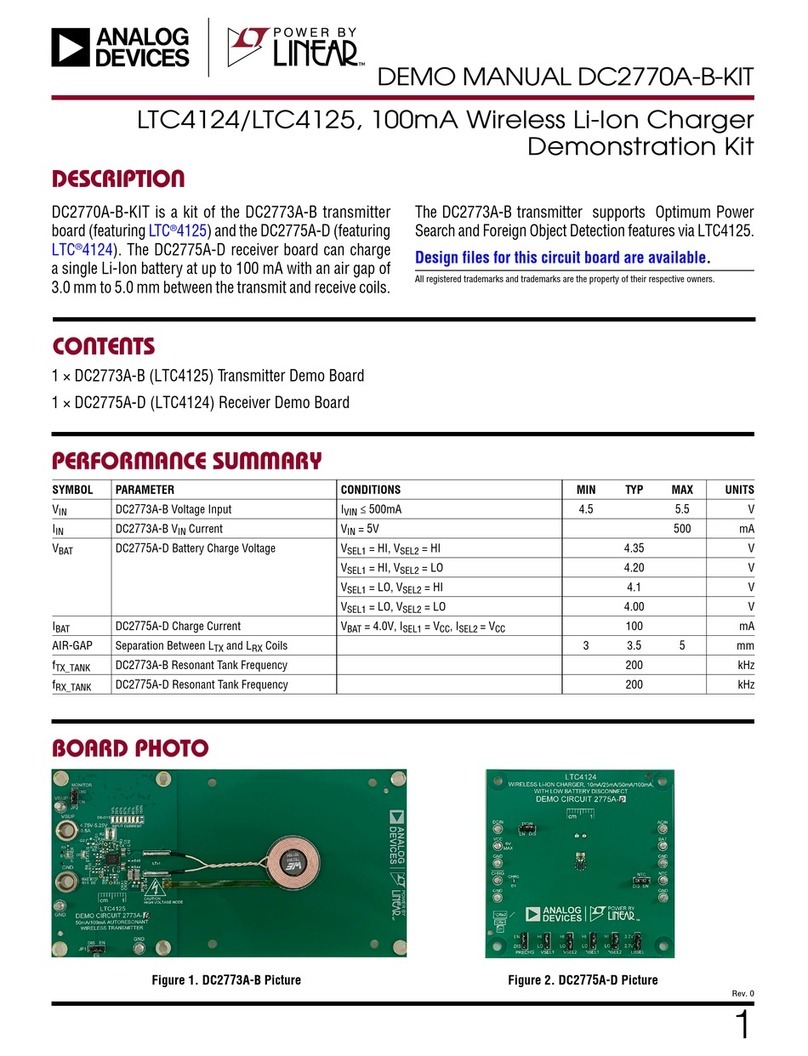

VMIVME-7487A

486 PC/ATVMEbus CPUWITH

DUAL-PORT MEMORY, PC/104,

AND CACHE

PRODUCT MANUAL

DOCUMENT NO. 500-107487-000 C

Revised July 21, 1997

VME MICROSYSTEMS INTERNATIONAL CORPORATION

12090 SOUTH MEMORIAL PARKWAY

HUNTSVILLE, AL 35803-3308

(205) 880-0444

(800) 322-3616

FAX NO.: (205) 882-0859

COPYRIGHT AND TRADEMARKS

© Copyright January 1996.The information in this document has been carefully checked and is believed

to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of

this manual,VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use

of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC’s products to improve

reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described

herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC’s Standard Conditions of Sale.

AMXbus

, BITMODULE

, COSMODULE

, DMAbus

, IOWorks

, IOWorks Access

, IOWorks

Foundation

, IOWorks man figure™, IOWorks Manager™, IOWorks Server™, MAGICWARE

,

MEGAMODULE

, PLC ACCELERATOR (ACCELERATION)

, Quick Link

, Soft Logic Link

, SRTbus

,

TESTCAL

, “The Next Generation PLC”

, The PLC Connection

, TURBOMODULE

, UCLIO

, UIOD

,

UPLC

, Visual IOWorks

, Visual Soft Logic Control(ler)™,

VMEaccess

,

VMEmanager

,

VMEmonitor

,

VMEnet

, VMEnet II

, and

VMEprobe

are trademarks of VME Microsystems International Corporation.

The I/O man figure, UIOC®

,

the VMIC logo, and

WinUIOC

® are registered trademarks of VME

Microsystems International Corporation.

Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, and XENIX are

registered trademarks and Windows NT is a trademark of Microsoft Corporation.

Pentium is a registered trademark of Intel Corporation.

Other registered trademarks are the property of their respective owners.

VME Microsystems International Corporation

All Rights Reserved

This document shall not be duplicated, nor its contents used for any

purpose, unless granted express written permission from VMIC.

®

UIOC

(VMIC logo)

WinUIOC

(I/O man figure)

(IOWorks man figure)

VMIVME-7487A Error Notification

Because of a recently discovered design flaw in the VIC64 (Cypress

Semiconductor) used to implement the VMEbus interface on the

VMIVME-7487A, VMIC warns users that a malfunction may occur. The

following paragraphs below provide information from Cypress concerning

the conditions that must be present to cause this malfunction.

Cypress Erratum:

The following paragraphs came directly from the 6/13/97 Cypress Erratum (Reference No.95):

Lword and A7-A1 are driven on the VMEbus by a VIC64 slave that is not the addressed slave to the D64

transaction in progress thus corrupting the data of the transaction.The following condition must be met to see

this failure:

1. Defining this misbehaving VIC64 as the “failing slave” and the transaction in which the failure is

noted the “current transaction.”

2. The failing slave was the addressed slave to the transaction immediately preceding the current

transaction.We define this transaction to be the “preceding transaction.”

3. The preceding transaction was a D64 slave read from the failing slave.

4. The current transaction must be a D64 transaction.

5. The preceding transaction exhibits a local “read ahead” cycle which extends (local PAS+ signal is

asserted) beyond the address broadcast phase (first VMEbus DS1/0 deassertion after AS*

assertion) of the current transaction.

Work around, Hardware:

PAS* must be deasserted before DSB (later deassertion of either DS1/0) of the address broadcast cycle of

the current transaction deasserts.

VMIC’s Response:

These conditions may arise if:

1. You have more than one device that may be slave to 64-bit block transfers and at least one has a

VIC64 chip.

2. Block transfer master(s) can reassert AS* and execute a BLT 64 Address Broadcast quickly (less

than about 100 ns AS* hightime).

The VIC64 as used on the VMIVME-7487A does not cause trouble during Master Mode. In other words, the

VMIVME-7487A can safely do master BLT 64 transactions under all conditions. The described malfunction

only occurs when the VIC64 is a BLT 64

slave

(read

from/by

master)

and

the slave transaction is rapidly

followed by

another

BLT 64 slave transaction

to

another slave.

RECORD OF REVISIONS

REVISION

LETTER DATE PAGES INVOLVED CHANGE NUMBER

VME MICROSYSTEMS INT’L CORP.

12090 South Memorial Parkway

Huntsville, AL 35803-3308 • (205) 880-0444

REV LTR PAGE NO.

iii

DOC. NO. 500-107487-000

C

A 01/25/96 Release 96-0110

B 05/01/96 Cover and Page ii 96-0313

C 07/21/97 Cover and Page iii 97-0538

iv

VMIC

SAFETY SUMMARY

THE FOLLOWING GENERAL SAFETY PRECAUTIONS MUST BE OBSERVED DURING ALL PHASES

OF THE OPERATION, SERVICE, AND REPAIR OF THIS PRODUCT. FAILURE TO COMPLY WITH

THESE PRECAUTIONS OR WITH SPECIFIC WARNINGS ELSEWHERE IN THIS MANUAL VIOLATES

SAFETY STANDARDS OF DESIGN, MANUFACTURE, AND INTENDED USE OFTHIS PRODUCT. VME

MICROSYSTEMS INTERNATIONAL CORPORATION ASSUMES NO LIABILITY FOR THE

CUSTOMER'S FAILURETO COMPLY WITHTHESE REQUIREMENTS.

GROUNDTHE SYSTEM

To minimize shock hazard, the chassis and system cabinet must be connected to an

electrical ground. A three-conductor AC power cable should be used. The power cable

must either be plugged into an approved three-contact electrical outlet or used with a

three-contact to two-contact adapter with the grounding wire (green) firmly connected to

an electrical ground (safety ground) at the power outlet.

DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE

Do not operate the system in the presence of flammable gases or fumes. Operation of

any electrical system in such an environment constitutes a definite safety hazard.

KEEP AWAY FROM LIVE CIRCUITS

Operating personnel must not remove product covers. Component replacement and

internal adjustments must be made by qualified maintenance personnel. Do not replace

components with power cable connected. Under certain conditions, dangerous voltages

may exist even with the power cable removed. To avoid injuries, always disconnect

power and discharge circuits before touching them.

DO NOT SERVICE OR ADJUST ALONE

Do not attempt internal service or adjustment unless another person, capable of

rendering first aid and resuscitation, is present.

DO NOT SUBSTITUTE PARTS OR MODIFY SYSTEM

Because of the danger of introducing additional hazards, do not install substitute parts or

perform any unauthorized modification to the product. Return the product to VME

Microsystems International Corporation for service and repair to ensure that safety

features are maintained.

DANGEROUS PROCEDUREWARNINGS

Warnings, such as the example below, precede only potentially dangerous procedures

throughout this manual. Instructions contained in the warnings must be followed.

DANGEROUS VOLTAGES, CAPABLE OF CAUSING DEATH, ARE PRESENT IN THIS SYSTEM. USE

EXTREME CAUTIONWHEN HANDLING,TESTING, AND ADJUSTING.

WARNING

v

SAFETY SYMBOLS

GENERAL DEFINITIONS OF SAFETY SYMBOLS USED IN THIS MANUAL

Instruction manual symbol: the product is marked with this symbol when it

is necessary for the user to refer to the instruction manual in order to

protect against damage to the system.

Indicates dangerous voltage (terminals fed from the interior by voltage

exceeding 1000 volts are so marked).

Protective conductor terminal. For protection against electrical shock in

case of a fault. Used with field wiring terminals to indicate the terminal

which must be connected to ground before operating equipment.

Low-noise or noiseless, clean ground (earth) terminal. Used for a signal

common, as well as providing protection against electrical shock in case of

a fault. Before operating the equipment, terminal marked with this symbol

must be connected to ground in the manner described in the installation

(operation) manual.

Frame or chassis terminal. A connection to the frame (chassis) of the

equipment which normally includes all exposed metal structures.

Alternating current (power line).

Direct current (power line).

Alternating or direct current (power line).

The WARNING sign denotes a hazard. It calls attention to a procedure, a

practice, a condition, or the like, which, if not correctly performed or

adhered to, could result in injury or death to personnel.

The CAUTION sign denotes a hazard. It calls attention to an operating

procedure, a practice, a condition, or the like, which, if not correctly

performed or adhered to, could result in damage to or destruction of part or

all of the system.

The NOTE sign denotes important information. It calls attention to a

procedure, a practice, a condition or the like, which is essential to highlight.

OR

***************

***************

*

*

**

*

*

CAUTION

NOTE:

WARNING

!

OR

TABLE OF CONTENTS

VMIVME-7487A PRODUCT MANUAL

vi

CHAPTER 1 - INTRODUCTION .................................................1-1

SECTION 1 - INTRODUCTION TO THE VMIVME-7487A .....................1-1

SECTION 2 - ABOUT THIS MANUAL ...................................................1-2

SECTION 3 - PRODUCT FAMILY .........................................................1-3

SECTION 4 - REFERENCES .................................................................1-5

SECTION 5 - PC/AT FEATURES ..........................................................1-6

SECTION 6 - VMEbus FEATURES .......................................................1-8

CHAPTER 2 - INSTALLATION AND SETUP ............................2-1

SECTION 1 - INTRODUCTION ..............................................................2-1

SECTION 2 - UNPACKING PROCEDURES .........................................2-2

SECTION 3 - HARDWARE SETUP .......................................................2-3

SECTION 4 - LED STATUS DEFINITION ..............................................2-5

SECTION 5 - INSTALLATION ...............................................................2-5

SECTION 6 - FRONT PANEL CONNECTORS .....................................2-6

SECTION 7 - PC/104 EXPANSION SITE ..............................................2-7

SECTION 8 - BIOS SETUP ....................................................................2-8

SECTION 9 - CONFIGURING OPERATING SYSTEMS .......................2-8

GENERAL RULE REGARDING OPERATING SYSTEMS

...............2-8

CONFIGURATION EXAMPLES

........................................................2-9

Configuring MS-DOS for the VMIVME-7487A

.............................2-9

Configuring Windows for the VMIVME-7487A

.............................2-10

TABLE OF CONTENTS 500-107487-000

vii

VMIVME-7487A PRODUCT MANUA

L

CHAPTER 3 - PC/AT FUNCTIONS 1

SECTION 1 - CPU REGISTER MODEL ................................................3-1

SECTION 2 - PHYSICAL MEMORY ......................................................3-2

SECTION 3 - MEMORY AND PORT MAPS ..........................................3-3

MEMORY MAP

.................................................................................3-3

I/O PORT MAP

..................................................................................3-4

SECTION 4 - PC/AT INTERRUPTS .......................................................3-8

SECTION 5 - ENHANCED I/O PORTS ..................................................3-12

SERIAL PORTS

................................................................................3-13

PARALLEL PORT

.............................................................................3-13

SECTION 6 - VIDEO GRAPHICS ADAPTER ........................................3-14

SECTION 7 - PC/104 EXPANSION SITE ..............................................3-15

CHAPTER 4 - VMEbus FUNCTIONS ........................................4-1

SECTION 1 - INTRODUCTION ..............................................................4-1

SECTION 2 - VMEbus INTERFACE ......................................................4-2

VMEbus Interface Overview

..............................................................4-2

VMEbus Interface Hardware

.............................................................4-3

Programming the VMEbus Interface

.................................................4-6

SECTION 3 - VMEbus MASTER OPERATION .....................................4-7

Real Mode Access

............................................................................4-8

Protected Mode Access

....................................................................4-10

500-107487-000 TABLEOFCONTENTS

VMIVME-7487A PRODUCT MANUAL

viii

SECTION 4 - VMEbus SLAVE OPERATION ........................................4-13

Interprocessor Communications

........................................................4-13

Dual-Ported DRAM

............................................................................4-18

Slave Access Memory Map

...............................................................4-21

System Considerations

.....................................................................4-23

SECTION 5 - SYSTEM CONTROLLER FUNCTIONS ...........................4-25

SECTION 6 - VMEbus INTERRUPT HANDLING ..................................4-26

Software Interrupts

............................................................................4-30

Interrupt on BERR*

............................................................................4-30

Periodic Timer Interrupt

.....................................................................4-30

Interrupt Processing

..........................................................................4-31

SECTION 7 - VMEbus INTERRUPTER .................................................4-33

SECTION 8 - VMEbus REQUESTER ....................................................4-34

SECTION 9 - READ-MODIFY-WRITE CYCLES ....................................4-34

SECTION 10 - BLOCK TRANSFERS ....................................................4-36

DRAM Refresh Considerations

.........................................................4-36

Master BLT Operation

.......................................................................4-37

Slave BLT Operation

.........................................................................4-38

SECTION 11 - VME64 FUNCTIONS ......................................................4-39

Master VME64 operation

...................................................................4-39

Slave VME64 operation

.....................................................................4-39

TABLE OF CONTENTS 500-107487-000

ix

VMIVME-7487A PRODUCT MANUA

L

SECTION 12 - BYTE ORDERING .........................................................4-40

BYTE SWAPPING

............................................................................4-40

The Byte Swapping Problem Defined

..........................................4-41

Byte Swapping and the VMEbus

.................................................4-42

VMIVME-7487A Byte Swapping Hardware

.................................4-43

Master/Slave Byte Swapping

.......................................................4-45

SECTION 13 - VMIVME-7487A REGISTERS ........................................4-46

REGISTER MAPS

.............................................................................4-46

SYSTEM REGISTER DETAILS

........................................................4-52

General Purpose Command Register

..........................................4-52

Product ID Register

.....................................................................4-55

VIC Base Register

.......................................................................4-55

Extended/Standard Address Register

.........................................4-57

Onboard Video Status Register

...................................................4-57

Rearm Interrupt Register

.............................................................4-57

Slave Address Mask/Compare Registers

....................................4-57

INTERRUPT ACKNOWLEDGE REGISTER DETAILS

.....................4-58

VIC REGISTER DETAILS

.................................................................4-58

VMEbus Interrupter Interrupt Control Register

............................4-59

VMEbus Interrupt Control Registers

............................................4-60

DMA Status Interrupt Control Register

........................................4-61

Local Interrupt Control Registers

.................................................4-62

ICGS Interrupt Control Register

...................................................4-63

ICMS Interrupt Control Register

..................................................4-64

Error Group Interrupt Control Register

........................................4-65

ICGS Interrupt Vector Base Register

...........................................4-66

ICMS Interrupt Vector Base Register

..........................................4-67

Local Interrupt Vector Base Register

...........................................4-68

Error Group Interrupt Vector Base Register

................................4-68

Interprocessor Communications Registers

..................................4-69

VMEbus Interrupt Request/Status Register

.................................4-69

VMEbus Interrupt Vector Base Registers

....................................4-70

Transfer Timeout Register

...........................................................4-70

Local Bus Timing Register

...........................................................4-73

Block Transfer Definition Register

...............................................4-74

500-107487-000 TABLEOFCONTENTS

VMIVME-7487A PRODUCT MANUAL

x

Interface Configuration Register

..................................................4-75

Arbiter/Requester Configuration Register

....................................4-77

Address Modifier Source Register

...............................................4-78

Bus Error Status Register

............................................................4-79

DMA Status Register

...................................................................4-80

Slave Select 0 Control Register 0

................................................4-82

Slave Select 0 Control Register 1

................................................4-84

Slave Select 1 Control Register 0

................................................4-87

Slave Select 1 Control Register 1

................................................4-89

Release Control Register

.............................................................4-92

Block Transfer Control Register

...................................................4-93

Block Transfer Length Registers

..................................................4-95

System Reset Register

................................................................4-96

INTERPROCESSOR COMMUNICATIONS REGISTERS

................4-96

Interprocessor Communications Switch Register

........................4-97

Interprocessor Communication Registers

....................................4-98

VIC Version Register

...................................................................4-98

Reset/Halt Status Register

...........................................................4-98

Mailbox Semaphore Register

.......................................................4-99

Set/Clear ICGS Switch Registers (Slave-Only) ...........................4-101

Set/Clear ICMS Switch Registers (Slave-Only) ...........................4-101

CHAPTER 5 - MAINTENANCE ..................................................M-1

SECTION 1 - MAINTENANCE ...............................................................M-1

SECTION 2 - MAINTENANCE PRINTS .................................................M-1

APPENDIX A - CONNECTOR PINOUTS ..................................A-1

SECTION 1 - INTRODUCTION ..............................................................A-1

SECTION 2 - ETHERNET CONNECTOR PINOUT ...............................A-3

SECTION 3 - FLOPPY DRIVE CONNECTOR PINOUT ........................A-4

SECTION 4 - IDE HARD DRIVE CONNECTOR PINOUT .....................A-5

SECTION 5 - KEYBOARD CONNECTOR PINOUT ..............................A-6

TABLE OF CONTENTS 500-107487-000

xi

VMIVME-7487A PRODUCT MANUA

L

SECTION 6 - PC/104 CONNECTOR PINOUT .......................................A-7

SECTION 7 - PRINTER CONNECTOR PINOUT ...................................A-9

SECTION 8 - SERIAL CONNECTOR PINOUT .....................................A-10

SECTION 9 - VIDEO CONNECTOR PINOUT .......................................A-11

SECTION 10 - VMEbus CONNECTOR PINOUT ..................................A-12

APPENDIX B - ETHERNET OPTION .........................................B-1

SECTION 1 - INTRODUCTION ..............................................................B-1

SECTION 2 - ETHERNET SOFTWARE COMPATIBILITY ...................B-2

SECTION 3 - ETHERNET DRIVER SOFTWARE ..................................B-3

SECTION 4 - ETHERNET DIAGNOSTIC SOFTWARE .........................B-3

SECTION 5 - TECHNICAL DETAILS ....................................................B-5

APPENDIX C - FLASH MEMORY OPTION ...............................C-1

SECTION 1 - INTRODUCTION ..............................................................C-1

SECTION 2 - PREPARING THE FLASH MEMORY ..............................C-2

SECTION 3 - COPYING FILES TO FLASH MEMORY .........................C-3

SECTION 4 - USING FLASH MEMORY AS BOOT DEVICE ................C-4

SECTION 5 - REPROGRAMMING FLASH MEMORY ..........................C-4

SECTION 6 - TECHNICAL DETAILS ....................................................C-5

SECTION 7 - PROGRAMMING .............................................................C-6

500-107487-000 TABLEOFCONTENTS

VMIVME-7487A PRODUCT MANUAL

xii

APPENDIX D - BASIC INPUT OUTPUT SYSTEM ....................D-1

SECTION 1 - INTRODUCTION ..............................................................D-1

SECTION 2 - STANDARD FEATURES .................................................D-1

SECTION 3 - QUICK SETUP .................................................................D-2

SECTION 4 - PROGRAM DESCRIPTION .............................................D-5

USER INTERFACE ...........................................................................D-6

CONTROL KEY SUMMARY .............................................................D-7

SECTION 5 - PROGRAM MENUS AND MENU ITEMS ........................D-8

MAIN MENU ......................................................................................D-8

System Time ................................................................................D-9

System Date ................................................................................D-9

Diskette A:/B: ...............................................................................D-9

Video System ...............................................................................D-9

Large Disk Mode ..........................................................................D-9

System Memory/ Extended Memory ............................................D-9

IDE Adapter 0 Master/IDE Adapter 0 Slave Sub-menus .............D-10

Autotype Fixed Disk .....................................................................D-10

Type .............................................................................................D-11

Cylinders ......................................................................................D-13

Heads ...........................................................................................D-13

Sectors/Track ...............................................................................D-13

Write Precomp .............................................................................D-13

MEMORY CACHE SUB-MENU ........................................................D-14

Internal Cache ..............................................................................D-15

External Cache ............................................................................D-15

Cache Shadow Region ................................................................D-15

Non-Cacheable Region ................................................................D-15

MEMORY SHADOW SUB-MENU .....................................................D-16

System Shadow ...........................................................................D-17

Video Shadow ..............................................................................D-17

TABLE OF CONTENTS 500-107487-000

xiii

VMIVME-7487A PRODUCT MANUA

L

Shadow Memory Regions ............................................................D-17

C800 - CFFF ................................................................................D-18

D000 - DFFF ................................................................................D-18

E000 - EFFF ................................................................................D-18

BOOT OPTIONS SUB-MENU ...........................................................D-18

Keyboard .....................................................................................D-19

Boot Sequence ............................................................................D-19

SETUP Prompt ............................................................................D-20

POST Errors ................................................................................D-20

Floppy Check ...............................................................................D-20

Summary Screen .........................................................................D-20

KEYBOARD FEATURES ..................................................................D-21

NumLock ......................................................................................D-22

Key click .......................................................................................D-22

Keyboard Auto-Repeat Rate ........................................................D-22

Keyboard Auto-Repeat Delay ......................................................D-22

SECTION 6 - EXITING THE PhoenixBIOS ...........................................D-22

EXIT MENU .......................................................................................D-22

Save Changes & Exit ...................................................................D-23

Discard Changes & Exit ...............................................................D-23

Load Default Values ....................................................................D-23

Load Previous Values ..................................................................D-24

Save Changes .............................................................................D-24

SECTION 7 - STATUS AND ERROR MESSAGES ...............................D-24

LIST OF FIGURES

VMIVME-7487A PRODUCT MANUAL

xiv

Figure 1-1 VMIVME-7487A Board View ............................................1-3

Figure 1-2 VMIVME-7487A Partial Block Diagram ..........................1-7

Figure 1-3 VMIVME-7487A VMEbus Functions ...............................1-9

Figure 2-1 I/O Port and Jumper Locations ......................................2-3

Figure 2-2 LED Position on the Front Panel ...................................2-5

Figure 2-3 PC/104 Mechanical Connection .....................................2-7

Figure 3-1 80486 CPU Block Diagram .............................................3-1

Figure 3-2 Connections Between the PC Interrupt Logic

Controller and the VMEbus ............................................3-12

Figure 4-1 VMIVME-7487A VMEbus Functions ...............................4-3

Figure 4-2 VMEbus Interface Block Diagram ..................................4-4

Figure 4-3 VLIC Block Diagram ........................................................4-5

Figure 4-4 Real Mode VMEbus Access ...........................................4-9

Figure 4-5 Protected Mode VMEbus Access ..................................4-12

Figure 4-6 VMEbus Slave Interface ..................................................4-15

Figure 4-7 Slave Compare Operation ..............................................4-17

Figure 4-8 Slave Addressing Detail .................................................4-24

Figure 4-9 Flow Chart for Non-NMI Interrupt Processing

for IRQ11 ..........................................................................4-32

Figure 4-10 Flow Chart for NMI Interrupt Processing ......................4-33

Figure 4-11 Byte Relationships Using the Little-Endian 80486 .......4-41

Figure 4-12 Byte Relationships Using the Big-Endian 68040 .........4-42

Figure 4-13 80486-to-VMEbus Data Byte Lanes ...............................4-44

LIST OF FIGURES 500-107487-000

xv

VMIVME-7487A PRODUCT MANUA

L

Figure A-1 VMIVME-7487A Connector Locations ...........................A-2

Figure A-2 Ethernet Connector Pinout ............................................A-3

Figure A-3 Floppy Drive Connector Pinout .....................................A-4

Figure A-4 IDE Hard Drive Connector Pinout ..................................A-5

Figure A-5 PS/2 Keyboard Connector Pinout .................................A-6

Figure A-6 PC/AT Keyboard Connector Pinout ..............................A-6

Figure A-7 PC/104 Connector Diagram ............................................A-7

Figure A-8 Printer Connector Pinout ...............................................A-9

Figure A-9 Serial Connector Pinouts ...............................................A-10

Figure A-10 Video Connector Pinout .................................................A-11

Figure A-11 VMEbus Connector Diagram .........................................A-12

Figure B-1 Location of the Ethernet Mezzanine ..............................B-2

Figure C-1 Flash Mezzanine Jumper Location ................................C-2

Figure D-1 PhoenixBIOS Opening Display ......................................D-3

Figure D-2 Elements of the PhoenixBIOS User Interface ..............D-6

Figure D-3 PhoenixBIOS Main Menu ................................................D-8

Figure D-4 PhoenixBIOS IDE Adapter Master Sub-menu ..............D-10

Figure D-5 PhoenixBIOS Memory Cache Sub-menu ......................D-14

Figure D-6 PhoenixBIOS Memory Shadow Sub-menu ...................D-17

Figure D-7 PhoenixBIOS Boot Options Sub-menu .........................D-19

Figure D-8 PhoenixBIOS Example Summary Screen .....................D-21

500-107487-000 LISTOFFIGURES

VMIVME-7487A PRODUCT MANUAL

xvi

Figure D-9 PhoenixBIOS Keyboard Features Sub-menu ...............D-21

Figure D-10 PhoenixBIOS Exit Menu .................................................D-23

LIST OFTABLES

xvii

VMIVME-7487A PRODUCT MANUAL

Table 1-1 PC/AT I/O Features ..........................................................1-8

Table 2-1 VMIVME-7487A Jumper Functions and Settings .........2-4

Table 2-2 VMEbus Window Addresses ..........................................2-9

Table 3-1 VMIVME-7487A Memory Map .........................................3-3

Table 3-2 VMIVME-7487A I/O Address Map ...................................3-5

Table 3-3 PC/AT Hardware Interrupts ............................................3-8

Table 3-4 PC/AT Interrupt Vector Table .........................................3-9

Table 3-5 Parallel Port Modes .........................................................3-13

Table 3-6 Common Supported Graphics Video Resolutions .......3-14

Table 4-1 Protected Mode VMEbus Address Modifiers ................4-11

Table 4-2 Slave Access Memory Map ............................................4-22

Table 4-3 Interrupt Priorities ...........................................................4-26

Table 4-4 Interrupt Level Assignments ..........................................4-28

Table 4-5 VMEbus Byte Assignment to the Data Lines ................4-40

Table 4-6 Byte Swap Modes ............................................................4-44

Table 4-7 System Register Map ......................................................4-47

Table 4-8 VIC Register Map .............................................................4-48

Table 4-9 Slave Access Register Map ............................................4-51

Table A-1 PC/104 Connector Pinout ...............................................A-7

Table A-2 VMEbus Connector Pinout .............................................A-12

Table B-1 Boot EPROM Address Selection ...................................B-6

Table D-1 PhoenixBIOS Setup Keystroke Actions ........................D-7

500-107487-000 LISTOFTABLES

VMIVME-7487A PRODUCT MANUAL

xviii

Table D-2 PhoenixBIOS Fixed Disk Table ......................................D-12

Table D-3 PhoenixBIOS Status and Error Messages ....................D-25

Table of contents

Other VMIC Computer Hardware manuals

Popular Computer Hardware manuals by other brands

ASROCK

ASROCK athena A1 Kit Quick installation guide

Freescale Semiconductor

Freescale Semiconductor MC68HC08KH12 datasheet

ICP

ICP Chapter C Quick setup guide

Linear Technology

Linear Technology Analog Devices DC2773A-B manual

Uctronics

Uctronics U6184 Assembly guide

Connectland

Connectland Front panel I/O Box user manual