WM8750-EV1M

w Rev 2.0, February 2005

2

TABLE OF CONTENTS

TABLE OF CONTENTS .................................................................................. 2

INTRODUCTION ............................................................................................. 4

GETTING STARTED ....................................................................................... 4

EVALUATION BOARD CHECKLIST ...................................................................... 4

CUSTOMER REQUIREMENTS.............................................................................. 4

POWER SUPPLIES ............................................................................................... 5

BOARD FUNCTIONALITY ..................................................................................... 5

BOARD INPUT ....................................................................................................... 6

BOARD OUTPUT ................................................................................................... 6

INTERFACES......................................................................................................... 7

HEADERS .............................................................................................................. 7

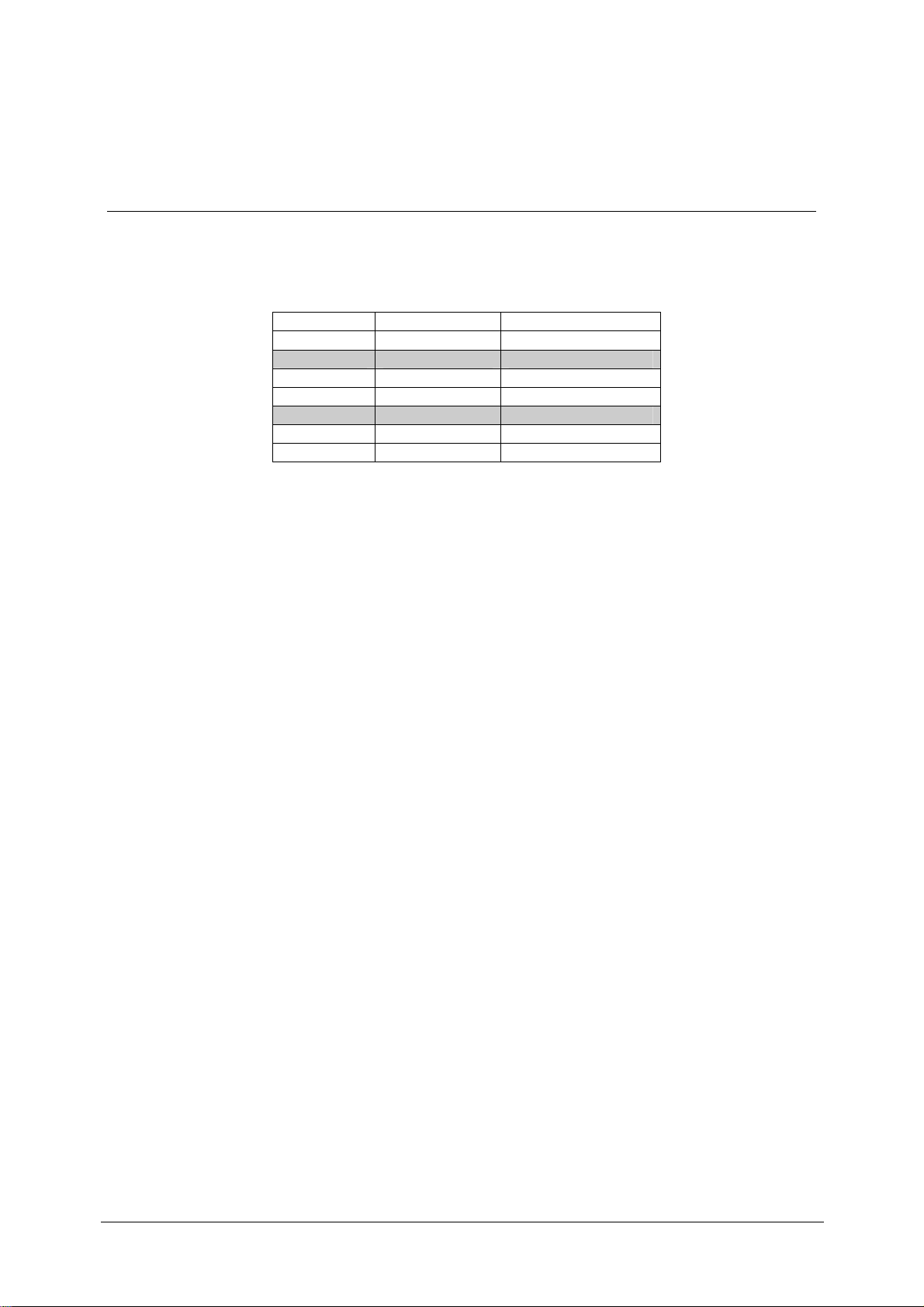

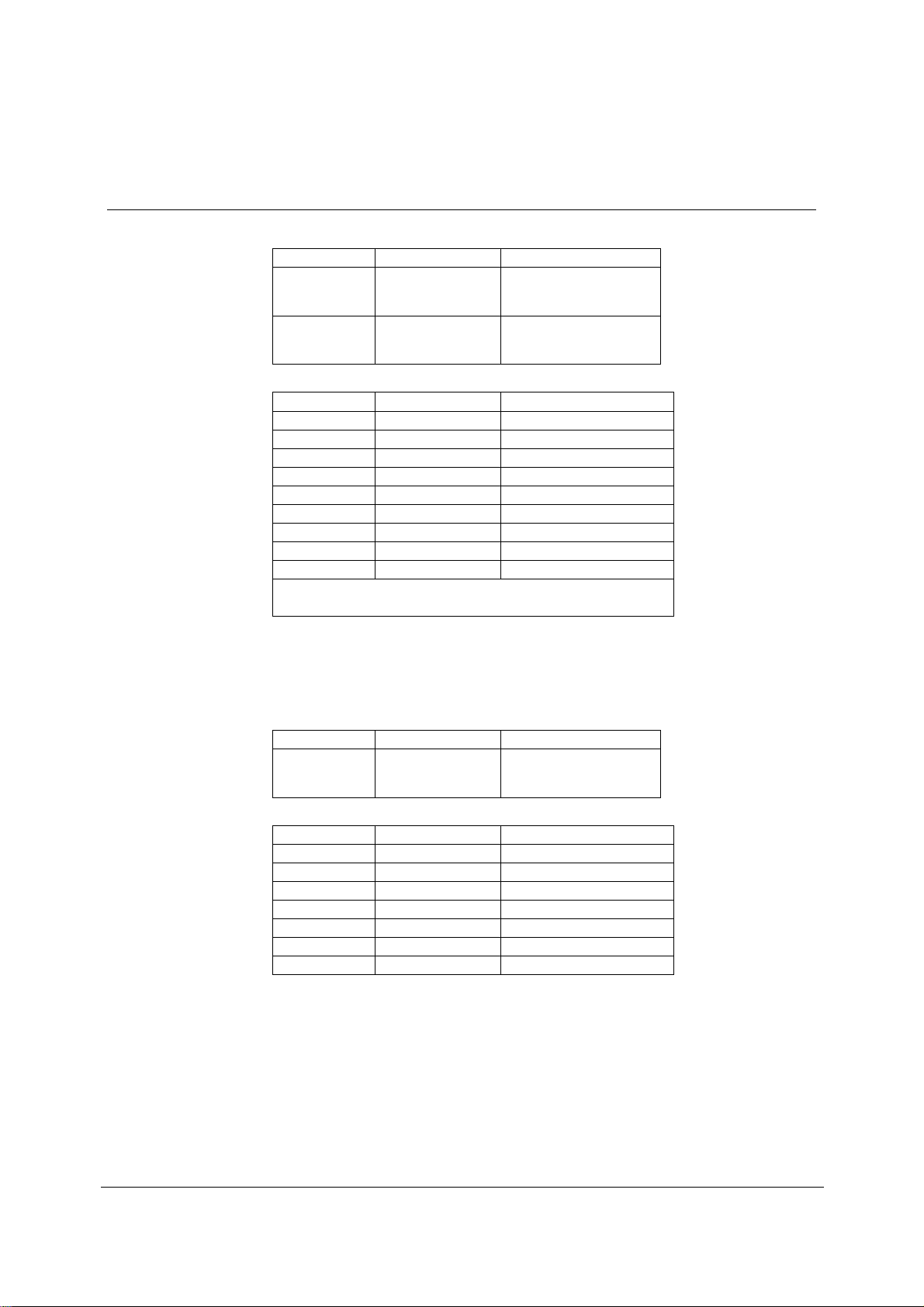

LINKS, JUMPERS AND SWITCHES ...................................................................... 9

WM8750 OPERATION .................................................................................. 10

SOFTWARE CONTROL....................................................................................... 10

SERIAL INTERFACE SOFTWARE DESCRIPTION...................................... 13

SOFTWARE DOWNLOAD................................................................................... 13

SOFTWARE INSTALLATION............................................................................... 13

SOFTWARE OPERATION ................................................................................... 13

POWER DOWN AND INTERFACE CONTROL.................................................... 19

DAC AND ADC CONTROL................................................................................... 20

VOLUME CONTROL ............................................................................................ 21

MIXER CONTROL................................................................................................ 22

TONE CONTROL ................................................................................................. 23

SCHEMATIC LAYOUT .................................................................................. 24

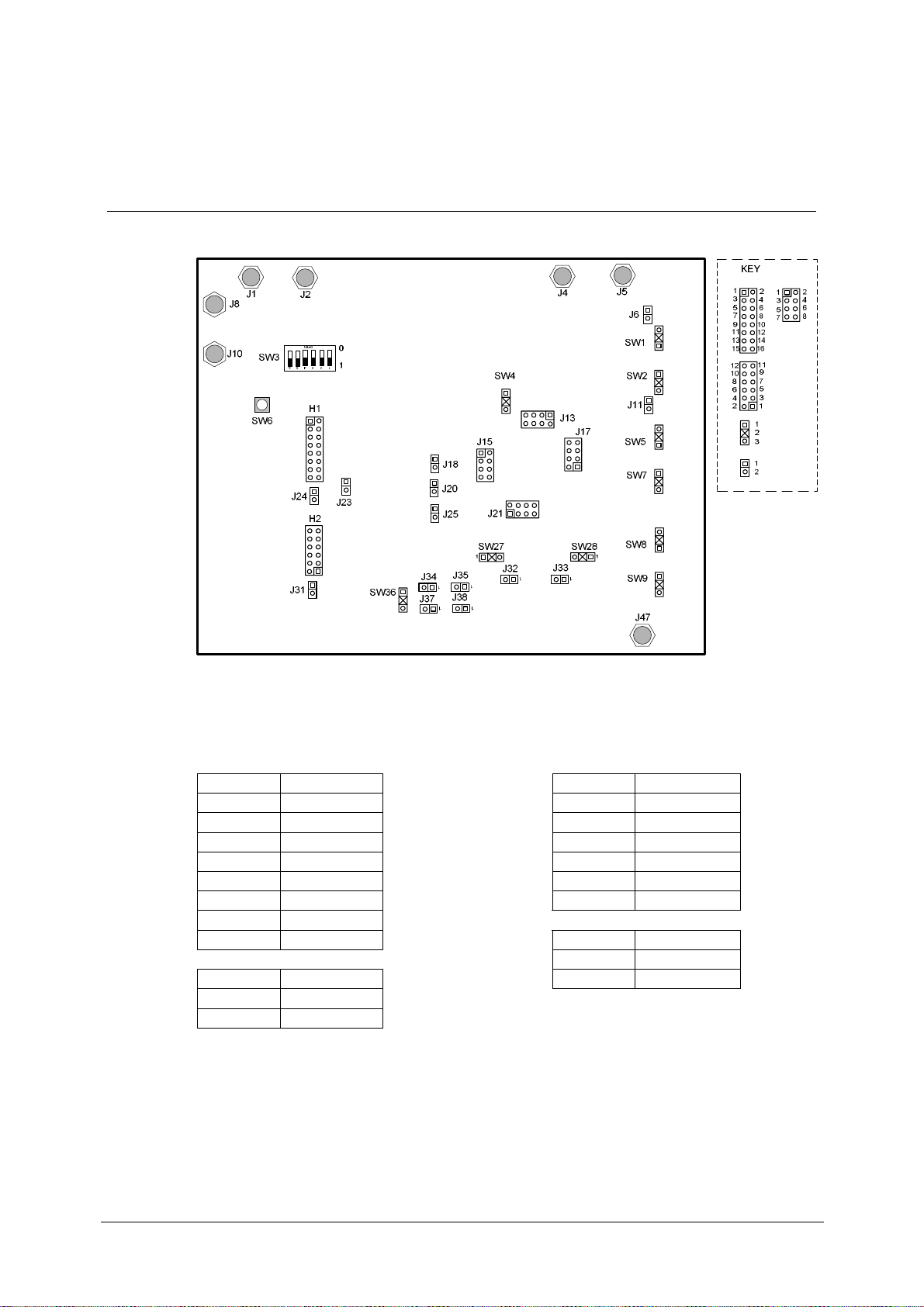

WM8750-EV1B PCB LAYOUT...................................................................... 32

WM8750-EV1B BILL OF MATERIAL............................................................ 36

APPENDIX .................................................................................................... 38

EXTERNAL DSP CONNECTION TO THE WM8750-EV1B .......................... 38

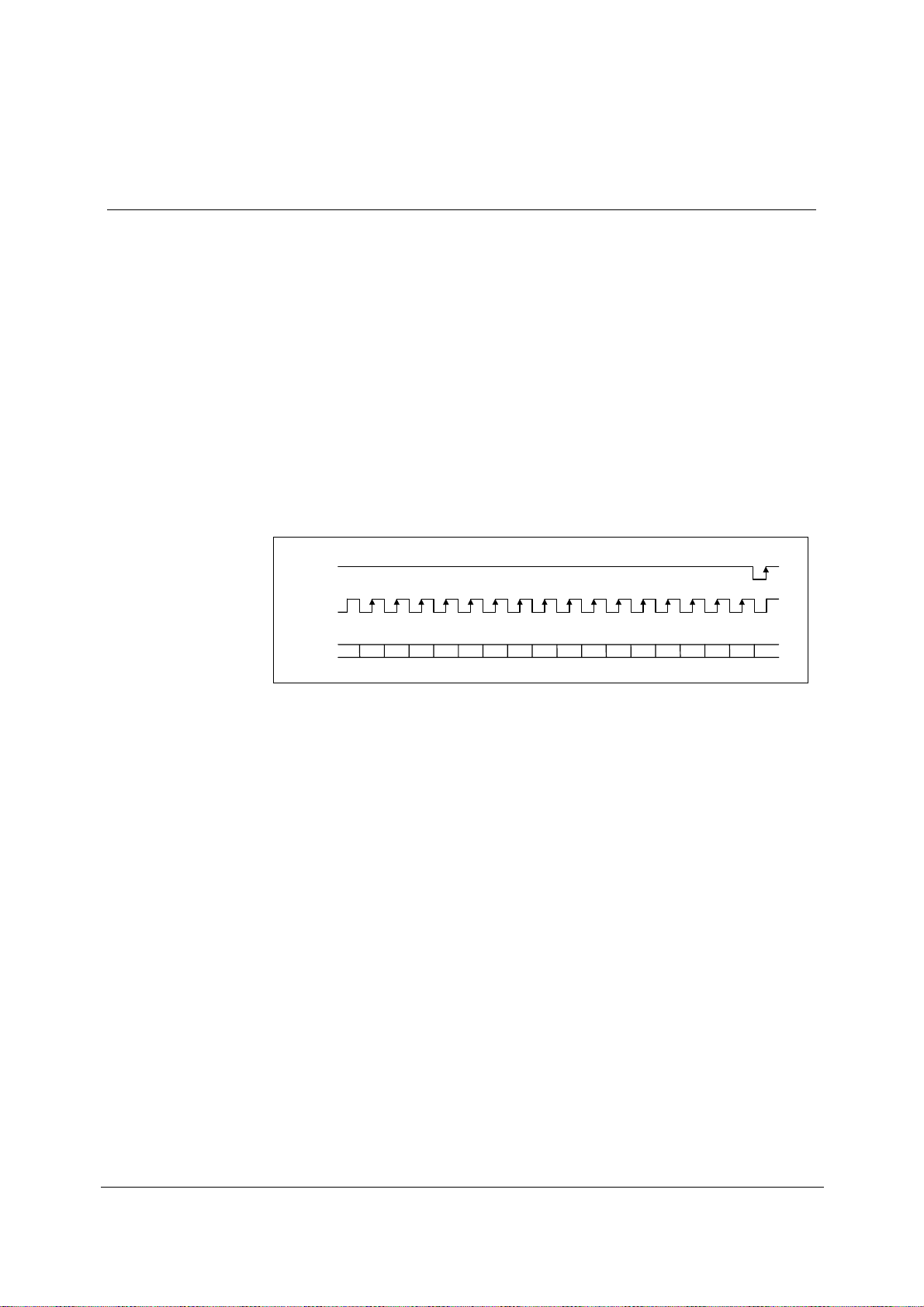

AUDIO INTERFACE CONNECTIONS.................................................................. 38

SOFTWARE INTERFACE.................................................................................... 40

CONNECTION DIAGRAMS.................................................................................. 40

ADDITIONAL WM8750-EV1B SETUP RECOMMENDATIONS.................... 42

ADC TO DAC LOOPBACK................................................................................... 42

CONNECTION OF AN 8ΩMONO SPEAKER ...................................................... 44

HEADPHONE AUTO-DETECT FUNCTION ......................................................... 46